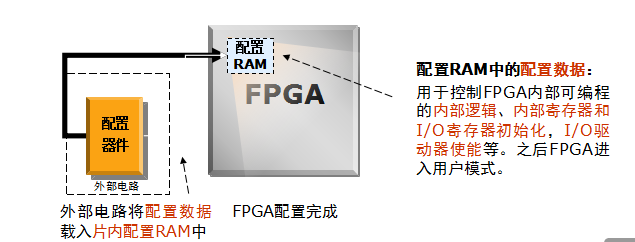

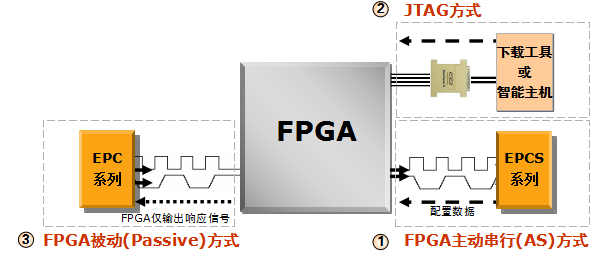

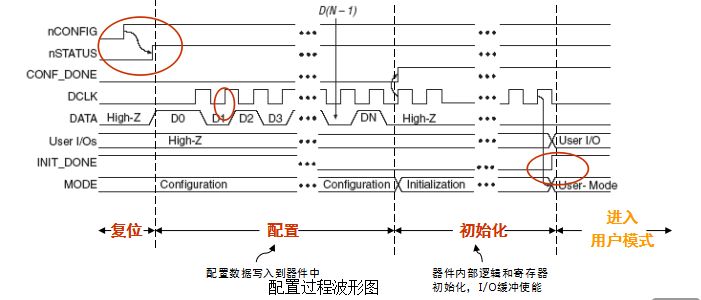

等。 配置( configuration )是对FPGA的内容进行编程的过程。每次上电后都需要进行配置是基于SRAM工艺FPGA的一个特点,也可以说是一个缺点。FPGA配置过程如下:

2022-12-26 18:10:00 1780

1780 目前我公司开发的产品以28335为主控芯片,但在实际使用过程中,发现经常有一些板卡上电后不工作,人为按复位按钮后,工作又正常,检查3.3V电源与1.9V电源电压也都正常,电源芯片使用的是TPS767D301,两路电源是同时上电,无延时,上电顺序满足28335上电要求,请问是什么方面的问题?

2020-05-20 08:24:33

FPGA在上电完成整个配置流程之后进入到用户模式。用户模式是在完成了用户合计的数字逻辑在FPGA片上的搭建之后,开始运行该逻辑电路从而相应的功能。转自《电子技术应用》

2016-10-02 20:20:32

`FPGA 上电配置时候IO口会有一个短暂的3.3V 10ms 的电平,导致我控制端出现问题,我想问下如何可以避免这个电平`

2020-11-23 10:31:40

的过程优势:简单的说,它就相当于一张白纸,把需要做的东西全部自己做出来,自由度最高。理论上FPGA可以配置成任何需要的处理器。一般用于通信类的行业。难点: 开发难度高,门槛也比较高。对数电模电的...

2022-02-09 06:14:56

FPGA上电瞬间IO管脚输出的高电平怎么消除呢?

2023-04-23 14:48:08

下面给大家介绍FPGA LUT的结构

2018-07-09 04:57:10

FPGA与6678调试SRIO通信过程中,如DSP修改后重新编译LOAD后,FPGA方无反应,需要断电再上电才能通信正常,请问可能是什么原因,根据论坛例程改编的DSP程序。。。

2018-08-07 07:28:46

FPGA入门知识介绍近几年来,由于现场可编程门阵列(FPGA)的使用非常灵活,又可以无限次的编程,已受到越来越多的电子编程者的喜爱,很多朋友都想学习一些FPGA入门知识准备进行这个行业,现在关于

2014-08-16 10:32:45

FPGA在软件无线电中的应用本文结合各种实际测试介绍了罗德与施瓦茨公司的手持式频谱仪R&S FSH在发射机与天馈线测试、无线电干扰查处以及电磁兼容诊断测试中的应用。

2012-08-12 11:55:19

Flash进行上电加载,在系统上电稳定后,FPGA器件首先需要足够的时间用于配置加载操作,只有在这个过程结束之后,FPGA器件才能够进入正常的用户运行模式。而上电复位延时过短,等同于FPGA器件根本

2019-04-12 06:35:31

的。除此之外,FPGA与传统的开发是有很大区别的,FPGA开发的是硬件,需要对底层有深刻的了解,学习的过程也是很困难的,在这里分享几点我的学习经验。1、对于任何一门学问,并不是您有了所有知识储备才开始,而是

2019-10-14 10:08:35

本文以Altera公司的FPGA为目标器件,通过开发实例介绍FPGA开发的完整的流程及开发过程中使用到的开发工具,包括QuartusII、FPGA CompilerII、Modelsim,并重点解说如何使用这三个工具进行协同设计。

2021-04-29 06:04:13

FPGA为了简化BOM成本(如安路半导体)不需要用户特别关注上电时序,用单电源供电,芯片内部控制上电时序。虽然不合理的上电时序有时候也能让FPGA正常工作,但不正常的上电或掉电过程有可能会造成瞬时电流

2019-07-18 14:26:01

FPGA程序写完编译已用94%的资源。下载没有问题,上电后,有时正常运行,有时一上电没有现象,示波器看管腿的波形也没有,怀疑FPGA没有工作,有时epcs4的程序没有正确下载。量了FPGA的供电也都正常。到底是什么问题呢?

2015-01-08 15:18:37

cyclone fpga jtag突然不能下载程序,测量了一下电压,发现上电后 ,nstatus管教一直是低电平,其他供电正常 ,这是为什么呢?求帮忙解答,谢谢了

2016-09-27 20:40:03

如上,fpga开发版上电后有个红色的灯常亮了(正常情况下是闪烁的),现在也连接不上电脑,是板子坏了吗?有没有大神有过经验?求告知。

2023-06-01 14:55:08

我第一次做FGPA,PCB完全完成,现在是上电FGPA就烧了,但是不知道从什么地方下手,求大神指教,从哪开始调试。

2014-11-11 10:39:18

- 2.5VVCCO_35 - 2.5V连接到I / O bank的一些外部电路在2.5V FPGA电源轨之前上电(这超出了我的控制范围)。这会以奇怪的方式导致2.5V FPGA电源轨斜坡,请参考附图。基本上2.5VFPGA

2020-07-30 09:51:29

介绍了STC下载的过程,并设计全自动STC下载电路,使得整个下载过程不需要人工干预,这就大大提高的程序的开发效率,使得通过下载-运行-测试 模式完成程序的开发。STC下载模式介绍STC单片机IS...

2021-12-01 06:33:37

介绍一种无线电测向技术

2021-05-26 06:40:24

类故障的概念以及维修加电类故障的基本思路。◎加电类故障基本概念和现象首先笔者先给大家介绍加电类故障的基本概念。所谓加电类故障就是从上电或者复位到自检完成这一段过程中电脑所发生的故障的总称,通俗点来说就是...

2021-09-08 06:35:10

输出。而另一个常用的组合逻辑电路有译码的功能,即译码器,其逻辑功能是编码的逆过程,通常是将少比特的输入编码翻译为多比特的数据信息输出。由于两者的实现方式非常类似,这里仅以编码器中的优先编码器为例介绍一下其在FPGA开发板上的实现过程。原作者:语雀

2022-07-21 15:38:45

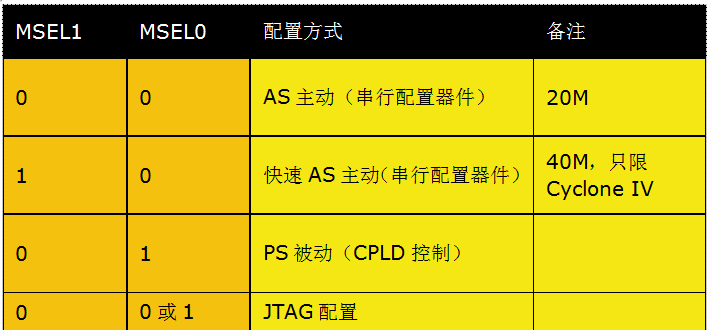

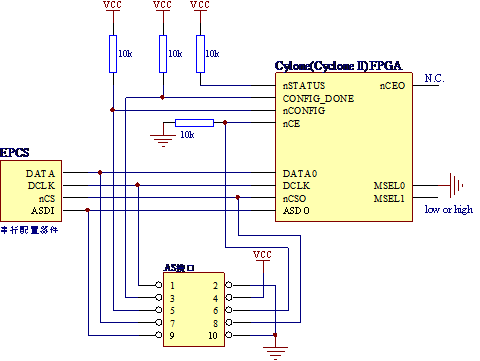

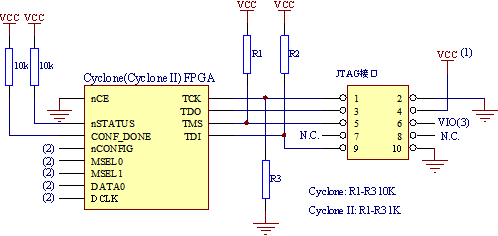

必要的。 本节介绍设计一款FPGA最小系统的过程,通过设计来学习PCB电路板(四层)和FPGA编程入门知识,具体要求如下: 方案:调试芯片+FPGA芯片+闪存要求: 01. 了解FPGA芯片最小

2023-03-27 11:57:14

你好,ADI工程师,我现在想用AD9516-4时钟芯片产生一个200M的时钟,给FPGA用。当我单独测试AD9516-4时,能够产生200M时钟,并且多次上电依然可以,但是当我把fpga及其外围电路

2018-12-20 14:15:47

学习的时候了解到FPGA的多路供电要求一定的上电断电顺序,目前在搞Altera的Cyclone IV系列的FPGA,主要有内部逻辑供电VCCINT,PLL供电VCCD_PLL,IO口供电VCCIO等

2017-05-18 22:36:29

CPLD和FPGA介绍及应用原理[/hide]

2009-10-22 15:19:14

M032芯片的所有GPIO在MCU上电过程直到完成reset的这段过程中,是什么状态?项目需要用GPIO控制多个外部IO,需要在设备上电过程中有明确的IO状态。

I/O Initial State

2023-08-21 07:38:50

1,(正泰抵押研究院与翼辉信息):MCU上电后 到 用户main函数运行 之间的过程?MCU上电也就想到与重启复位,引起复位的原因有很多:1,上电复位2,外部产生的手动复位信号3,执行复位指令4

2021-12-13 08:05:05

和boot1电平对应的意义可能不同,下表是STM32F4xx系列的启动方式选择 当STM32上电时,无论哪种启动模式,程序都将会从地址0x0000 0000开始执行,三种启动模式只是将各自存储空间映射到地址

2023-04-07 15:10:20

STM32加电启动的具体过程是怎样的?

2021-11-29 06:57:08

1.同样的板子,用过好多块,都没有问题,就这块无法加载,应该不是PCB设计问题。2.我设计的是主串加载模式(Master Serial)。硬件上将FPGA的M2~M0直接接到GND上。3.上电以后

2015-08-15 09:20:26

的内部的一些特性来试图解决这个问题。 要解决这个问题首先要了解FPGA上电初始化过程,这里我们是以ALTERA的ArriaGX的AS模式来进行研究。第一步控制POR时间 FPGA的AS配置主要分为

2015-01-22 14:41:34

和支撑,十分小巧有特色。下面咱们上电测试一下,确认一下整体通电情况,能够正常上电,而且喇叭还播放音频。(ps:一定要连接JTAG口,如果在办公室测试,不想影响他人,可以提前将喇叭插头拔掉)。 下面咱们

2022-03-08 06:35:09

、第三节介绍了电荷放大器及和混叠滤波电路的实现方法,第四节着重介绍了FPGA的实现方法,最后介绍了方案的实际应用情况。

2019-07-01 06:11:15

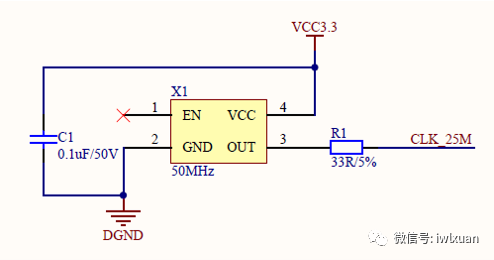

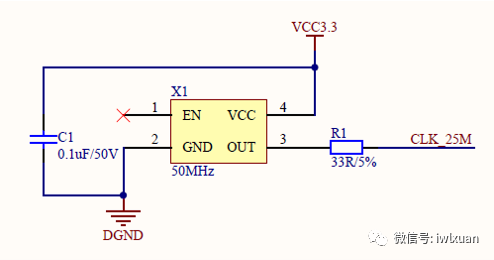

一、本文内容本文主要包含以下三个基本外围电路的调试过程与调试结果:电源模块时钟模块复位模块二、电源模块调试无论对FPGA还是DSP而言,对电源的上电顺序都有一定的要求,且不同型号的器件对电源轨的顺序

2021-11-11 06:51:24

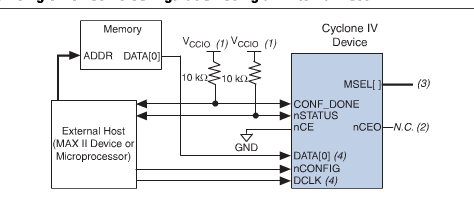

bit文件下载到FPGA或存储器的任务,另一方面则要完成FPGA上电启动时加载配置数据的任务。在开始设计FPGA的配置电路之前,我们不妨花一些篇幅简单的了解一下FPGA的配置过程和配置方式。大都数

2016-08-10 17:03:57

之后最高只能到400M,在全国电设里能用上么?从今年的题目来看,一届的频率比一届要高,以后的题目估计不会再出现低频题目了。我知道FPGA是并行操作,看过那个很多人说,ALTERA的芯片最高时钟频率也只能到200M,在高的话处理效果就不会很好。我就是 想问如果用FPGA的这款 芯片最高可以处理多高频率的信号?

2015-09-13 11:25:37

关于FPGA芯片资源介绍不看肯定后悔

2021-09-18 08:53:05

本文介绍了基于2600系列的IDDQ测试过程与功能实现。

2021-05-07 06:25:08

使得设计调试和检验变成设计周期中最困难的流程。本文重点介绍在调试FPGA系统时遇到的问题及有助于提高调试效率的技术,通过逻辑分析仪配合FPGA View软件快速有效的观测FPGA内部节点信号。最后提供了FPGA具体的调试过程和方法。

2019-06-25 07:51:47

产生的问题是在FPGA上电启动时这部分引脚总是会快速的闪过一次高电平才恢复低电平,请问应该怎么做才能使避免高电平会闪一次的这种情况?程序中因为需要复位时保持输出结果,所以不能使用复位信号,关键代码

2023-04-23 14:53:05

输出。而另一个常用的组合逻辑电路有译码的功能,即译码器,其逻辑功能是编码的逆过程,通常是将少比特的输入编码翻译为多比特的数据信息输出。由于两者的实现方式非常类似,这里仅以编码器中的优先编码器为例介绍一下其在FPGA开发板上的实现过程。原作者:硬木课堂语雀

2022-08-04 17:39:32

大家好,我们正在设计一个基于kintex-7 FPGA的电路板。该板具有DDR,QDR,BPI,以太网,UART等外设。我们有一个关于加电排序的查询。有没有要求外围IC在FPGA上电之前应该上电,反之亦然。感谢致敬Tarang JIndal

2020-07-31 11:32:50

1、CPU上电后加载程序的流程芯片上电解复位之后执行的第一段程序,在芯片中称之为Bootrom loader。这部分程序在芯片制造过程中固化到其内部的ROM空间,具备只读属性,在实际使用过程中无法

2022-06-21 15:28:35

如何控制FPGA各电源的上电顺序呢?请教一下大神

2023-03-27 13:48:32

你好,在我们的研究中,我们正在探索FPGA器件上SRAM的上电状态的固有随机性。因此,我们现在正试图在启动后从aVirtex-5器件读出分配的RAM值。但是,根据“Virtex-5 FPGA配置指南

2020-06-18 09:26:09

最近在用AD7768在做数据采集,采用FPGA控制和处理转换后的数据,但是将FPGA和AD7768端口链接后,每次上电AD都会发烫 ,断开连线后正常,这是怎么回事

2018-08-06 09:17:15

的内部的一些特性来试图解决这个问题。 要解决这个问题首先要了解FPGA上电初始化过程,这里我们是以ALTERA的ArriaGX的AS模式来进行研究。第一步控制POR时间 FPGA的AS配置主要分为三个过程

2015-01-20 17:37:04

嗨,大家好,我遇到了Xilinx ISE映射过程的棘手问题。当我综合我的设计时,我得到了一些FPGA资源的利用。虽然在映射过程中映射到FPGA上的LUT时,所有利用率都会达到0%。他很可能是由于

2020-06-13 09:57:50

本人做课设,想用FPGA输出一个方波作为时钟信号,使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下载了程序之后,发现只有上电和手动复位后

2016-12-08 16:20:03

求助:基于SRAM结构的FPGA上电瞬间电流大小如何去评估,上电瞬间的电流很大,比正常工作电流大很多,如何去评估?资料上没找到描述,感谢讨论

2019-04-18 16:50:00

求大神详细介绍一下FPGA嵌入式系统开发过程中的XBD文件设计

2021-05-06 08:19:58

现在的FPGA还严格要求上电时序吗?想请教一下大家

2017-09-26 15:39:07

引言 电源时序控制是微控制器、FPGA、DSP、 ADC和其他需要多个电压轨供电的器件所必需的一项功能。这些应用通常需要在数字I/O轨上电前对内核和模拟模块上电,但有些设计可能需要采用其他序列

2019-07-03 08:15:19

上电过程 上电过程电源不是线性增加,而会出现电压降低的现象,如图所示,称为上电回沟。 这个问题觉得应该分两种情况分析: 1. 高速电路上信号线的回钩:反射,串扰,负载瞬变... 2. 电源电路上的回

2021-12-31 06:59:38

FPGA的仿真与调试在FPGA开发过程中起着至关重要的作用,也占用了FPGA开发的大部分时间。所以适当减少或简化FPGA的仿真与调试过程无疑是对FPGA开发的加速,所对产品成型的时间。这里我们将利用

2020-04-25 08:00:00

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行

2019-07-18 08:10:11

Hi all,

请教下Zstack中Coordinator上电过程PANID的选取问题.

跟踪Zstack代码最终将调用NLME接口函数NLME_NetworkFormationRequest()来

2018-06-01 12:36:31

大家好, 谁能告诉我Spartan-3AN的FPGA上电和闪存配置之间的时间间隔?谢谢RGDS以上来自于谷歌翻译以下为原文Hi All, Could anyone tell me the Time

2019-06-27 08:15:46

请问CPLD/FPGA上电初始时IO口的状态是怎么样的呢?

2023-04-23 14:26:44

本帖最后由 一只耳朵怪 于 2018-6-14 10:48 编辑

请问TMS320F28035上电过程中是否将IO口设置为输入状态?上拉电阻多大?

2018-06-14 06:26:13

软件无线电技术因为其灵活性被广泛用于无线通信产品和射频检测仪器。本文介绍了软件无线电在射频检测仪器和射频检测方法上的应用。按照软件无线电原理,将无线产品看作射频前端+基带电路+辅助电路的模块构架,就可以用射频参数检测替代昂贵的通信功能检测,从而提高生产者的市场竞争力。

2019-07-22 07:32:59

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

简化Xilinx和Altera FPGA调试过程:通过FPGAViewTM 解决方案,如混合信号示波器(MSO)和逻辑分析仪,您可以在Xilinx 和Altera FPGA 内部迅速移动探点,而无需重新编译设计方案。能够把内部FPGA

2009-11-20 17:46:26 26

26 FPGA整体视频介绍

视频教程

2010-11-18 16:22:39 265

265 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2013-03-14 15:18:22 64

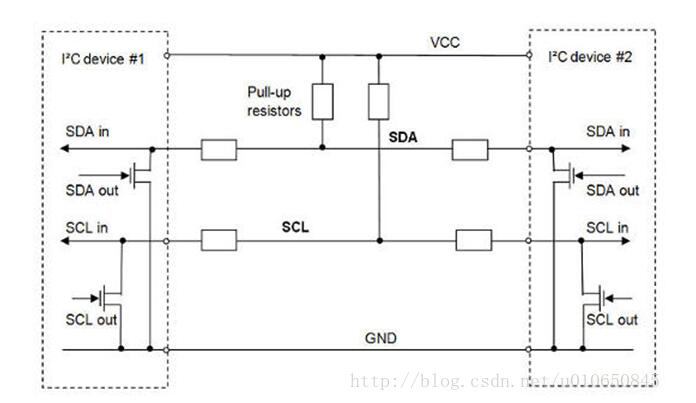

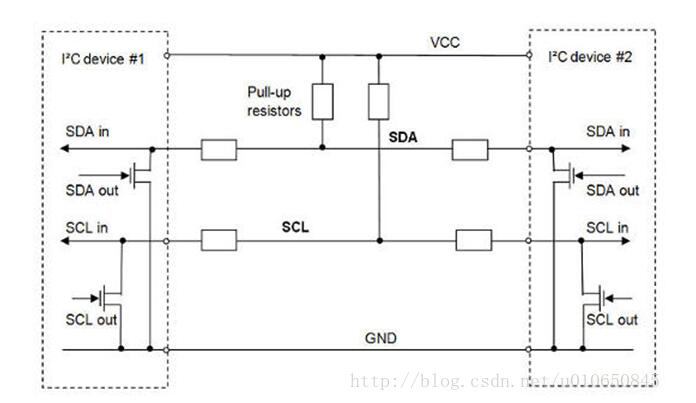

64 本文首先介绍了IIC总线概念和IIC总线硬件结构,其次介绍了IIC总线典型应用,最后详细介绍了IIC总线的FPGA实现原理及实现过程。

2018-05-31 10:56:50 6325

6325

本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 如果你在采用FPGA的电路板设计方面的经验很有限或根本没有,那么在新的项目中使用FPGA的前景就十分堪忧——特别是如果FPGA是一个有1000个引脚的大块头。继续阅读本文将有助于你的FPGA选型和设计过程,并且有助于你规避许多难题。

2020-11-01 09:44:54 1826

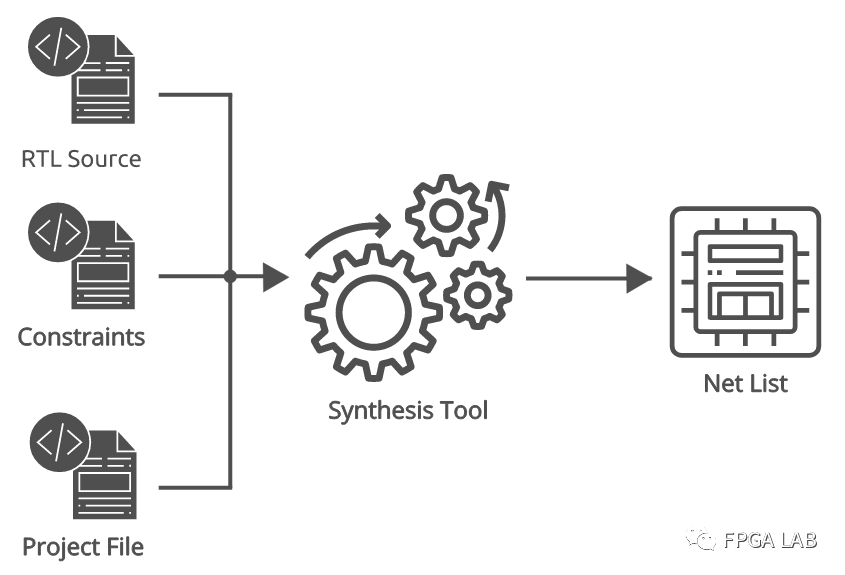

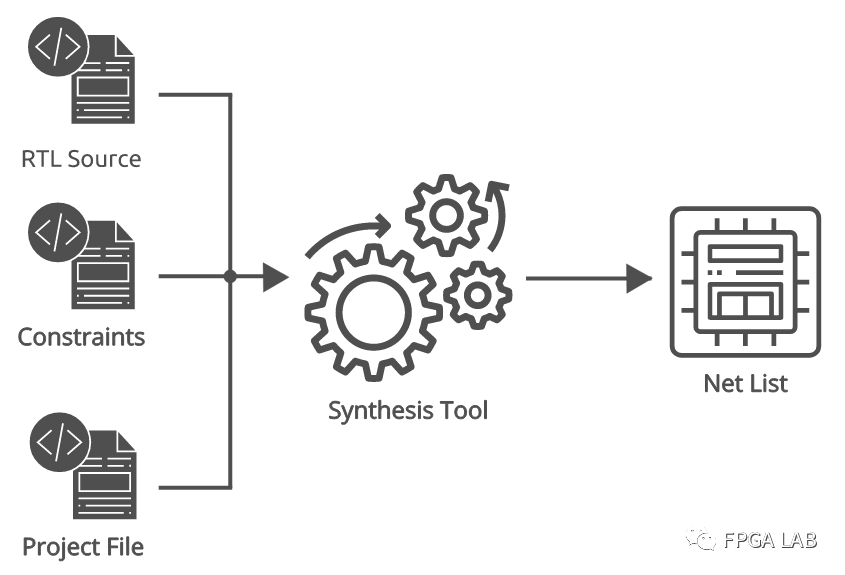

1826 构建FPGA的第一阶段称为综合。此过程将功能性RTL设计转换为门级宏的阵列。这具有创建实现RTL设计的平面分层电路图的效果。

2023-06-21 14:26:16 511

511

其实用FPGA做的示波器有很多,开源的相对较少,我们今天就简单介绍一个使用FPGA做的开源示波器:

2023-08-14 09:03:18 881

881 小编在本节介绍FPGA芯片外围电路设计规范和配置过程,篇幅比较大,时钟的设计原则就有17条,伙伴们耐心读一读。

2023-08-15 16:18:11 3374

3374

电子发烧友App

电子发烧友App

评论