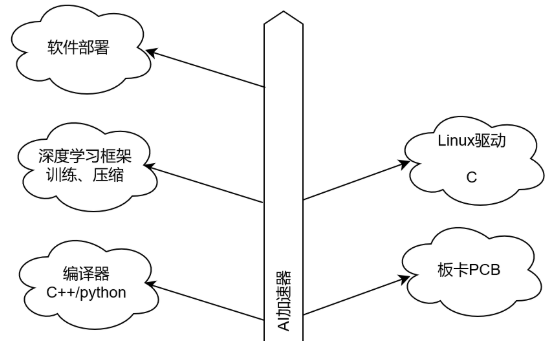

相比GPU和GPP,FPGA在满足深度学习的硬件需求上提供了具有吸引力的替代方案。凭借流水线并行计算的能力和高效的能耗,FPGA将在一般的深度学习应用中展现GPU和GPP所没有的独特优势。同时,算法

2016-07-28 12:16:38 7349

7349 大家好,又到了每日学习的时间了,今天我们来聊一聊基于FPGA的异步FIFO的实现。 一、FIFO简介 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通

2018-06-21 11:15:25 6164

6164

的主要有三种不同架构的器件种类:CPU,GPU,AI芯片/FPGA。CPU是一个通用架构芯片,其计算能力和数据带宽相对受到限制,面对大计算量的深度学习就显露出其缺点了。GPU含有大量的计算阵列,可以适用于大规模运算,而且其生态较为成熟和完整,所以现在包

2020-10-10 16:25:43 3349

3349

,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。 FPGA的每个BANK有4个IN_FIFO

2020-11-29 10:08:00 2340

2340

最近加的群里面有些萌新在进行讨论**FIFO的深度**的时候,觉得 **FIFO的深度计算比较难以理解** 。所

2023-11-28 16:19:46 347

347

FIFO先进深度?我也想知道我的输入是否改变为3个数据单元(每个16位)的突发,应该是什么深度?谢谢,阿伦以上来自于谷歌翻译以下为原文Hi All, I have a design issue, I

2019-01-10 10:45:27

本帖最后由 eehome 于 2013-1-5 10:08 编辑

FPGA学习总结[经典推荐]

2012-05-14 16:59:49

现场可编程门阵列 (FPGA) 解决了 GPU 在运行深度学习模型时面临的许多问题

在过去的十年里,人工智能的再一次兴起使显卡行业受益匪浅。英伟达 (Nvidia) 和 AMD 等公司的股价也大幅

2024-03-21 15:19:45

被用作系统中的缓冲元件或队列。因此FIFO的大小基本上暗示了所需缓存数据的容量,该容量取决于读写数据的速率。FIFO深度计算=B-B*F2/(F1*I), B为突发数据块大小

2013-05-28 14:17:37

为1024,但是在此处显示的却是1023。原因是因为FIFO结构的特殊性,并不是我们设置的有问题。所以,在我们这个异步FIFO中,深度为1023。

点击OK直接生成。在点击

2023-06-16 17:50:31

CORE 之 FIFO设计 本篇实现基于叁芯智能科技的SANXIN -B01 FPGA开发板,以下为配套的教程,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。 SANXIN-B01

2023-03-15 16:19:35

深度学习中的IoU概念理解

2020-05-29 09:24:28

深度学习中的图片增强

2020-05-28 07:03:11

汽车安全系统的发展进步中发挥重要的作用。而这些系统远不止仅供典型消费者群体掌握和使用。深度学习这一概念在几十年前就已提出,但如今它与特定的应用程序、技术以及通用计算平台上的可用性能更密切相关。深度学习

2022-11-11 07:55:50

简单的回顾的话,2006年Geoffrey Hinton的论文点燃了“这把火”,现在已经有不少人开始泼“冷水”了,主要是AI泡沫太大,而且深度学习不是包治百病的药方。计算机视觉不是深度学习最早看到

2021-07-28 08:22:12

神经系统,因此支持人工智能的概念。图 2:简易反向传播示例尽管深度学习具有效力,但其在实际应用中也遇到了一些挑战。对于容易受到系统限制因素(如总体成本、功耗和扩展计算能力)影响的嵌入式应用程序而言,在

2019-03-13 06:45:03

深度学习在预测和健康管理中的应用综述摘要深度学习对预测和健康管理(PHM)引起了浓厚的兴趣,因为它具有强大的表示能力,自动化的功能学习能力以及解决复杂问题的一流性能。本文调查了使用深度学习在PHM

2021-07-12 06:46:47

深度学习常用模型有哪些?深度学习常用软件工具及平台有哪些?深度学习存在哪些问题?

2021-10-14 08:20:47

摘要与深度学习算法的进步超越硬件的进步,你如何确保算法明天是一个很好的适合现有的人工智能芯片下发展?,这些人工智能芯片大多是为今天的人工智能算法算法进化,这些人工智能芯片的许多设计都可能成为甚至在

2020-11-01 09:28:57

创客们的最酷“玩具” 智能无人机、自主机器人、智能摄像机、自动驾驶……今年最令硬件创客们着迷的词汇,想必就是这些一线“网红”了。而这些网红的背后,几乎都和计算机视觉与深度学习密切相关。 深度学习

2021-07-19 06:17:28

怎样从传统机器学习方法过渡到深度学习?

2021-10-14 06:51:23

不多说,上货。IP CORE 之 FIFO 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。FIFO

2023-04-11 20:50:21

SPI2_CONFIG寄存器中FIFO深度是根据什么改变的?是根据TRANSCTRL寄存器的WRTRANCNT和RDTRANCNT设置改变吗?为什么我设置了WRTRANCNT和RDTRANCNT,SPI2_CONFIG寄存器中FIFO深度还是默认值0x00004311?

2023-05-26 07:46:57

大家好,在zynq 7000系列中,UART FIFO的深度为128字节,这是不是意味着直到所有128字节的数据都在FIFO中传输它才会传输?如果有人知道,请告诉我...谢谢

2020-03-31 09:29:05

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打开

2016-02-29 13:35:55

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打开

2016-02-29 13:35:55

`Xilinx FPGA入门连载56:FPGA片内异步FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1新建

2016-03-09 10:49:56

FIFO内缓存数据最多。计算此时写入数据-该阶段读出数据即为FIFO的最小深度。 Nwr = 120x = Nwr - Nrd = 120 - 96 = 24.二.为保证数据连续输出,求读取前

2020-02-22 20:37:49

`FZ3深度学习计算卡总结篇几个月的试用即将结束,也通过这个板子完成了自己的项目,具体的不方便公开,有网友私聊我相关资料,因此这里做一个统一的说明,能公开的帖子里面都发布了,其他的项目结束之后,会考

2021-01-10 14:39:17

学习的硬件需求上提供了具有吸引力的替代方案。凭借流水线并行计算的能力和高效的能耗,FPGA将在一般的深度学习应用中展现GPU和GPP所没有的独特优势。同时,算法设计工具日渐成熟,如今将FPGA集成到

2018-08-13 09:33:30

都出现了重大突破。深度学习是这些领域中所最常使用的技术,也被业界大为关注。然而,深度学习模型需要极为大量的数据和计算能力,只有更好的硬件加速条件,才能满足现有数据和模型规模继续扩大的需求。 FPGA

2019-10-10 06:45:41

- 恒定8 MB /秒(一旦开始读取,您将需要保持数据速率,不允许上溢/下溢)什么应该是fifo深度?谢谢,以上来自于谷歌翻译以下为原文Hi, I have a design problem where

2019-04-26 10:56:25

深度学习是什么意思

2020-11-11 06:58:03

上述分类之外,还被用于多项任务(下面显示了四个示例)。在 FPGA 上进行深度学习的好处我们已经提到,许多服务和技术都使用深度学习,而 GPU 大量用于这些计算。这是因为矩阵乘法作为深度学习中的主要

2023-02-17 16:56:59

《深度学习工程师-吴恩达》03卷积神经网络—深度卷积网络:实例探究 学习总结

2020-05-22 17:15:57

关于吴恩达深度学习总结(一)

2019-07-29 10:35:29

点开“memory compiler",然后选择FIFO,同时在右边填入自命名的器件名字。点下一步,在这一步中要设置FIFO的数据宽度,FIFO的深度,FIFO的类型(同步FIFO还是异步FIFO,他们

2012-03-27 12:28:32

嗨,我想计算异步fifo的深度,但我很困惑如何计算它。 fifo参数如下:写Clk Freq = 60 MHz。读取Clk Freq = 100 MHz。最大WriteBurst大小= 1024

2019-04-17 08:25:47

fifo不为空时,用rd clk = 50 MHz连续读出数据。从模拟开始,在5次写入后,fifo空置为空。如何正确计算深度?最初,我的深度为16,所有人都在董事会工作。然后进行实验,我改变了wr和rd

2019-04-09 06:25:58

数据进入FPGA的速率高于传出的速率,持续的传输会造成数据的溢出,断续的传输可能会造成数据不连续。使用基于LabVIEW FPGA的DMA FIFO作为主控计算机和FPGA之间的缓存,若DMAFIFO深度设置的合适,FIFO不会溢出和读空,那么就能实现数据输出FPGA是连续的。

2019-10-12 09:05:54

本文由回映电子整理分享,欢迎工程老狮们参与学习与评论内容► 射频系统中的深度学习► Deepwave Digital技术► 信号检测和分类示例► GPU的实时DSP基准测试► 总结回映电子是一家

2022-01-05 10:00:58

图像压缩之后的数据存入fifo,然后经过nrf2401发送。。但是由于图片尺寸比较大,导致fifo深度不够,受限于FPGA芯片尺寸的限制,fifo深度不能再选大了。。。求指导

2015-05-22 14:34:48

请问2812型DSP的SCI模块中,接收和发送数据都是16级的FIFO深度是什么意思?对这个16级深度的FIFO不太理解

2023-03-17 11:19:05

嗨,以下条件的FIFO深度是多少?8位并行数据连续出现(即没有突发长度)写入和读取没有理想的循环。写频率= 100MHz读频率= 70MHz谢谢娜文G K.

2020-05-21 07:45:14

计算机视觉与深度学习,看这本书就够了

2020-05-21 12:43:42

`立即学习—60天FPGA工程师入门就业项目实战特训营(3月16日开班) 谈谈FIFO阈值的阈值设置及深度计算1.什么是FIFO2.什么情况下使用FIFO3.什么FIFO的阈值4.FIFO的阈值

2020-02-19 21:09:35

首先介绍异步FIFO 的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法; 在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA 实现。

2009-04-16 09:25:29 46

46 容易地嵌入到实际应用系统中;2. 完成从简单的逻辑控制、数据采集、信号处理、数学计算等功能;3. 核心板FPGA芯片的所有管脚全部引出,可以直接

2023-02-03 15:14:29

基于FPGA的FIFO设计和应用

引 言

在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据的暂时存储

2009-11-20 11:25:45 2127

2127

FPGA设计的高速FIFO电路技术

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量

2010-05-27 09:58:59 2226

2226

为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定 FIFO 深度的方法。对FIFO不同深度的实验表明,采

2011-09-26 13:45:17 6923

6923

文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用异步FIFO的方法,在FPGA与DSP通信中的应用,具有传输速度快、稳定可靠、实现方便的优点。

2011-12-12 14:28:22 51

51 为实现目标识别与跟踪的应用目的 ,在基于 TMS320DM642 的 FIFO 基础上扩展存储空间 ,提出一种基于

FPGA实现 SDRAM 控制器的方法。分析所用 SDRAM 的特点和工作原理

2015-10-29 14:05:57 2

2 FIFO_学习心得。 FIFO_学习心得

2015-11-09 14:07:47 6

6 异步FIFO结构及FPGA设计,解决亚稳态的问题

2015-11-10 15:21:37 4

4 异步FIFO在FPGA与DSP通信中的运用

2016-05-19 11:17:11 0

0 FPGA是深度学习的未来,学习资料,感兴趣的可以看看。

2016-10-26 15:29:04 0

0 单片机(Microcontrollers)学习,FPGA学习总结[经典推荐],感兴趣的小伙伴可以瞧一瞧。

2016-11-03 15:15:39 153

153 由NSF资助的一个研究项目,目前正在研究如何使用RDMA高性能连接器将深度学习算法在FPGA和跨系统之间运行;另一个由Andrew Ng和两个超算专家牵头的项目,则希望把模型放在超级计算机上,给它们一个Python接口。

2017-02-10 16:32:30 744

744 本文我们就来分析目前主流的深度学习芯片的优缺点。 CPU 不适合深度学习 深度学习与传统计算模式最大的区别就是不需要编程,它是从输入的大量数据中自发地总结出规律,而传统计算模式更多都需要人为提取所需

2017-09-27 15:24:59 2

2 基于异步FIFO在FPGA与DSP通信中的运用

2017-10-19 10:30:56 10

10 摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现

2017-10-30 11:48:44 1

1 由腾讯云基础产品中心、腾讯架构平台部组成的腾讯云FPGA联合团队,在这里介绍国内首款FPGA云服务器的工程实现深度学习算法(AlexNet),讨论深度学习算法FPGA硬件加速平台的架构

2017-11-15 20:20:08 2468

2468 本文总结了Python、Matlab、CPP、Java、JavaScript、Lua、Julia、Lisp、Haskell、.NET、R等语言的深度学习库,赶紧收藏吧!Theano是一个Python

2017-11-16 14:20:45 2873

2873 在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 7873

7873

几乎所有深度学习的研究者都在使用GPU,但是对比深度学习硬鉴方案,ASIC、FPGA、GPU三种究竟哪款更被看好?主要是认清对深度学习硬件平台的要求。

2018-02-02 15:21:40 10203

10203

为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO

2019-01-04 14:25:07 4225

4225

本文从硬件加速的视角考察深度学习与FPGA,指出有哪些趋势和创新使得这些技术相互匹配,并激发对FPGA如何帮助深度学习领域发展的探讨。

2019-06-28 17:31:46 6529

6529 微软发布了 Project Brainwave,一个基于 FPGA 的低延迟深度学习云平台。微软官方测评显示,当使用英特尔的 Stratix 10 FPGA,Brainwave 不需要任何

2019-07-03 14:58:52 883

883 相比GPU和GPP,FPGA在满足深度学习的硬件需求上提供了具有吸引力的替代方案。凭借流水线并行计算的能力和高效的能耗,FPGA将在一般的深度学习应用中展现GPU和GPP所没有的独特优势。

2019-10-18 15:48:14 1326

1326 近十年来,人工智能又到了一个快速发展的阶段。深度学习在其发展中起到了中流砥柱的作用,尽管拥有强大的模拟预测能力,深度学习还面临着超大计算量的问题。在硬件层面上,GPU,ASIC,FPGA都是解决庞大计算量的方案。

2019-10-22 15:26:21 977

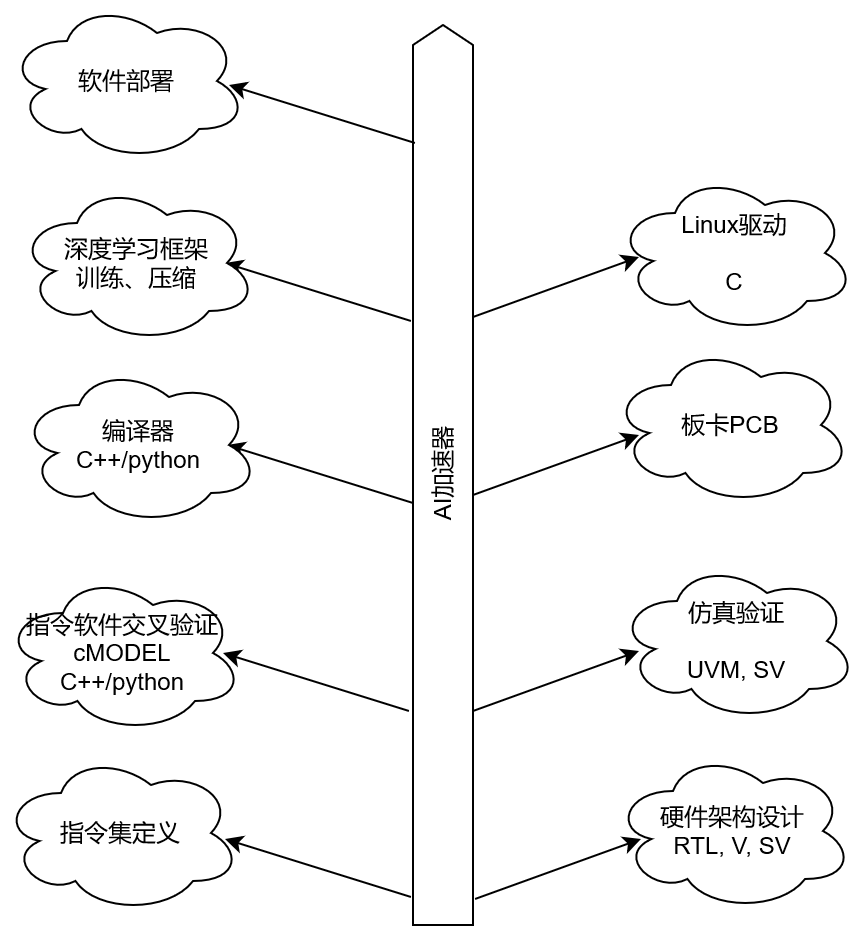

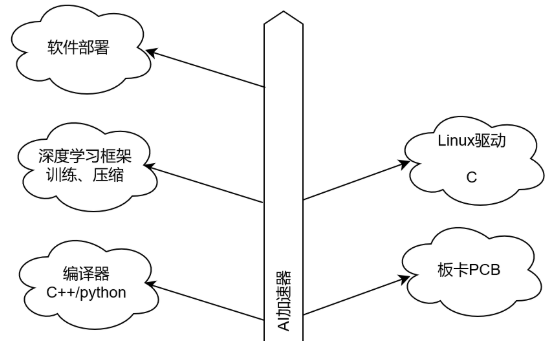

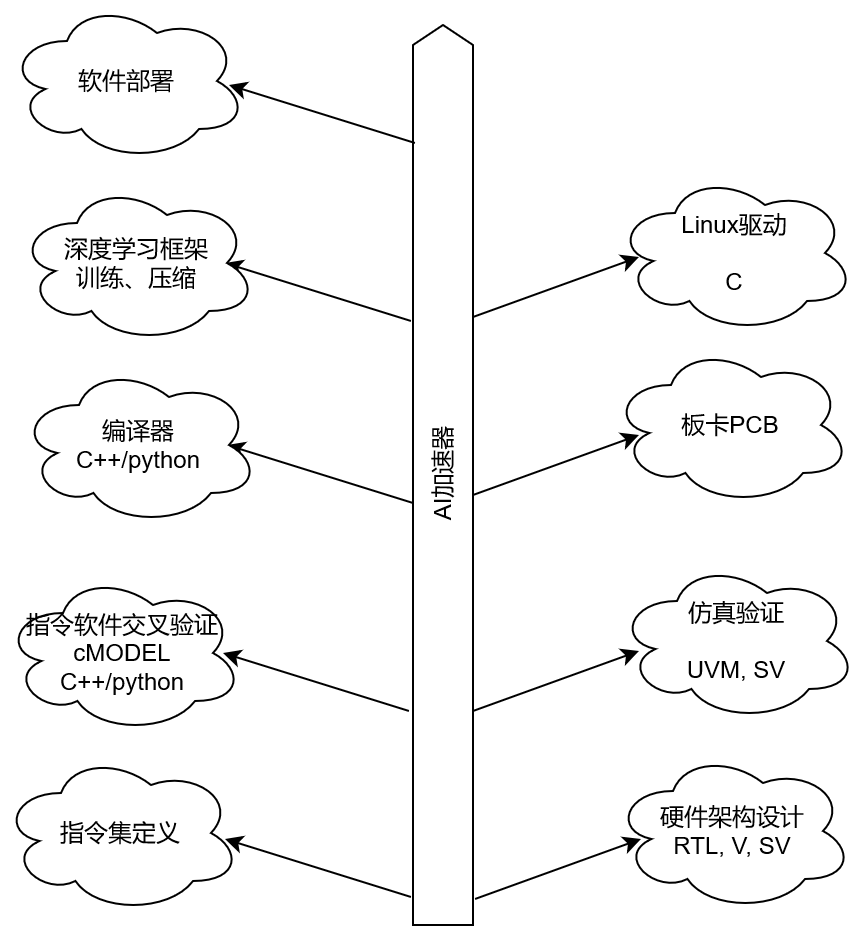

977 做深度学习加速器已经两年了,从RTL设计到仿真验证,以及相应的去了解了Linux驱动,深度学习压缩方法等等。

2020-03-08 16:29:00 8342

8342

FPGA电路FIFO设计的源代码

2020-07-08 17:34:37 15

15 近日,MIT却发出警告:深度学习正在接近计算极限,必须转变现有技术「大幅」提高计算效率。

2020-07-21 09:31:28 721

721 本篇文章用于总结之前学习的time quest,并且我已经能够利用公式,计算出slack了,并能够根据setup slack来更改优化代码了。时光由隔了1个月,时序分析的路没有终点,本篇文章是对之前

2021-01-13 16:02:00 10

10 FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

2021-03-12 06:01:34 12

12 由于平时我们工作中,FIFO都是直接调用IP核,对于FIFO深度选择并没有很在意,而在笔试面试过程中,经常被问及的问题之一就是如何计算FIFO深度。 当读数据的速率小于写数据的速率时,我们需要先将

2021-05-11 14:37:08 1950

1950

FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO

2021-09-09 11:15:00 6293

6293 FIFO 最小深度计算 例子 - 1:f_wr 》 f_rd,连续读写 写时钟80MHz。 读时钟50MHz。 Burst_Len = 120,也就是要求至少安全写入120个数据。 连续写入和连续

2021-09-10 09:23:28 1507

1507

FIFO最常被用来解决写、读不匹配的问题(时钟、位宽),总结下来,其实FIFO最大的作用就是缓冲。既然是缓冲,那么就要知道这个缓存的空间到底需要多大。接下来的讨论,都建立在满足一次FIFO突发传输

2022-02-26 17:41:52 3045

3045

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中对图像的一行数据进行缓存时,可以采用FIFO这一结构,如上图所示,新一行图像数据流入到FIFO1中,FIFO1中会对图像数据进行缓存,当FIFO1中缓存有一行图像数据时,在下一行图像数据来临的时候,将FIFO1中缓存的图像数据读出,并传递给下一个FIFO

2022-05-10 09:59:29 3056

3056 由于平时我们工作中,FIFO都是直接调用IP核,对于FIFO深度选择并没有很在意,而在笔试面试过程中,经常被问及的问题之一就是如何计算FIFO深度。

2022-07-03 17:25:28 2222

2222 作者:凯鲁嘎吉 来源:博客园 这篇文章对现有的深度聚类算法进行全面综述与总结。现有的深度聚类算法大都由聚类损失与网络损失两部分构成,博客从两个视角总结现有的深度聚类算法,即聚类模型与神经网络模型

2022-12-30 11:15:08 648

648 这是新的系列教程,在本教程中,我们将介绍使用 FPGA 实现深度学习的技术,深度学习是近年来人工智能领域的热门话题。

2023-03-03 09:52:13 1088

1088 当今的深度学习应用如此广泛,它们能够为医疗保健、金融、交通、军事等各行各业提供支持,但是大规模的深度学习计算对于传统的中央处理器(CPU)和图形处理器(GPU)来说是非常耗时和资源密集的。

2023-03-09 09:35:24 1941

1941 FPGA(Field-Programmable Gate Array)是一种灵活的可编程硬件设备,它在深度学习应用领域中具有许多优势。

2023-03-09 09:41:15 1350

1350 这是新的系列教程,在本教程中,我们将介绍使用 FPGA 实现深度学习的技术,深度学习是近年来人工智能领域的热门话题。

2023-04-12 10:19:34 533

533 这是新的系列教程,在本教程中,我们将介绍使用 FPGA 实现深度学习的技术,深度学习是近年来人工智能领域的热门话题。

2023-05-04 11:22:36 651

651

FIFO(First In First Out)是一种先进先出的存储结构,经常被用来在FPGA设计中进行数据缓存或者匹配传输速率。

2023-08-07 15:39:50 446

446 什么是深度学习算法?深度学习算法的应用 深度学习算法被认为是人工智能的核心,它是一种模仿人类大脑神经元的计算模型。深度学习是机器学习的一种变体,主要通过变换各种架构来对大量数据进行学习以及分类处理

2023-08-17 16:03:04 1300

1300 点击上方 蓝字 关注我们 第一节:fifo基础 内容: 1. 掌握FPGA设计中关于数据缓存的使用 2. 掌握FIFO工作原理

2023-11-17 14:00:02 179

179

电子发烧友App

电子发烧友App

评论