目前商用领域的成像系统还是以嵌入式ASIC为主(成品时间快,性价比高),对于一些军工、医学等特殊领域还是以FPGA为主,在特殊领域里延迟是最先考虑的问题(成本不是主要问题),所以今天介绍一下使用FPGA实现低延迟的成像系统,这里说明一下,整个系统调试比较麻烦(和sensor有关),很大可能调试不出图像,所以大家只需要知道有这个架构即可,有需求可以自己调试。

低延迟架构

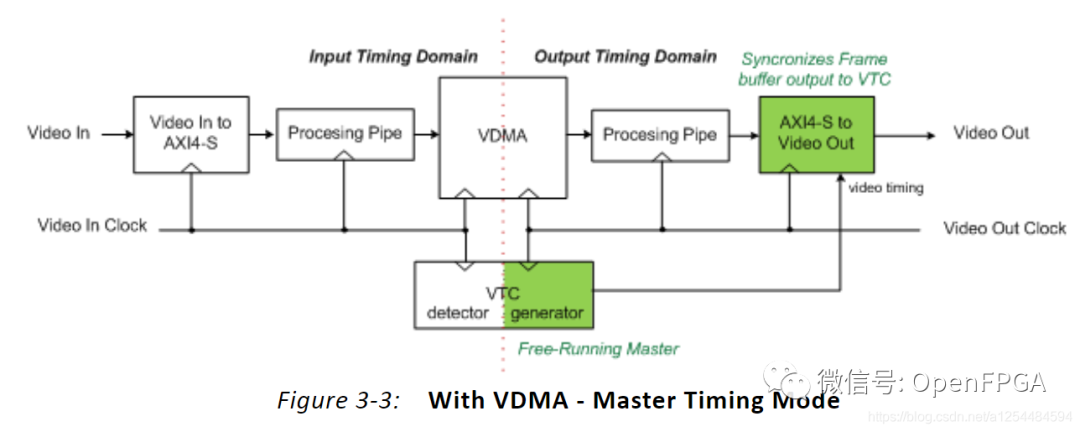

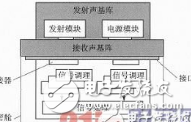

我们这次使用的是AMD-Xilinx FPGA,大部分的图像处理都有IP可以使用,在官方文档中有相关的架构,具体如下:

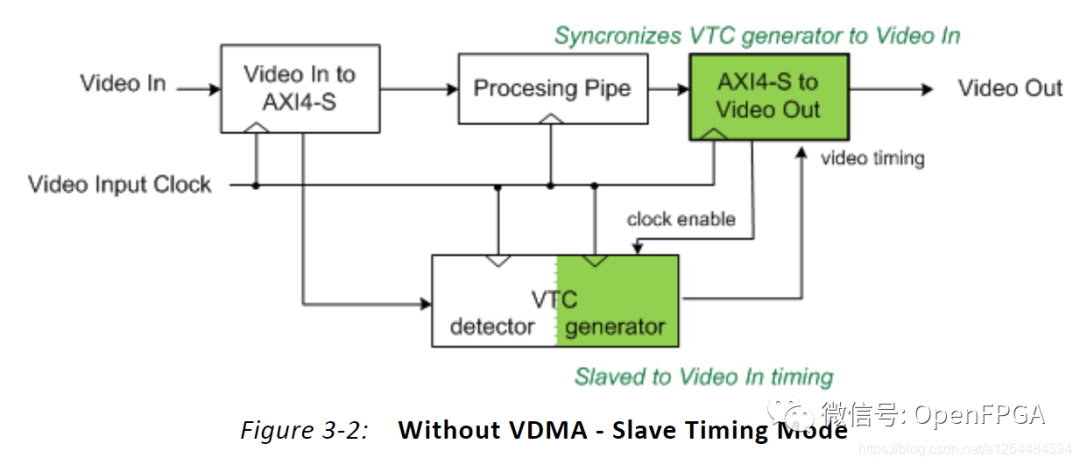

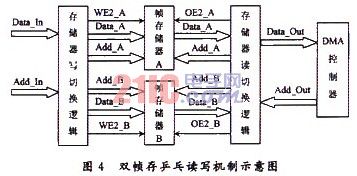

上面的架构是比较通用的架构,官方也有例程可以参考,但是上面架构多了一个VDMA,这就导致视频传输的时候有1到几帧的延迟,这对于低延迟、高分辨率的情形肯定是不能容忍的。所以官方对于特殊情况建议使用下面的架构:

去掉了VDMA,但是对于时钟系统要去更高,对于视频输入输出在不同时钟域情况下是使用不了的,所以整体要求比较高。但是砍掉了VDMA和DDR,所以整体成本会低很多。关于没有VDMA情况下的各个IP的设置及测试可以看下面的文章《不使用VDMA情况下使用AXI4总线实现视频输入输出(低延迟首选)》。

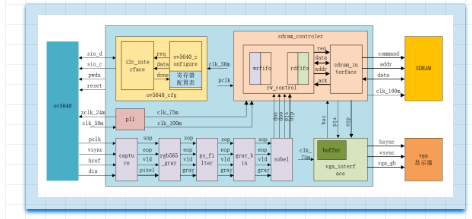

FPGA系统架构设计

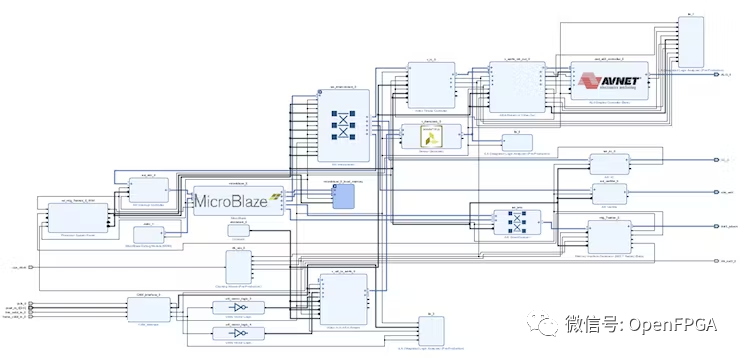

我们还是参考上面的架构来设计我们的系统。

当我们与图像sensor对接时,我们通常会以不同的格式接收图像,例如 MIPI 、并行接口,在我们接收视频之前,我们需要先配置sensor按照我们的需求运行。通常,sensor需要通过 I2C 或 SPI 进行配置。

这次演示的平台:

7系列FPGA

MT9M114 sensor

sensor 的接口非常简单,可以分为视频接口和配置接口(IIC)。

视频接口由 10 位数据(分为 8 位和 2 位)、帧和行有效、像素时钟和参考时钟 (24 MHz) 组成。

配置接口由连接到sensor的 I2C 和 复位IO组成。

该解决方案的架构如下:软核处理器(MicroBlaze)通过 I2C 配置sensor。虽然图像处理路径将在 FPGA 中实现,但由于这是一种低成本应用,该解决方案不会使用 DDR 存储器中实现外部帧缓冲区,而是图像处理流水线将完全在 FPGA 中实现。

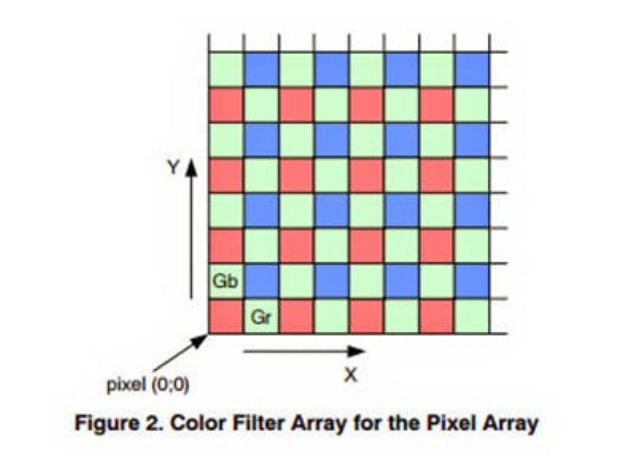

Sensor中由于我们配置的是RAW数据,所以还需要使用Sensor Demosaic和Gamma(基本成像IP)IP。

该设计还将使用软核处理器来控制视频时序和图像处理路径的其他相关配置任务。

Vivado 工程构建

搭建MicroBlaze 系统

添加其他IP

整个系统需要的IP主要如下:

CAM 接口 - 此接口与 sensor接口连接,简单处理数据(选择RAW数据的位数),此IP非必须

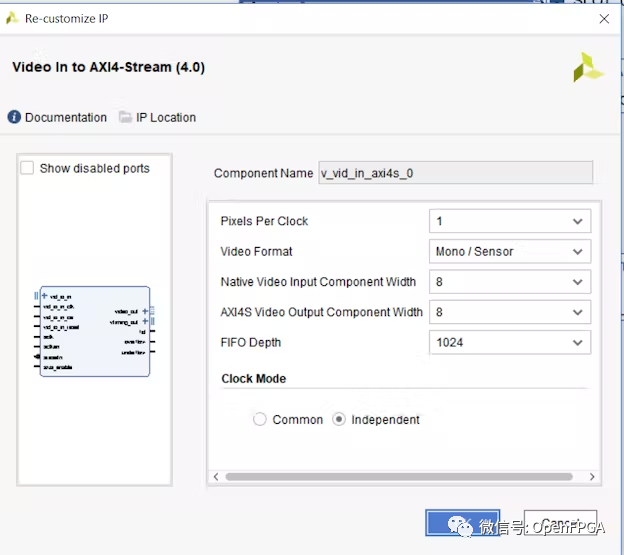

Video to AXIS - 这会将并行视频转换为 AXI 流格式

Sensor Demosaic - 将代表 R、G 或 B 的 RAW 像素值转换为 24 位 RGB 格式

Video Timing Generator - 生成输出格式的视频时序信号

AXI Stream to Video Out - 将 AXI Stream 转换为并行视频

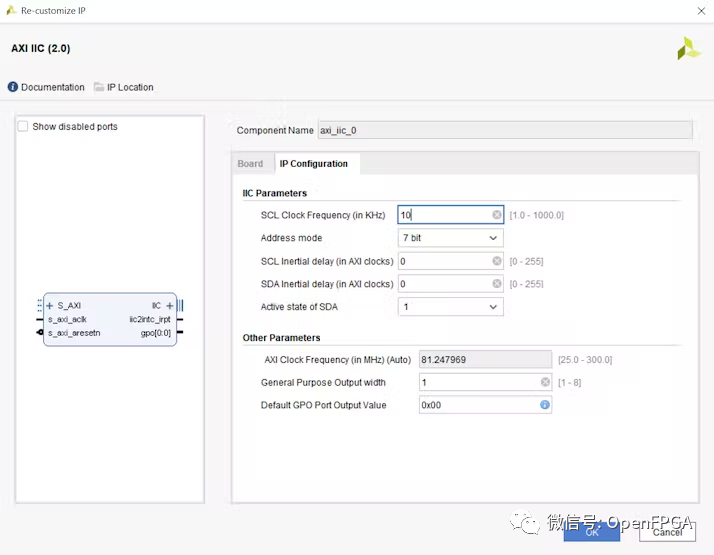

AXI IIC - 连接到 MicroBlaze,用于配置sensor

AXI UART - 连接到 MicroBlaze,用于软件调试

添加完后就可以连线了,完整的框图应如下所示。完整的工程在文章最后给出。

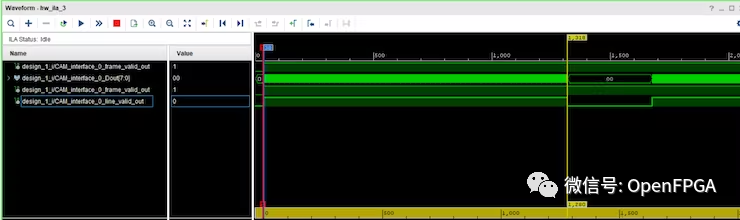

在 AXI Stream 中,使用 TUser 指示帧的开始,使用 TLast 指示行的结束。

IP的关键设置

Video to AXIS

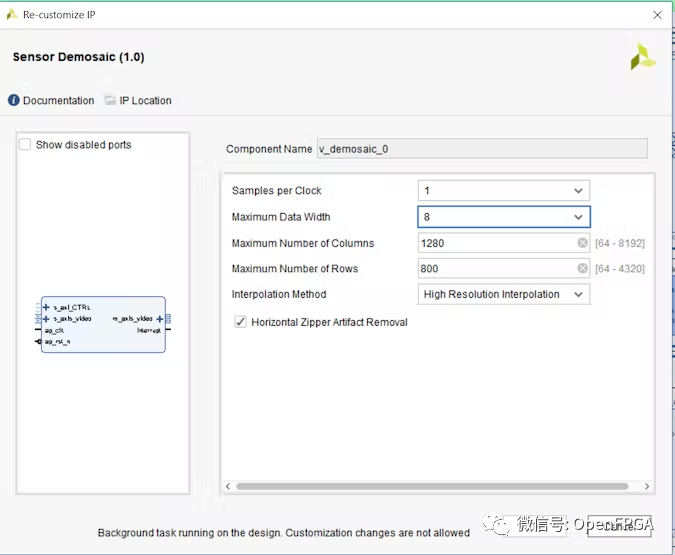

Sensor Demosaic

AXI IIC 设置

其他IP可以查看文章最后的工程查看。

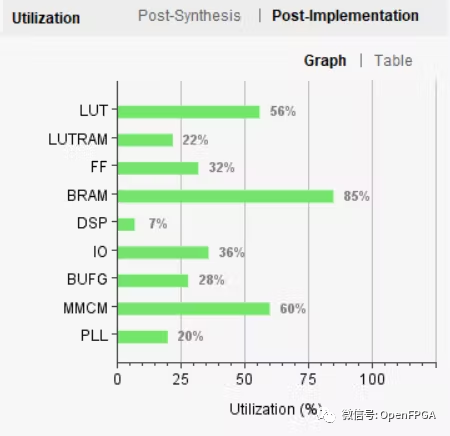

资源使用率

在Arty S7-50 的总利用率如下所示。

SDK 中编写软件

生成 Vivado 硬件后,下一步就是编写应用软件,用于配置sensor和视频处理IP核。

因此,软件中将执行以下操作:

初始化 AXI IIC、VTC 和中断控制器

设置AXI 相关中断控制器 - 这包括三个中断服务例程。IIC 发送、接收和状态各一个。

在 VTC 配置输出时序

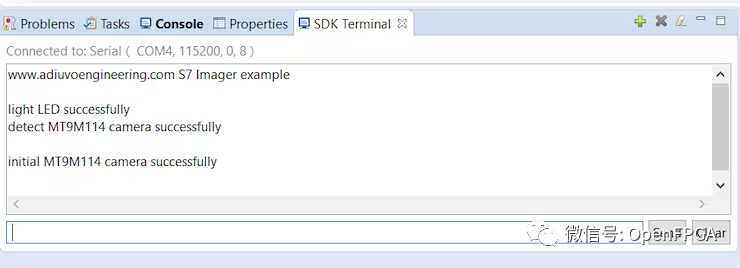

通过 I2C 复位sensor并点亮 sensor板子上 LED

通过I2C读取sensor-MT9M114的ID,来检测相机是否存在(外围设置是否正确)

通过 I2C 配置和初始化相机 - 这是最浪费时间的,好在有很多资料可以参考

初始化相机后,我们将能够在 ILA 上看到视频流。

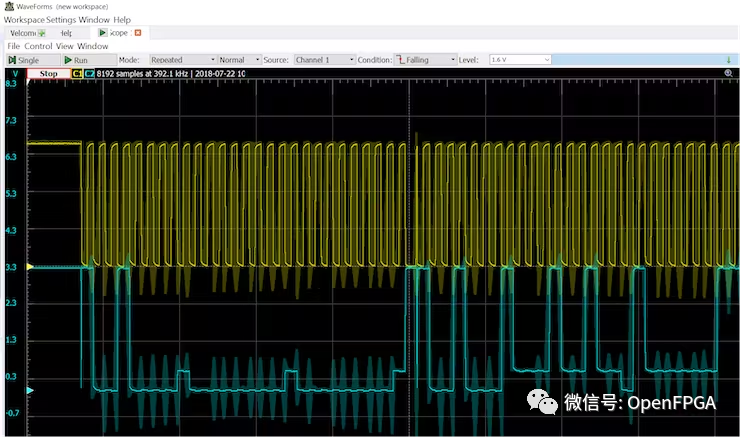

调试过程中测量的FPGA和sensor之间的 I2C 通信信号。

使用 AXI UART 调试软件:

一旦相机初始化,我们可以使用 ILA 采集信号:

上图显示了 1280 像素的线宽。

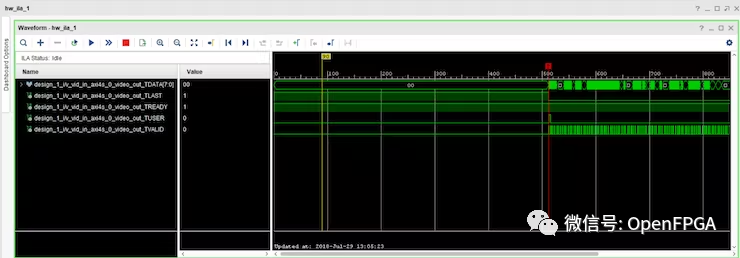

AXI Stream 是一种单向总线,用于将数据从主机传输到从机,作为数据流,它不包含地址通道。为了通过 AXI 流控制流和传递视频时序信息,我们使用了以下信号:

TReady - 当准备好接收数据时由下游外设断言

TValid - 当输出数据有效时通过发送外设断言

TUser - 为帧的开始发出

TLast - 为行尾标志

由于我们没有 使用VDMA,所以 AXIS 流上的视频输出是一个连续块,并且 TValid 在活动像素周期内不会断言和取消断言。

我们可以通过使用图像处理链的像素时钟来确保 Tvalid 是连续的。

软件部分还是参考最后的工程吧,除了sensor需要单独编写,其他都是由SDK自带的例程修改而来。

总结

虽然上面的架构和最后的设计比较简单,但是调试起来还是很难得,只不过我写的比较简单,一旦出不来视频,重点按照最开始官方架构检查PCLK。

该工程主要参考架构和架构中时钟域的处理,注意pCLK(像素时钟)和ACLK的走向。

审核编辑:刘清

电子发烧友App

电子发烧友App

评论