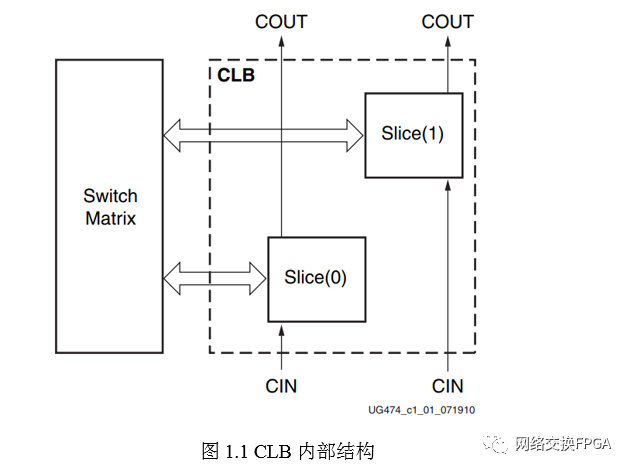

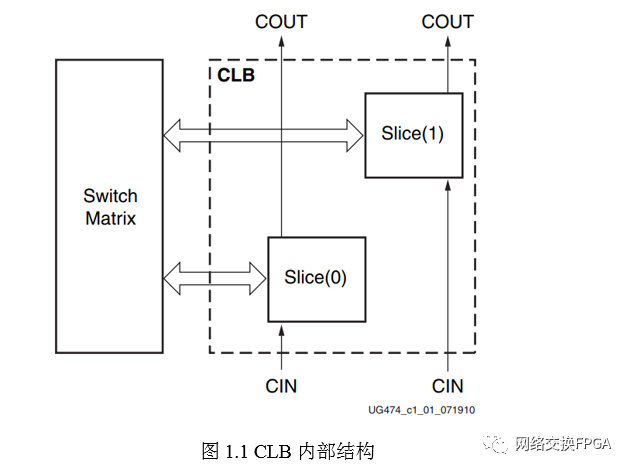

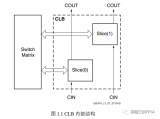

的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相同的SliceL或则一个SliceL和一个SliceM构成。每个Slice不仅可以用于实现组合逻辑、时序逻辑。其中

2020-11-02 17:18:05 5016

5016

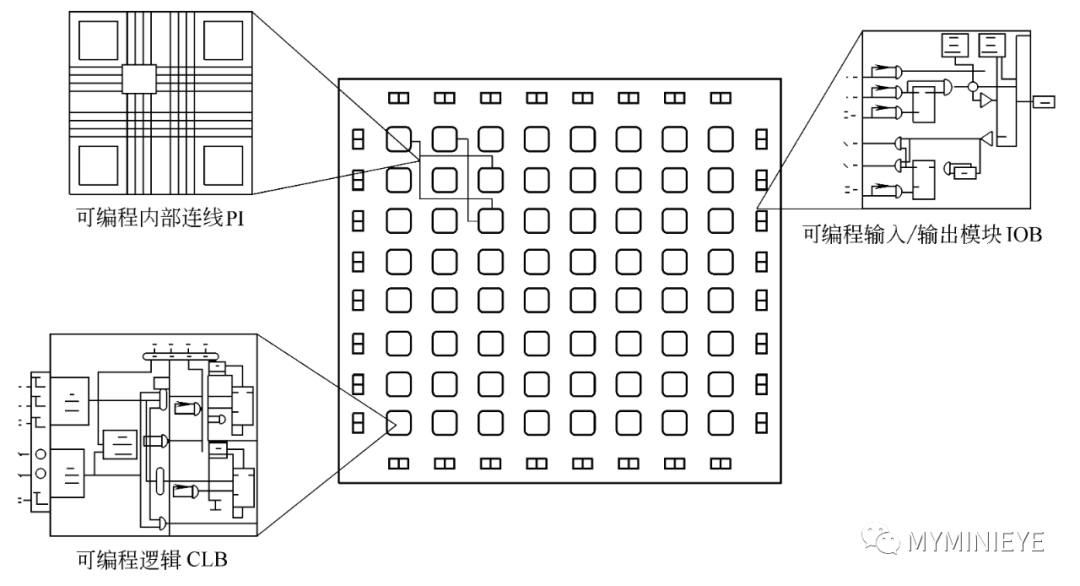

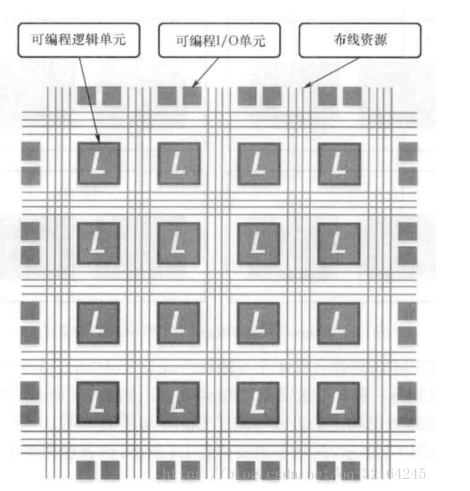

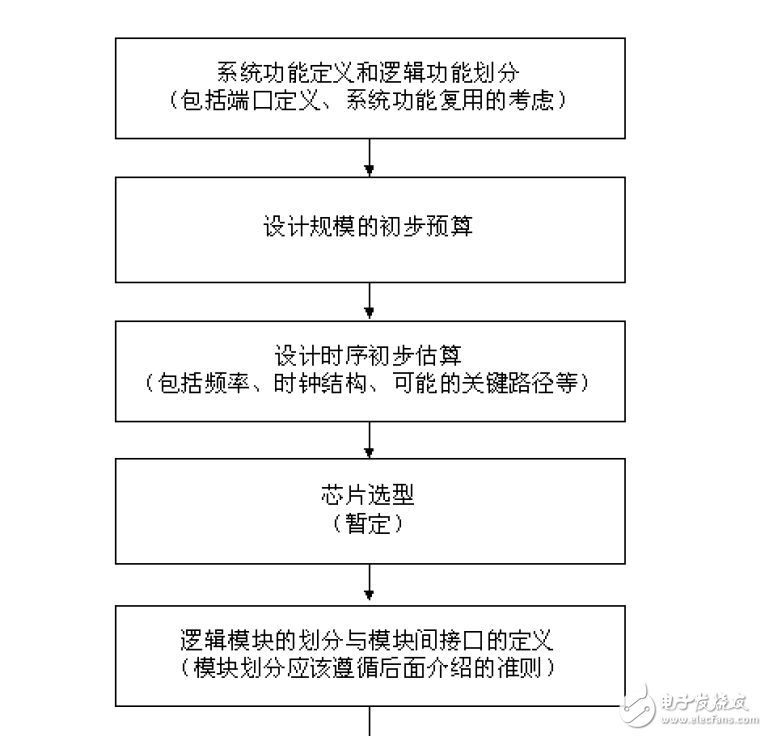

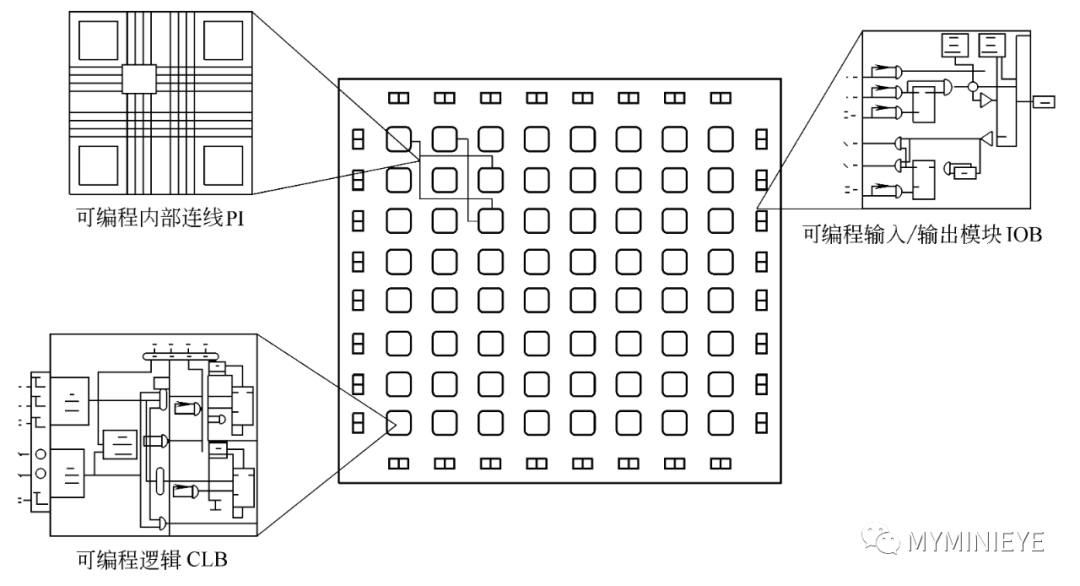

研究背景及基础知识 FPGA是实现高性能计算与网络的重要工具,得益于其高度的并行性与用户可编程的特性,FPGA得到了越来越广泛的应用。FPGA由CLB(Configurable Logic

2020-11-23 13:14:20 8757

8757

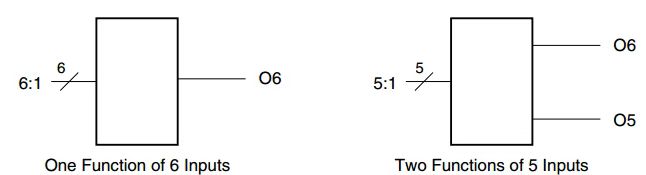

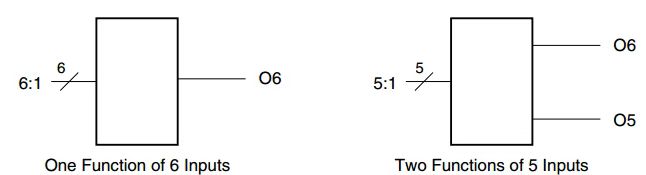

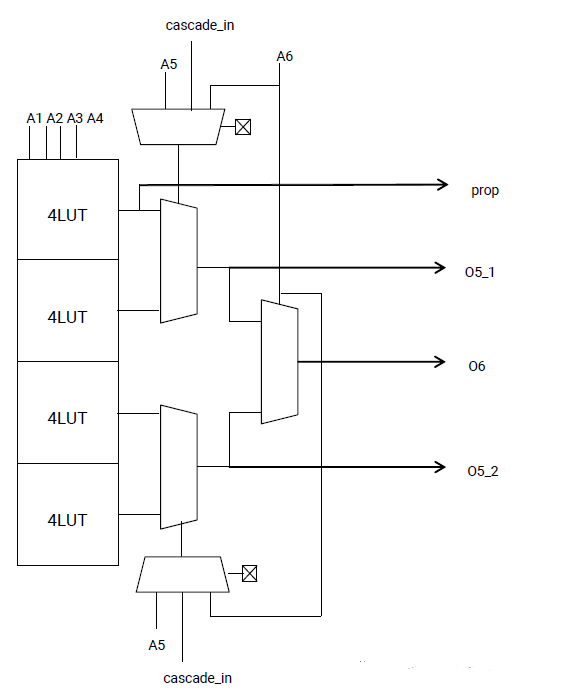

。利用xilinx器件中LUT的结构特征,设计出的乘法器不但能灵活适应数据位宽,而且能最大限度降低LUT资源使用。 Xilinx ultrascale器件LUT结构 在这里简要介绍一下

2020-11-30 11:45:21 2385

2385

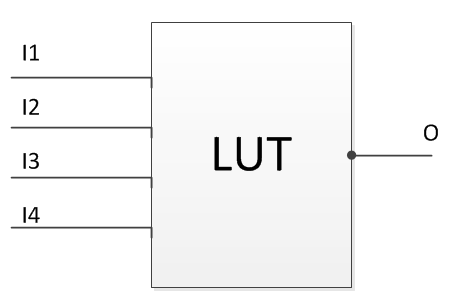

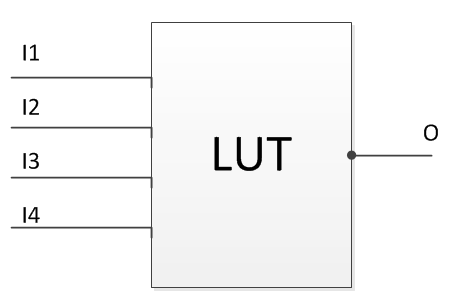

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

2023-03-13 10:28:06 2053

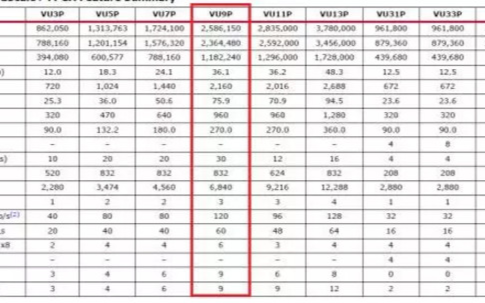

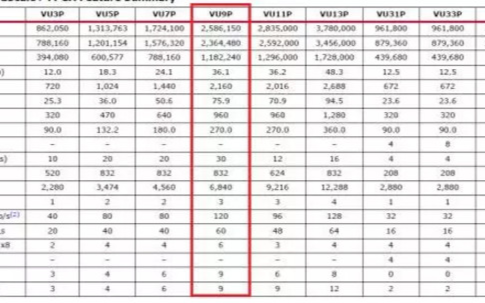

2053 在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 548

548

FPGA 如何估算程序所需的资源?是不是要把输出接到FPGA的PIN上后build,才算是程序所需的资源?因为我有个比较复杂的程序,没有output到FPGA上,LUT使用为8000+一旦output到FPGA上,LUT使用为8W+.是不是此时的LUT使用量才是程序真正所需的?

2017-01-19 09:09:19

下面给大家介绍FPGA LUT的结构

2018-07-09 04:57:10

用于xilinx ML507的Xilinx顶点XC5VFX70TFFG1136 FPGA如何将xilinx LUT作为移位寄存器?什么是xilinx ML507的Xilinx顶点XC5VFX70TFFG1136 FPGA的CLB结构。这个FPGA上有哪些额外的原语?

2020-06-16 16:48:59

`在FPGA中,实现逻辑的基本单元是查找表(LUT)而非基本门电路。目前的FPGA中,单一LE或者Cell通常能实现至少4输入查找表的逻辑功能。4输入查找表可以看成是具有4位地址1位数据的存储器

2018-07-30 18:11:19

所示的内容。Design Summary--------------Logic Utilization:1. FPGA资源利用率Number of Slice Flip Flops: 11,555

2018-08-17 09:44:25

、ROM和FIFO等结构。在实际应用中,芯片内部块RAM的数量也是选择芯片的一个重要因素。5. 丰富的布线资源布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度

2014-08-16 10:32:45

资料来源:http://wenku.baidu.com/link?url= ... ImZCXVVkKhd9oFsSmHC第一部分: 查找表LUT FPGA是在PAL、GAL、EPLD、CPLD等

2017-05-09 15:04:46

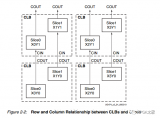

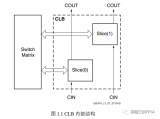

是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多个(一般为4个或2个) 相同的Slice和附加逻辑构成,如图1-3所示。每个CLB模块

2017-05-09 15:10:02

、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多个(一般为4个或2个)相同的Slice和附加逻辑构成,如图1-3所示。每个CLB模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式

2023-05-30 20:53:24

II、Vivado等)、仿真软件(ModelSim等)的使用5、熟悉FPGA设计流程(仿真,综合,布局布线,时序分析)。6、熟练掌握资源估算(特别是slice,lut,ram等资源的估算)。7、同步

2020-10-22 17:08:15

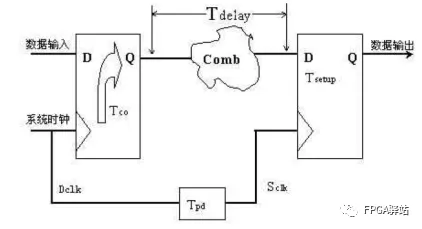

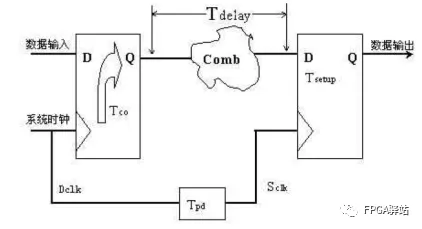

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-25 11:09:06

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-26 14:47:48

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-11-22 10:04:03

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-09 14:34:18

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-08-10 14:51:33

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2020-08-02 10:45:07

设计技巧..............................................................353.8.2 解剖Block SelectRAM内部结构....................................343.8.1 LUT如何配置成组合逻辑电路 揭开门数增加逻辑级数未变 但资源

2012-08-11 11:43:17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35343.8.1 LUT如何配置成组合逻辑电路 揭开 门数增加 逻辑级数未变 但资源占用减少

2017-12-08 14:33:54

嗨,是否有全局实现指令(属性)会强制实现工具将LUT和FF放在单独的片中(对FF或LUT使用单个片)?这是非理想的,也是我所知道的资源浪费......但我正在开发耐辐射设计,并且希望将FPGA的所有

2018-10-29 11:48:56

你好。我正在写一篇技术论文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的资源。资源可以是晶体管数量,栅极数,芯片面积大小等等。我在一个网站上听说LUT需要2.5倍的“FPGA门”,但

2019-02-27 13:49:58

你好,当我在原理图视图中单击LUT时,它会按预期显示逆变器。但我想知道它是通过逆变器在Xilinx FPGA上实现还是实际上原理图不等同于FPGA的真相?谢谢,Ĵ以上来自于谷歌翻译以下为原文Hi

2019-01-29 09:22:50

PAR报告中的“占用切片数量”与完全使用的LUT-FF对之间是否存在任何关系。例如,有两种设计使用相同数量的LUT和FF(以及其他资源) ),是否具有较大的完全使用LUT-FF比率较小的“占用切片数量

2018-11-01 16:11:30

Slice包含4个LUT,因此Slices可用于最多4个功能块。但是为什么64位Init值设置Slice的所有4个LUT的功能(在下面的例子中标记为红色)总是在切片的每个LUT实例中完全改变,而

2019-03-08 12:03:30

大家好,如果我想使用spartan 6 FPGA实现简单的“和”门,请说。我理解“和”门将被模拟到查找表中。有人可以对此有所了解吗?和门真值表是否被移植到LUT?LUT中是否有pmos和nmos

2019-08-09 09:16:35

用于Virtex 6设计的可重配置LUT(CFGLUT)可能被封装到FPGA的输出逻辑OLOGICE1而不是SLICEM上的LUT。我的设计涉及使用存在于与CFGLUT相同的片中的FF(用于流水线

2018-10-22 11:04:46

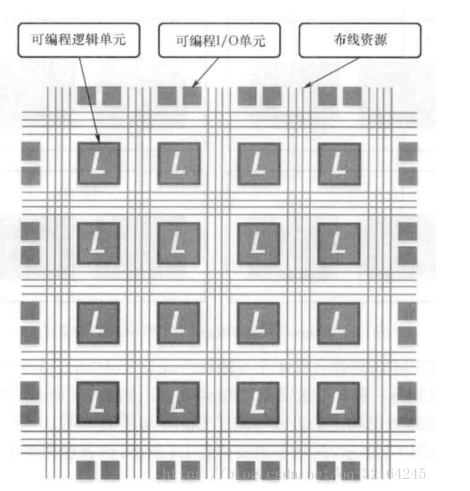

前言FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元(IOB)基本可编程逻辑单元(configurable logic block,CLB) 完整的时钟管理嵌入块式RAM丰富的布线资源内嵌

2021-07-26 06:54:01

或2 个)相同的Slice 和附加逻辑构成,每个CLB 模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM 和分布式ROM。3. 数字时钟管理模块(DCM)业内大多数 FPGA 均提供

2012-03-08 11:03:49

`FPGA的逻辑单元_CLB_项目代码文件`

2021-03-31 11:18:02

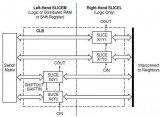

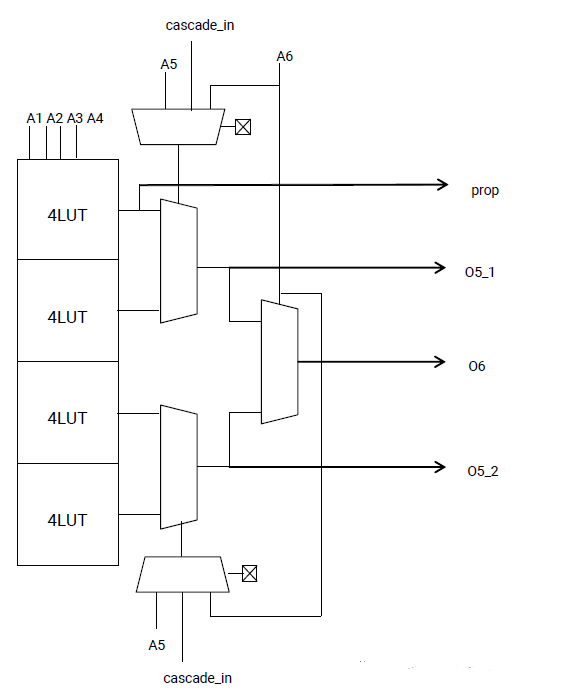

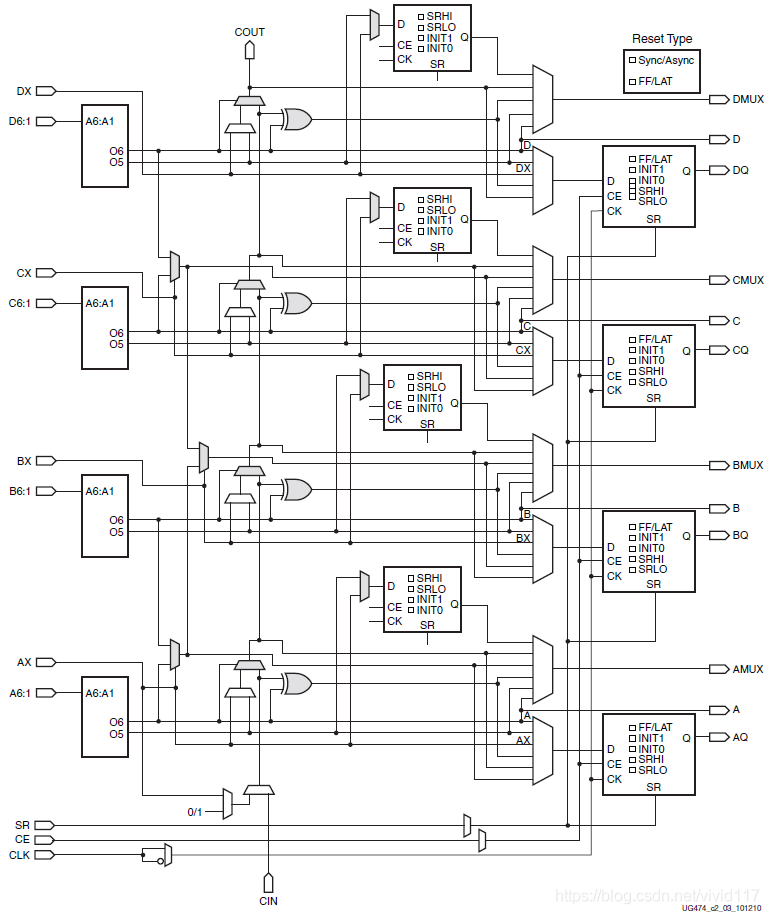

LUT:(look up table) 查找表今天我要讲的与FPGA CLB相关的第一节LUT。根据上一节课的课程大纲,讲CLB应该是讲SLICEL(SLICEM)。不过当我打开用户手册,看了一下

2021-07-29 08:13:55

... the LUT5_L specifies that the only connections from the LUT5 is within a slice or CLB". I'm

2018-10-17 14:26:28

嗨朋友我是Xilinx FPGA的新手,我在Altera FPGA上工作了很长时间。我正在使用Spartan 6,目前正在阅读有关Spartan 6 CLB架构详细信息的CLB配置u384手册。我

2019-08-08 07:13:38

+ 2FF? Or does this mean each slice have 4 pairs of LUT Flip Flop?Thanks,

2018-10-23 10:21:12

关于FPGA芯片资源介绍不看肯定后悔

2021-09-18 08:53:05

嗨,我可以在Virtex-5的任何片中实现CFGLUT5原语,还是仅限于SLICE_M中的LUT?谢谢,Hooman

2020-05-28 06:32:38

一、查找表LUT就是查找表,对于4输入的LUT而言,实际上就是4位地址位,一位数据位的存储器,能够存储16位数据,所以我们在FPGA设计中可以用LUT组建分布式的RAM。这样也可以解释我们在设计中

2021-07-28 08:42:17

在PlanAhead中的一个Slice中发现了LUT6实例的BEL位置的差异FPGA编辑器(由于没有放置FF,因此额外路由的成本会再次进入Slice适当)。一个简单的例子:我定义 LUT1 BEL

2020-06-11 15:18:53

是两片,都在同一个CLB中。弹跳的红线跨越是失败的道路。正如你可以看到从下面的4条路线切片都有一个3的扇出,一个用于上部切片中的每个LUT它路由到。所以你在截图中看到的是12条彩色路径总数,其中只有1个

2018-10-09 15:31:53

资源组成的可编程逻辑,用于实现高密度逻辑,被称为现场可编程门阵列(FPGA)。FPGA也称为可编程ASIC,由可配置逻辑块(CLB)、IO块(IOB)和可编程互连组成。现代FPGA甚至包括乘法器

2022-10-27 16:43:59

我正在使用vertex fpga来实现我的设计。我可以写一个约束文件来为我的设计选择特定的CLB / CLB。谢谢以上来自于谷歌翻译以下为原文i am using vertex fpga

2019-07-18 07:51:49

喜据我所知,有些xilinx FPGA具有DSP Slice(DSP48E)。在fpga设计摘要中,我看到切片寄存器,切片LUT,占用切片等以及DSP48E的单独行。我的问题是 - 1)DSP48E

2019-04-04 06:36:56

(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析

2019-06-17 09:03:28

组成。切片成对分组,并按列排列。设备中 clb 的数量根据供应商和设备家族的不同而不同。例如,Xilinx make Spartan 3E FPGA 包含四个切片。每个片由两个 lut 和两个存储元素

2022-04-03 11:20:18

fpga:Spartan-6 xc6slx150-3fgg484我在资源密集型处理系统中使用了几百个8位加法器,因此资源使用很重要。用于加法器减法器的核心生成器为具有2个8位输入和8位输出,0延迟

2019-04-03 15:55:35

嘿,为了在Zynq设备上对一种算法的不同实现进行简单比较,我想为每种实现的资源使用创建一个指示符,例如CLB的使用。因此,获得基本元素CLB,DSP48E1和BRAM36K的面积指标会很好。在

2020-07-25 11:04:42

Xilinx 公司的 FPGA 器件中,CLB 由多个(一般为 4 个或 2 个) 相同的 Slice 和附加逻辑构成,如图 1-3 所示。每个 CLB 模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为

2020-05-01 07:30:00

`Xilinx片子一般从65nm工艺以上就使用6输入LUT,新器件的Slice包含4个6输入LUT和8个寄存器等。Cyclone V的片子是6输入LUT吗?如果是的话,每个Cyclone的基本逻辑

2016-10-26 10:58:05

在使用ISE进行实现过程中,占用slice的资源较多,如图中所示,想用unrelated logic部分,期望能够将slice资源均衡使用,而折腾了好久,改了好多综合、map等的设置,可都

2015-02-28 14:55:25

嗨,我正在使用Kintex-7 XC7K160T-2FFG676C设备和Vivado 2013.4。由于我无法通过资源利用来实现我的设计,因此我附加了合成后生成的资源利用率报告。根据综合利用率报告

2020-08-05 12:48:02

此课程将教会你:1)描述Spartan-6 和Virtex-6 FPGA的6输入LUT和CLB建设的所有功能;2)指定Spartan-6 和Virtex-6的CLB资源和可用的Slice配置;3)定义可用的RAM和DSP资源块;4)正确设计I/O块和S

2010-12-14 15:09:48 0

0 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 在基于FPGA的商用设计中,设计师通常会将查找表(LUT)的资源占用率上限设置为80%左右,以便为未来升级和功能改进留有资源,并可让时序收敛更容易。余下约20%的空閒LUT留下了空余的佈

2011-08-21 18:01:51 2562

2562

一个写写代码,调调时序的小工程师的级别。我想,这应该不是我们所有年轻人的一个追求。 1.1 CLB的初探 首先CLB的最基本资源分为两种,一种是实现组合逻辑资源功能的,一般称为LUT。XILINX的LUT是6输入查找表。一种是Flip-flop,也就是经常听课大家听说的FF,我就

2017-02-08 10:10:34 214

214

7系列FPGA是Xilinx新推出的基于28nm工艺的FPGA,其中包含三个系列:Artix、Kintex和Virtex。因项目要使用kintex7为平台做设计,需要对其内部结构做了研究,首先从CLB(Configurable Logic Block)开始

2017-02-10 16:13:38 5090

5090

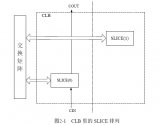

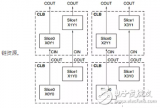

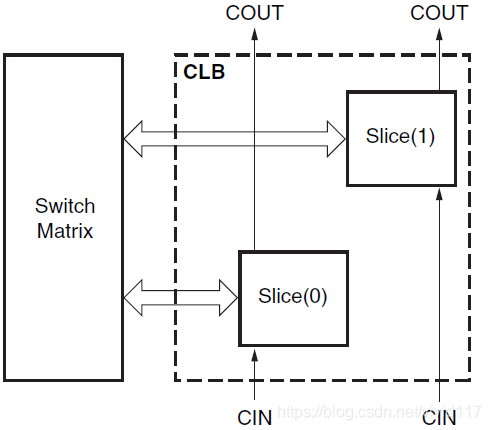

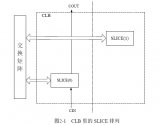

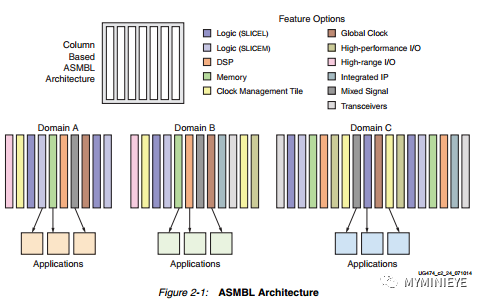

Spartan-6每个CLB模块里包含两个SLICE。CLB通过交换矩阵和外部通用逻辑阵列相连,如图2-1和图2-2所示。底部的SLICE标号为SLICE0,顶部的SLICE标号为SLICE1。两个SLICE没有直接连接。

2017-02-11 09:53:11 741

741

在赛灵思Spartan-3、3E等系列的FPGA中,其逻辑单元CLB中一般含有不同数量的单端口RAM(SRAM)或者双端口RAM(DRAM),这里的“单”或者“双”是由我们开发人员定义的。

2017-02-11 13:56:11 6348

6348

插,以模拟更大容量的LUT。这样,您就可以实现比1000 字 LUT更高的数值分辨率。此外,通过这种方法,仅需 1 个 BRAM、1个嵌入式乘法器(或DSP48),以及少数几个CLB芯片便可实施控制逻辑,因此LUT的使用成本变得更加合理化。而且,从信噪比的角度来看,其数值精度也是非常让人满意。

2017-11-25 12:05:01 2993

2993

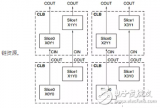

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成。

2018-05-10 11:43:00 25053

25053

FPGA中的基本逻辑单元是CLB模块,一个CLB模块一般包含若干个基本的查找表、寄存器和多路选择器资源,因此FPGA中的逻辑表达式基于LUT的。

2018-07-28 09:58:01 64941

64941

第二种Slice叫SLICEM,电路结构如下。除了LUTS与SLICEL的LUTS不同之外,其余结构都一样。这就是SLICEM与SLICEL之间的区别,利用SLICEM的LUTS还可以构成RAM,ROM,以及Shift Registers(移位寄存器)。

2018-10-18 17:04:41 10485

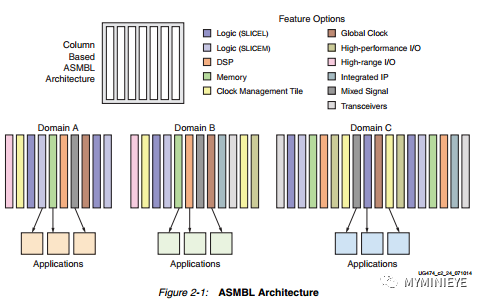

10485 现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

2018-10-22 11:00:43 5270

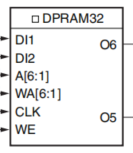

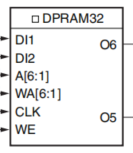

5270 一个SLICEM里面有4个LUT,他们可以组合得到多种大小的RAM。首先就是四端口的32x2bits的RAM,支持一次性读写2bits,原理如下图。四个LUT的写数据端口DI1,DI2,写使能WE,写地址WA共用,称为写控制信号共用。读地址A分别控制。

2018-10-30 10:28:40 10404

10404

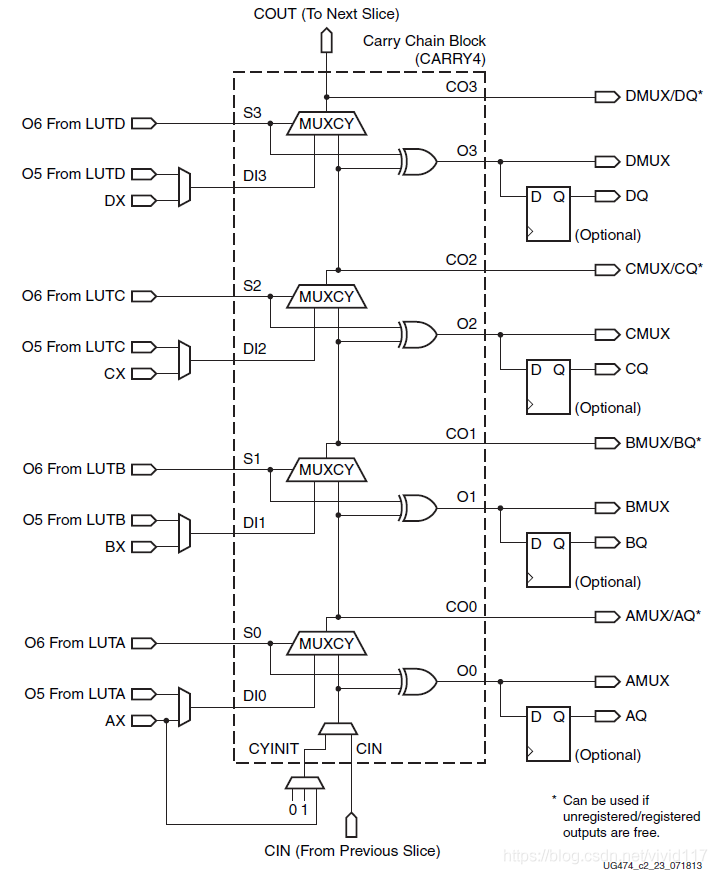

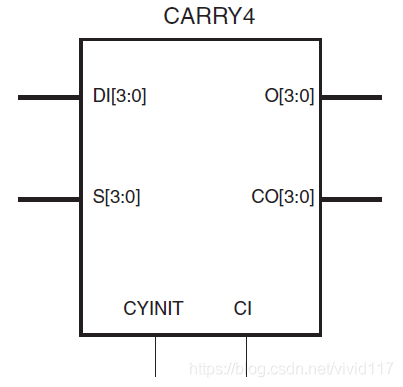

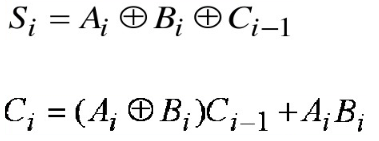

本视频介绍了7系列CLB架构,包括:LUT,触发器,专用多路复用器,进位链和其他资源。

2018-11-27 06:39:00 3290

3290 本视频介绍了7系列FPGA的DSP Slice功能。

此外,还讨论了Pre-Adder和Dynamic Pipeline控制资源。

2018-11-26 06:02:00 6700

6700 Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 12305

12305

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。 在用Vivado建立

2019-09-15 12:21:00 4826

4826

一个CLB包含两个Slice,两个Slice分别位于独立的列,有各自的进位链,他们相互不连接。每个CLB连接到一个Switch matrix上已完成布线。CLB中底部的Slice为Slice0,上部的为Slice1。

2019-06-18 08:00:00 0

0 管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。

2019-06-28 14:34:07 3703

3703 CLB(Configurable Logic Block):FPGA最基本的组成单元,可以实现基本的组合逻辑和时序电路。其中,LUT(Lookup Tables)是实现组合逻辑的部分,可以实现n个输入的任意组合逻辑运算(不同型号的FPGA有所不同,下图的例子中为6个输入)。

2019-09-27 15:18:06 7663

7663

这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数。

2019-11-02 10:56:01 1588

1588

结构配置到FPGA具体的哪个位置。需要说明的是,FPGA里任何硬件结构都是按照横纵坐标进行标定的,图中选中的是一个SLICE,SLICE里面存放着表和其他结构,它的位置在X50Y112上。不同的资源的坐标不一样,但是坐标的零点是公用的。 在FPGA里布局需要考虑的问题是,如何将这些

2020-10-25 10:25:31 7659

7659

在使用 FPGA 过程中,通常需要对资源做出评估,下面简单谈谈如何评估 FPGA 的资源。 FF 和 LUT 的数目:这个在写出具体代码之前,初学者通常没法估算,但资深 FPGA 工程师会估算

2020-12-28 07:59:00 8

8 在FPGA中,实现逻辑的基本单元是查找表(LUT)而非基本门电路。目前的FPGA中,单一LE或者Cell通常能实现至少4输入查找表的逻辑功能。

2020-12-29 17:27:22 14

14 SRL(移位寄存器)资源,在FPGA中都有,不过是叫不同的名字。Xilinx FPGA内部的LUT有个特殊功能,就是可以配置成可变长度SRL。

2020-12-31 16:45:35 8

8 DDR3。 2.FPGA架构设计问题 我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各模块之间的数据交织情况,这样可以避免

2021-01-07 10:15:31 4645

4645

在Versal ACAP中,同一个CLB内同一列的LUT是可以级联的,这是与前一代FPGA UltraScale+系列的一个显著不同点。这里我们先看看Versal中LUT的结构,如下图所示(图片来源

2021-03-27 09:52:08 2711

2711

面积通常指一个设计消耗FPGA/CPLD的逻辑资源的数量,通常用可消耗的FF(触发器)和LUT(查找表)来衡量。速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求

2022-02-16 16:21:28 855

855

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成。

2022-04-24 14:48:55 3407

3407 这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数。

2022-10-17 17:50:17 637

637 FPGA是一种数字集成电路芯片,名称为“现场可编程逻辑门阵列”FPGA的一项重要特点是其可编程特性,即用户可通过程序指定FPGA实现某一特定数字电路,FPGA的的组成有CLB,IOB,可编程互联资源,SRAM,DSP,时钟管理模块,CLB内包含有Filp-Flop和LUT等,可实现某些组合或时序逻辑电路;

2023-03-21 14:01:05 412

412 的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相同的SliceL或则一个SliceL和一个SliceM构成。每个Slice不仅可以用于实现组合逻辑、时序逻辑。其中,SliceM还可以配置为分布式RAM和分布式ROM

2023-03-21 14:14:41 554

554

我们知道FPGA由LUT、IO接口、时钟管理单元、存储器、DSP等构成,我觉得最能代表FPGA特点的就是LUT了。当然不同厂家、同一厂家不同阶段FPGA的LUT输入数量是不同的,随着技术的发展,LUT的输入数量也在增加。

2023-05-25 09:29:18 2444

2444

首先开门见山的回答这个问题——LUT的作用是 **实现所有的逻辑函数** ,也就是类似于计算Y=A&B+C+D之类的算式结果!

2023-06-28 10:56:39 1615

1615

在7系列FPGA中,将近2/3的SLICE是SLICEL,其余的是SLICEM[1],也就是说,FPGA内2/3的资源在bitstream文件下载后,其逻辑功能就无法更改了,除非修改代码并生成新的bitstream文件。

2023-08-26 14:18:37 1039

1039

FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 949

949

电子发烧友App

电子发烧友App

评论