1. 初识XILINX 初识XILINX,是PYNQ-Z2。当时刚学完学校的数字电路课程,对FPGA并不了解,学校课程也仅仅是用VHDL验证了一些基础的FPGA实验,例如生成一个n进位序列

2020-11-05 15:56:42 4204

4204 设计来满足各种约束 用不用的指令来探索多个HLS解决方案 2.实验内容 实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench

2020-12-21 16:27:21 3153

3153 InTime。 前言 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着从 C 转化得到 RTL 基本不可能。其实,使用 FPGA 工具设置来优化设计可以最

2020-12-20 11:46:46 1416

1416

的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 2880

2880

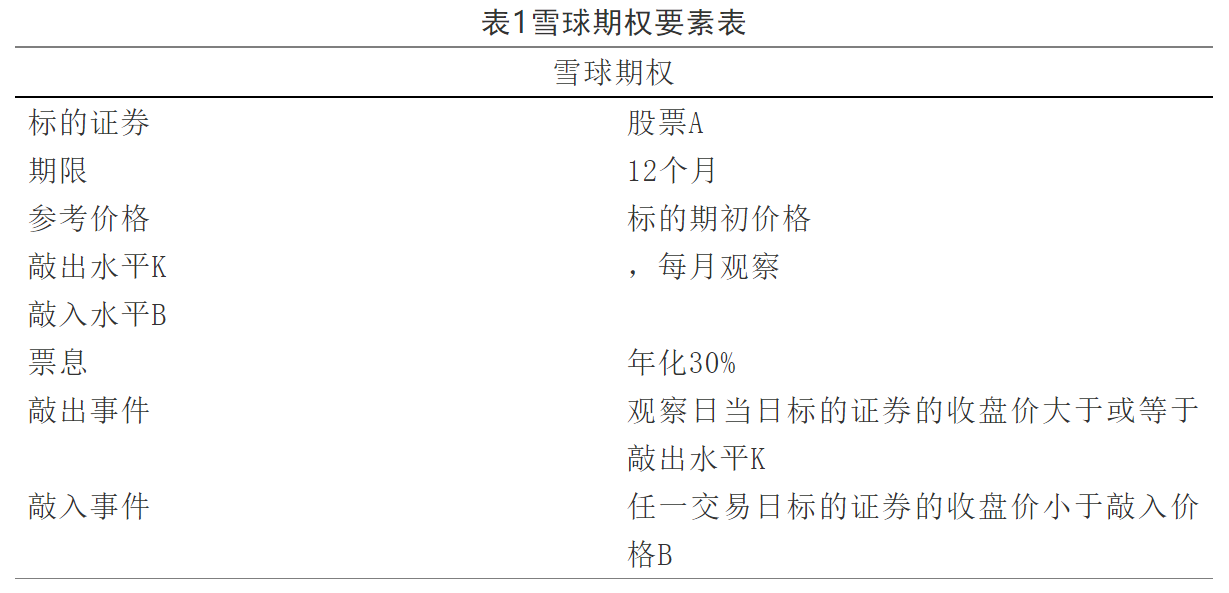

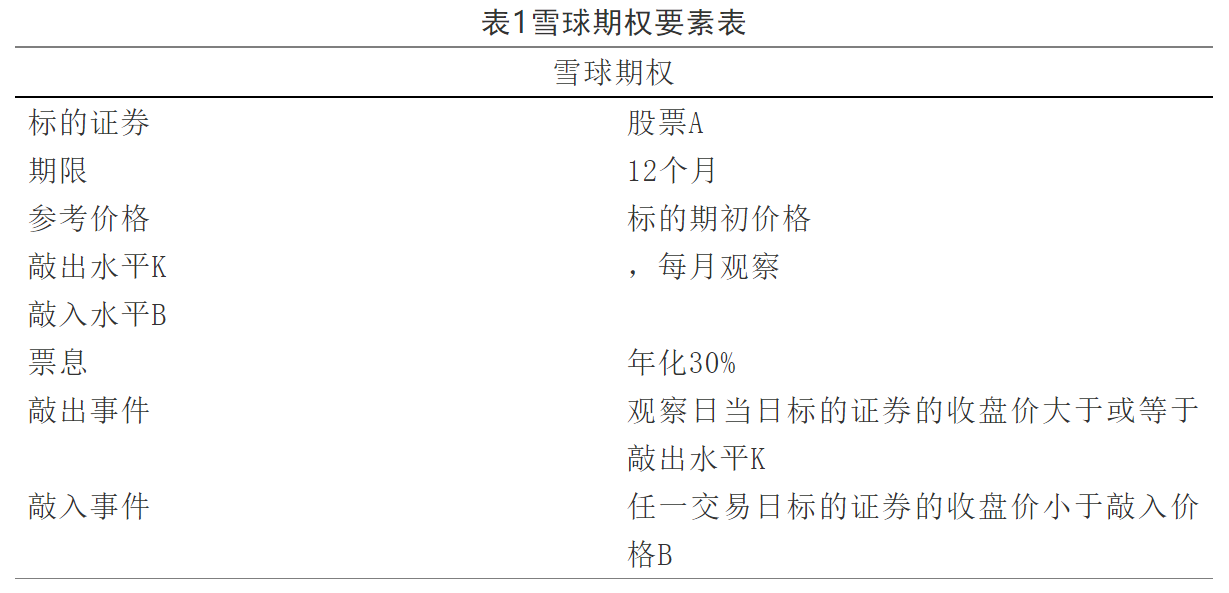

本文为解决基于C++的传统定价程序带来的处理时间长、延迟高、处理速率低的问题,提出并实现了一种基于FPGA的并行流水线计算处理设计,能够完成对雪球期权的定价功能,并使用HLS开发模式对设计进行了实现。

2022-08-02 08:03:31 1050

1050

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视为本科生的作业。在这里,我将通过这个例子来展示在 HLS 中实现它是多么容易和有趣。

2023-11-20 09:48:58 273

273

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视为本科生的作业。在这里,我将通过这个例子来展示在 HLS 中实现它是多么容易和有趣。

2023-11-20 09:50:59 311

311

目录HLS案例开发2_led_flash案例|基于FPGAKintex-7开发板前 言案例功能HLS工程说明编译与仿真IP核测试更多推荐前 言本文led_flash案例是基于创龙科技TLK7-EVM

2021-02-24 19:23:30

FPGA为什么是实现绿色搜索技术的关键?

2021-05-08 07:47:03

在上一讲已经知道了 FPGA就实现技术是可以分成三种不同 FPGA 的结构特点、实现的机理,这三种 FPGA 分别是基于 SRAM 技术、基于反熔丝技术、基于 E2PROM/FLASH技术。就电路结构...

2021-07-30 06:39:06

重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或 Block

2022-09-07 15:21:54

你好, 我想在HLS中实现反向输入和自然输出算法。 但是,结果始终是: 我的代码是:void reverse_fft(compnum xin [FFT_SIZE]){ const int LH

2019-03-06 12:48:35

HLS感知C代码生成,将无缝切换到HLS工具,最后一步实现使用SLX进行FPGA加速的端到端自动化流程。HLS是我们应该善待的朋友,它也不应该承载我们错误的期望。为了使HLS成为一个方便且不可或缺的工具

2021-07-10 08:00:00

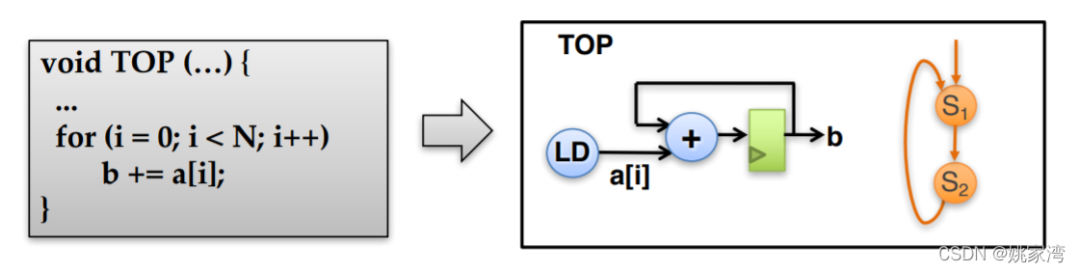

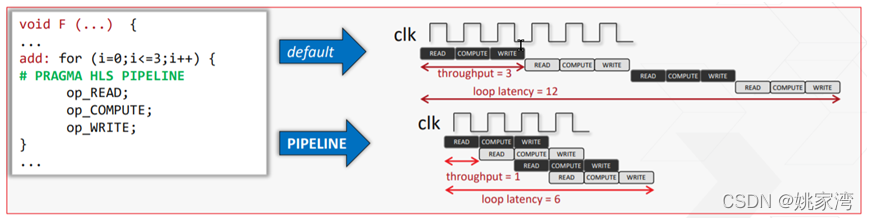

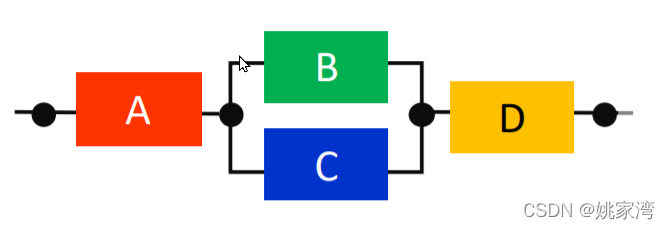

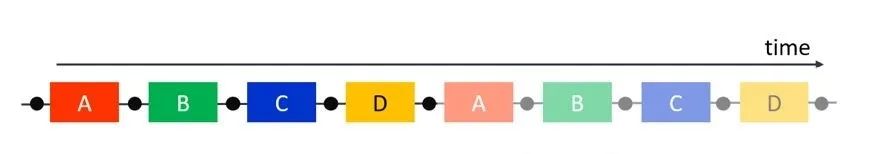

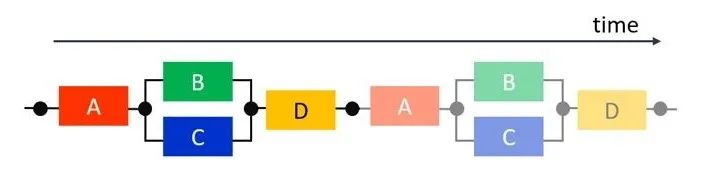

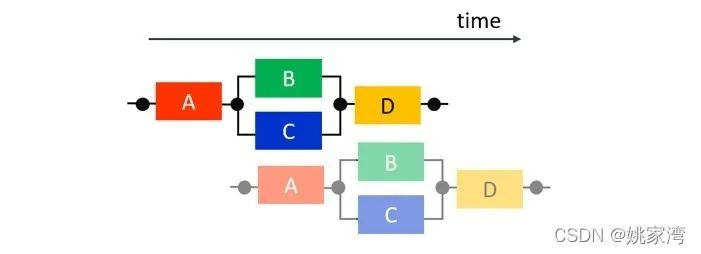

流水线指令

pragma HLS pipeline

通过流水线提高性能是计算机架构设计的8个伟大思想之一,不管是硬件设计还是软件设计,流水线设计(pipeline)都能够用更多的资源来实现高速

2023-12-31 21:20:08

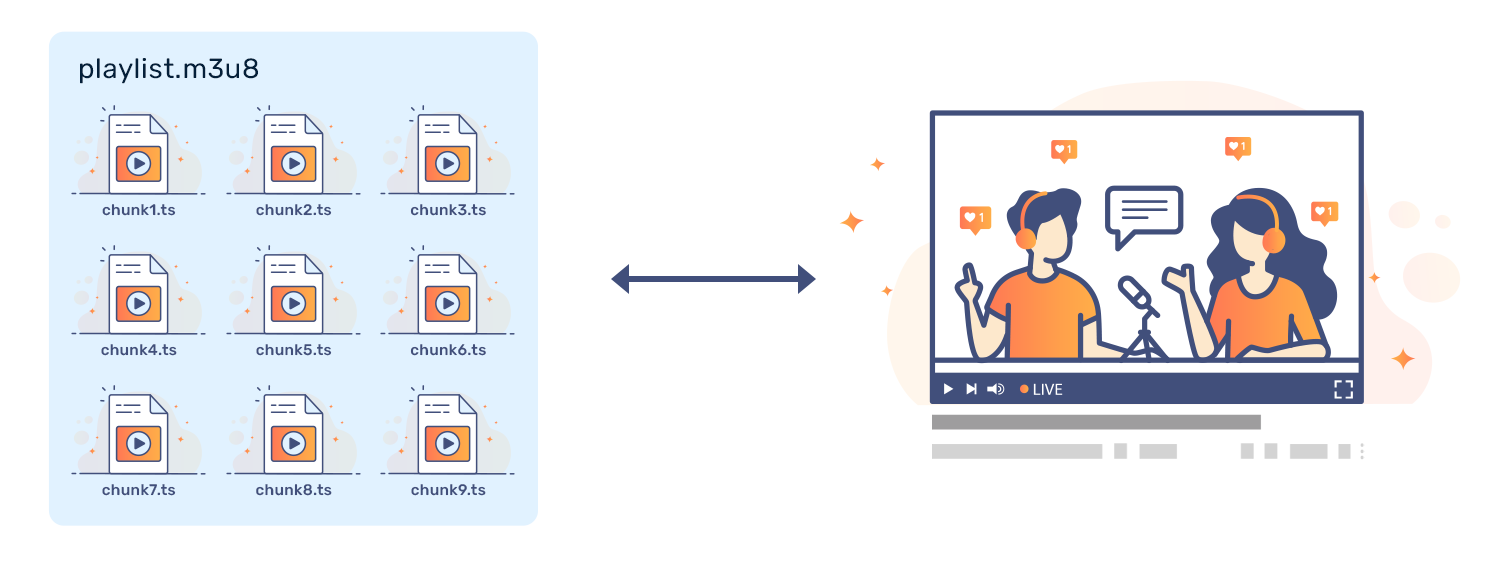

文件。 把上述2个技术性很强的概念表述翻译下。就是说H5是一种HTML的新标准,这种新标准支持原生的video标签和video控件。因为video控件标签又支持HLS协议播放。 所以得以实现在手机移动

2017-06-01 14:48:07

的RTL代码。在ISE或者Vivado开发环境中做RTL的集成和SOC/FPGA实现。2.2.1 VivadoHLS视频库函数HLS视频库是包含在hls命名空间内的C++代码。#include

2021-07-08 08:30:00

多个HLS解决方案2.实验内容实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。...

2021-11-11 07:09:49

WiBro系统是由哪些部分组成的?WiBro技术中的切换机理是什么?WiBro覆盖范围和传输速度怎样?WiBro系统有哪些业务?

2021-05-26 07:19:46

本帖最后由 FindSpace博客 于 2017-4-19 16:57 编辑

在c simulation时,如果使用gcc编译器报错:/home/find/d/fpga/Vivado_HLS

2017-04-19 16:56:06

HLS感知C代码生成,将无缝切换到HLS工具,最后一步实现使用SLX进行FPGA加速的端到端自动化流程。HLS是我们应该善待的朋友,它也不应该承载我们错误的期望。为了使HLS成为一个方便且不可或缺的工具

2021-07-06 08:00:00

)对正点原子FPGA感兴趣的同学可以加群讨论:8767449005)关注正点原子公众号,获取最新资料第一章HLS简介为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速

2020-10-10 16:44:42

割。二值化的方法有很多,其中自适应二值化(OTSU)是图像二值化最常用的一种算法。本章我们将在HLS中实现图像的自适应二值化。本章包括以下几个部分:1111.1简介11.2实验任务11.3HLS

2020-10-14 16:04:34

)对正点原子FPGA感兴趣的同学可以加群讨论:8767449005)关注正点原子公众号,获取最新资料第四章呼吸灯实验在前面两个实验中我们学习了如何通过Vivado HLS工具来生成带有一个

2020-10-10 17:01:29

HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或

2022-09-09 16:45:27

其主要的退化机理。【关键词】:后驱动技术;;故障注入;;退化机理【DOI】:CNKI:SUN:IKJS.0.2010-03-027【正文快照】:故障注入技术是装备测试性验证研究的重要方面,是测试性/B

2010-04-22 11:29:19

我想知道基于FPGA出租车计价系统实现的技术框架是什么?

2016-04-26 10:36:46

基于FPGA的交织编码技术研究及实现中文期刊文章作 者:杨鸿勋 张林作者机构:[1]贵州航天电子科技有限公司,贵州贵阳550009出 版 物:《科技资讯》 (科技资讯)年 卷 期:2017年 第

2018-05-11 14:09:54

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

PCM编码原理与规则是什么?如何利用FPGA编程技术实现PCM编码原理?机场监视监控网络中低速接入应用

2021-04-15 06:38:46

如何利用Freeze技术的FPGA实现低功耗设计?

2021-04-29 06:27:52

嗨〜 如何在HLS 14.3中编写pow功能? HLS 14.3不支持exp和pow功能。我在我的代码中写了“#include math.h”。但是,它不起作用。 另外,我想知道C代码中

2019-03-05 13:40:09

怎么实现基于FPGA技术的智能导盲犬设计?

2021-05-08 07:37:31

相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。Synphony HLS解决方案架构图

2019-08-13 08:21:49

我的目标是实现一个给定的C算法是一个FPGA。所以,我最近得到了一个Zedboard,目标是实现该算法是PL部分(理想情况下PS中的顶级内容)。我在FPGA领域和编写VHDL / Verilog方面

2020-03-24 08:37:03

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

2017-01-16 09:22:25

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

将Vivado HLS与OpenCV库配合使用,既能实现快速原型设计,又能加快基于Zynq All Programmable SoC的Smarter Vision系统的开发进度。 计算机视觉技术

2014-04-21 15:49:33

了解并掌握DSP中EMIF接口的使用方法;4. 在现有的FPGA数字信号处理硬件平台中调试实现数据的收发控制。主要技术指标1. 以太网通信实现TCP/IP协议,通信方式为半双工或者全双工;2. 以太网

2014-03-09 16:36:25

求助FM调制器的FPGA实现,对FPGA这些完全不了解,在网上看可以用DDS技术实现FM的数字调制,就在书上按照步骤先做了产生正弦波分频模块寻址模块数据存储模块,但编译不能通过,也不知道该怎样进行频率调制,请问该怎样实现频率的调制,请问有人写过频率调制的verilog代码吗,急求,谢谢

2019-03-16 11:43:26

您好,我目前正在尝试使用Vivado HLS在FPGA上合成加密算法。我根据需要拆分了C ++代码并包含了一个测试平台,但是当我尝试模拟代码时,我得到一个错误,说找不到测试平台。我附上了错误图片和项目档案,希望有人能帮我找到解决方案。谢谢!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

2018-12-27 10:57:49

EMC 中屏蔽技术的机理和分类

本文结合电磁兼容和屏蔽技术的基础知识,阐述了EMC 中屏蔽技术的机理和分类。对工程应用具有很大的实用价值和指导意义。

屏蔽

2010-02-22 14:33:56 29

29 基于对FPGA系统失效机理的深入分析, 提出了软件测试技术在FPGA测试中的应用, 并分析了其可行性; 通过对比FPGA与软件系统的异同, 归纳出FPGA特有的测试要求,从而在软件测试技术的基础

2011-09-29 17:41:21 65

65 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 基于FPGA技术的数字相关器的设计与实现

2016-12-16 22:23:00 14

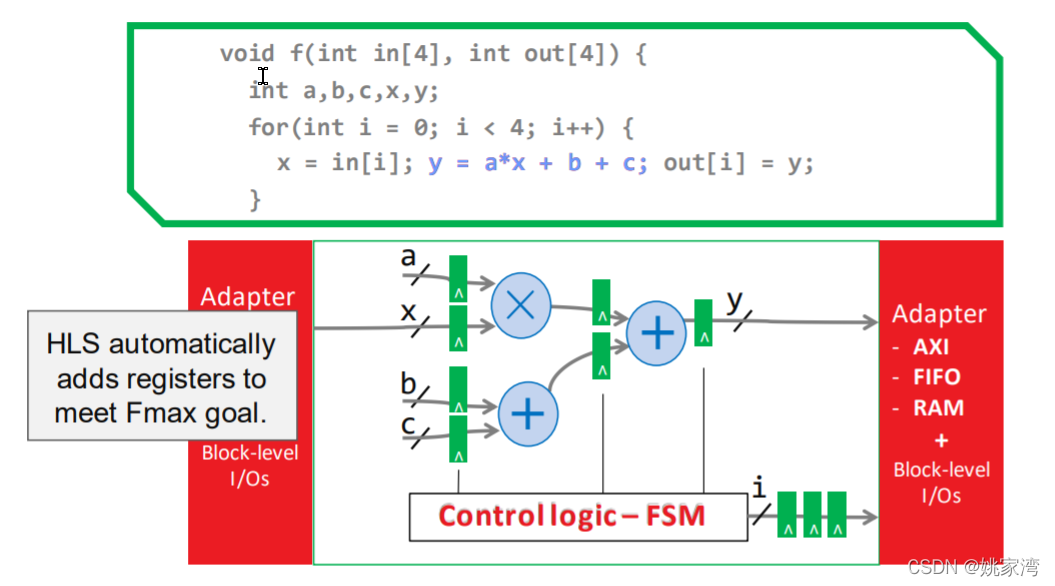

14 高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

HLS非常适合一些信号处理模块的快速实现。下面是一个实际的例子,由于使用了HLS,非常高效的就完成了模块的rtl的实现,比用手工coding节约了大量的时间! 需求描述: 在一个项目里面,需要

2017-02-08 02:33:36 623

623

Interface:内存访问型的端口协议 接下来的几章,我们重点介绍下AXI接口类型如何在HLS中实现,首先看Lite端口: AXI-Lite端口的实现 使用Vivado HLS的AXI-Lite端口,可以实现: 把多个port打包到一组AXI-

2017-02-08 03:27:11 475

475

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口

2017-02-08 03:29:11 544

544

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 AXI FULL端口的实现

2017-02-08 03:35:34 776

776

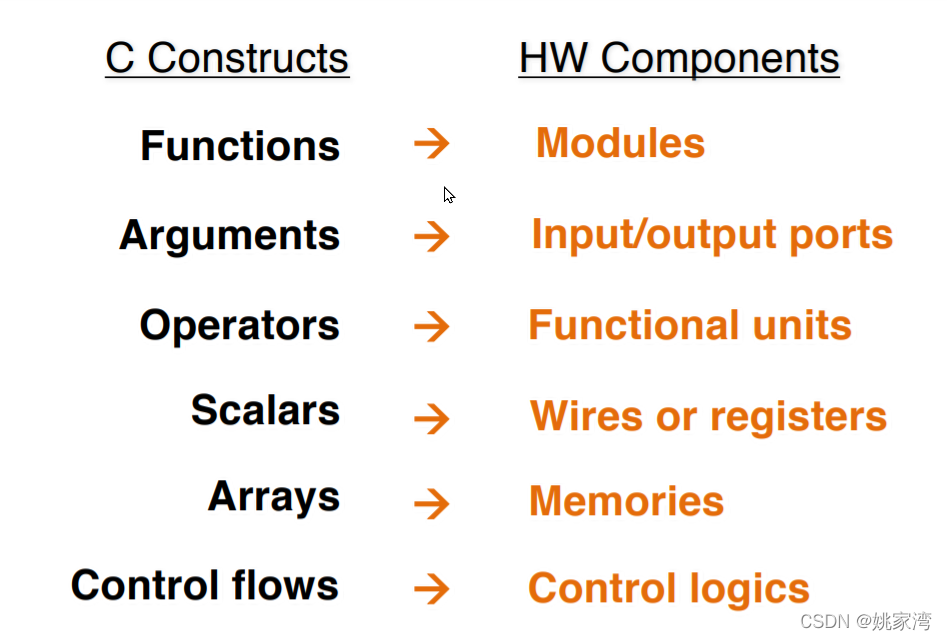

相信通过前面5篇fir滤波器的实现和优化过程,大家对HLS已经有了基本的认识。是时候提炼一些HLS的基本概念了。 HLS支持C,C++,和SystemC作为输入,输出为Verilog(2001

2017-02-08 05:23:11 674

674

里sobel edge detection的例程。 wiki Top Function 这里不同于xapp1167,直接调用hls::cv的库函数,sobel边缘提取算法是重新实现的,更方便了解hls的算法实现

2017-02-08 10:12:11 458

458 高层次综合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA设计工具,它能让用户通过编写C/C++等高级语言代码实现RTL级的硬件功能。随着这款工具

2018-07-14 06:42:00 5868

5868 Luke Miller并非一开始就是HLS(高层次综合)的倡导者。在使用早期的工具版本的时候,他似乎有过一些糟糕的经历。

2017-02-10 18:48:59 3334

3334

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 1647

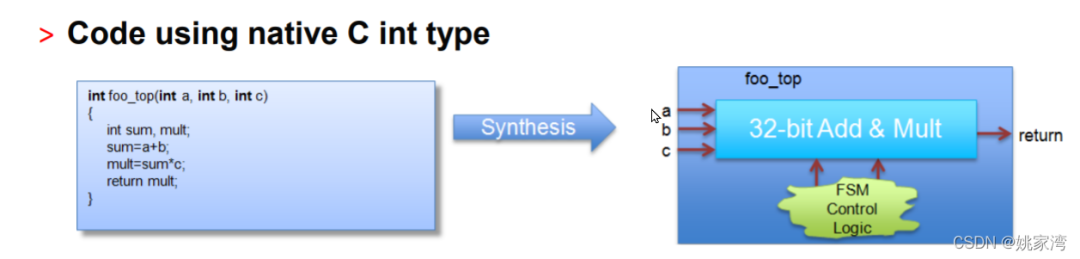

1647 通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解

2017-11-18 12:23:09 2377

2377

1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 摘要:HTTP Live Streaming(缩写是HLS)是一个由苹果公司提出的基于HTTP的流媒体网络传输协议。今天主要以HLS协议为中心讲述它的一些原理。

2017-12-10 09:25:37 54718

54718 对电子元器件的失效分析技术进行研究并加以总结。方法 通过对电信器类、电阻器类等电子元器件的失效原因、失效机理等故障现象进行分析。

2018-01-30 11:33:41 10912

10912 HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

2018-06-04 01:43:00 7171

7171

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS为FPGA流程提供集成化设计与开发环境,率先支持5G无线应用。

2018-08-30 10:09:32 7368

7368 Vivado HLS是Xilinx公司推出的加速数字系统设计开发工具,直接使用C、C++或SystemC开发的高层描述来综合数字硬件,替代用VHDL或Verilog实现FPGA硬件设计[6],实现设计的功能和硬件分离,不需要关心低层次具体细节,具有很强的灵活性,有效降低数字系统设计开发周期。

2018-10-04 10:41:00 7096

7096

作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

2018-11-10 11:01:05 2750

2750 了解如何使用GUI界面创建Vivado HLS项目,编译和执行C,C ++或SystemC算法,将C设计合成到RTL实现,查看报告并了解输出文件。

2018-11-20 06:09:00 3651

3651 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2887

2887 介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构。Xilinx官方文档表示利用HLS进行设计可以大大加速设计进度:

2019-07-31 09:45:17 6232

6232

、7系列FPGA相关文档 正文 0Zynq7000系列概览 1内存占用 1.1 FPGA程序中内存的实现方式 参阅xilinx文档UG998 FPGA并没有像软件那样用已有的cache,FPGA的HLS编译器会在FPGA中创建一个快

2021-04-19 11:12:02 2202

2202

IC技术与故障机理--了解可靠性标准可提高仪表质量

2021-05-18 08:09:39 7

7 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 FPGA的布局布线软件向来跑得很慢。事实上,FPGA供应商已经花了很大的精力使其设计软件在多核处理器上运行得更快。

2022-05-25 09:50:10 959

959 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2857

2857 vivado本身集成了opencv库以及hls视频库了,opencv不能被综合导出为RTL电路,hls视频库的功能有所欠缺,因此引入xfopencv作为既可以被综合导出为RTL电路,也能够实现opencv丰富的功能。

2022-09-09 15:07:05 997

997 这里向大家介绍使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

2022-10-11 14:21:50 1517

1517 电子发烧友网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境

2022-12-02 12:30:02 2570

2570 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2023-01-15 11:27:49 1317

1317 是Vitis HLS。在Vivado 2020版本中替代原先的Vivado HLS, 功能略有差异。 HLS 的机理 简单地讲,HLS采样类似C语言来设计FPGA 逻辑。但是要实现这个目标,还是不容易

2023-01-15 12:10:04 2968

2968 HLS,Http Live Streaming 是由Apple公司定义的用于实时流传输的协议,HLS基于HTTP协议实现,传输内容包括两部分,一是M3U8描述文件,二是TS媒体文件。

2023-04-06 09:29:50 428

428 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 652

652

电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 1

1 在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案

2023-07-07 09:08:14 934

934

在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案,调用HLS中自带的FFT库(hls:fft

2023-07-11 10:05:35 580

580

本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS 工具生成的在 FPGA 部分执行的硬件功能模块。

2023-08-04 11:00:43 335

335

电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

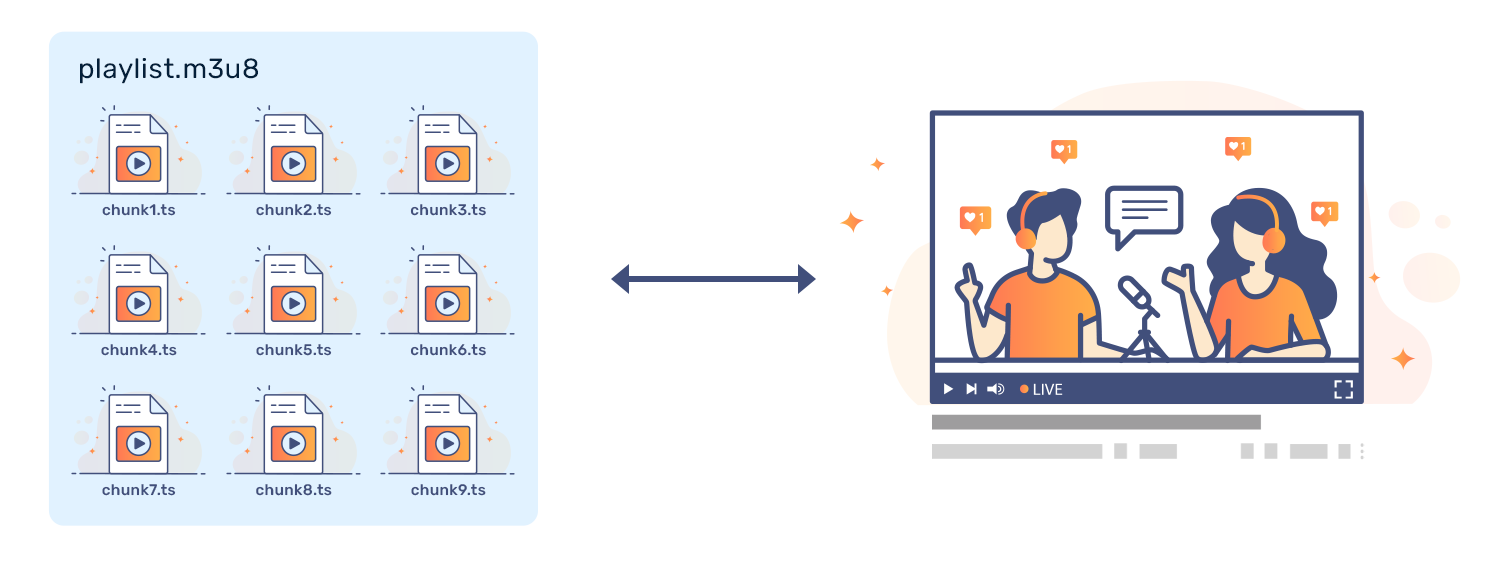

2 Streaming)是Apple开发的标准。此图全面概述了正在运行的HLS直播流: 原则上,该技术为自适应比特率提供多个播放列表

2023-10-09 17:16:54 485

485

电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0

电子发烧友App

电子发烧友App

评论