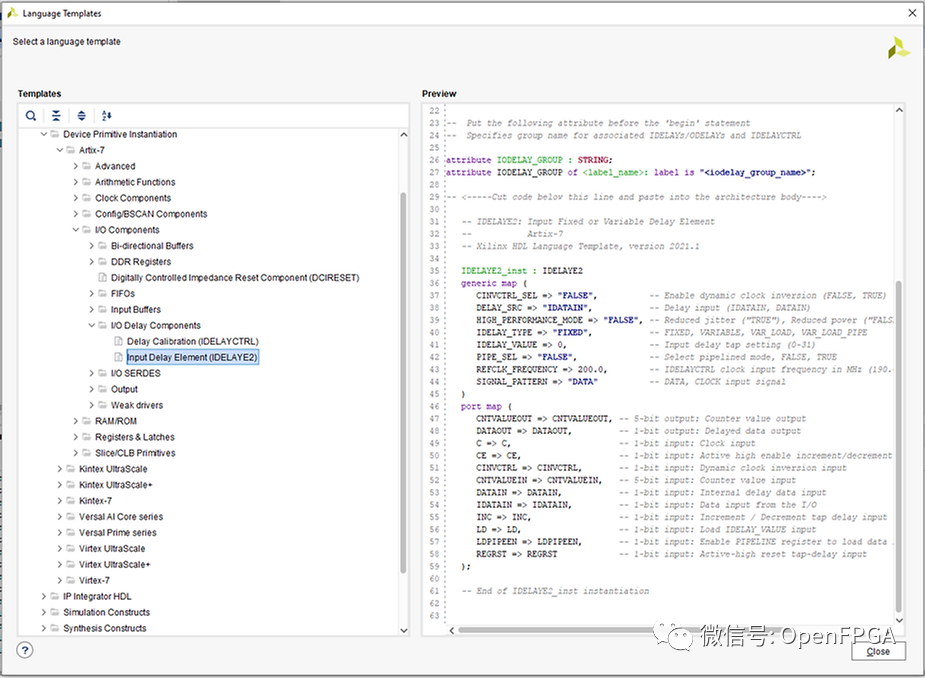

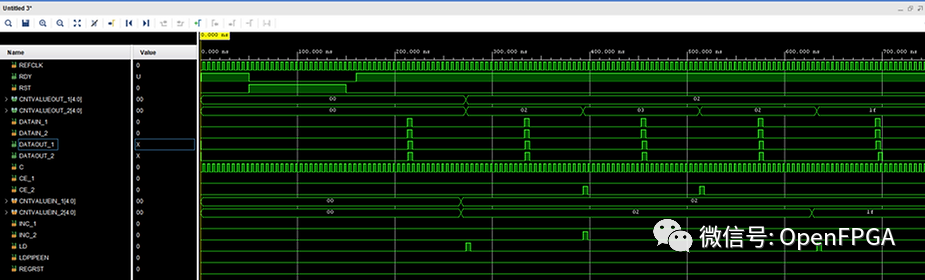

idelay2中按推荐配置,从DATAIN还是从IDATAIN输入区别为是内部延时还是从IO输入,FIXED固定延时,idelay value先输入0,,时钟是200M,其他全部接0。

2020-11-25 14:35:49 9912

9912 ,FPGA生成并向8个摄像机发送26.66MHz时钟,每个摄像机返回320MHz的时钟和12位SDR数据。从转发的26.66MHz时钟生成320MHz时钟并将其用于ISERDES(在所有通道上)应该是

2020-07-24 12:10:42

我有2个时钟输入通过一个支持时钟的IO对(AN19和AN20)进入FPGA。时钟输入具有相同的频率,但不同相。是否可以通过他们自己的IODELAY和BUFIO来分配每个本地时钟网络?我希望一个时钟

2020-05-29 15:52:06

嗨,我正在尝试使用KC705板进行PCIE RC和端点测试。1)我将把PCIE RC控制器IP设计和FPGA PCIE PHY放在FPGA中。2)我将在FPGA中放置另一个PCIE端点控制器IP

2020-07-26 13:06:25

货真价实XILINX、ALTERA 一系列2手FPGA,我们真实库存,货真价实。可提供检测。实验,应用等需求。Q 3618704432淘世宇电子

2019-07-28 17:40:08

。 NIOS2这种软核cpu思路很新颖 废物利用网表中闲置的逻辑门 就可以让FPGA平白无故就多了一块强大的控制器 而不用外接一个mcu。 但FPGA功耗/个头较大 更适合一些设计原型的开发中 或是对尺寸

2018-08-17 09:59:27

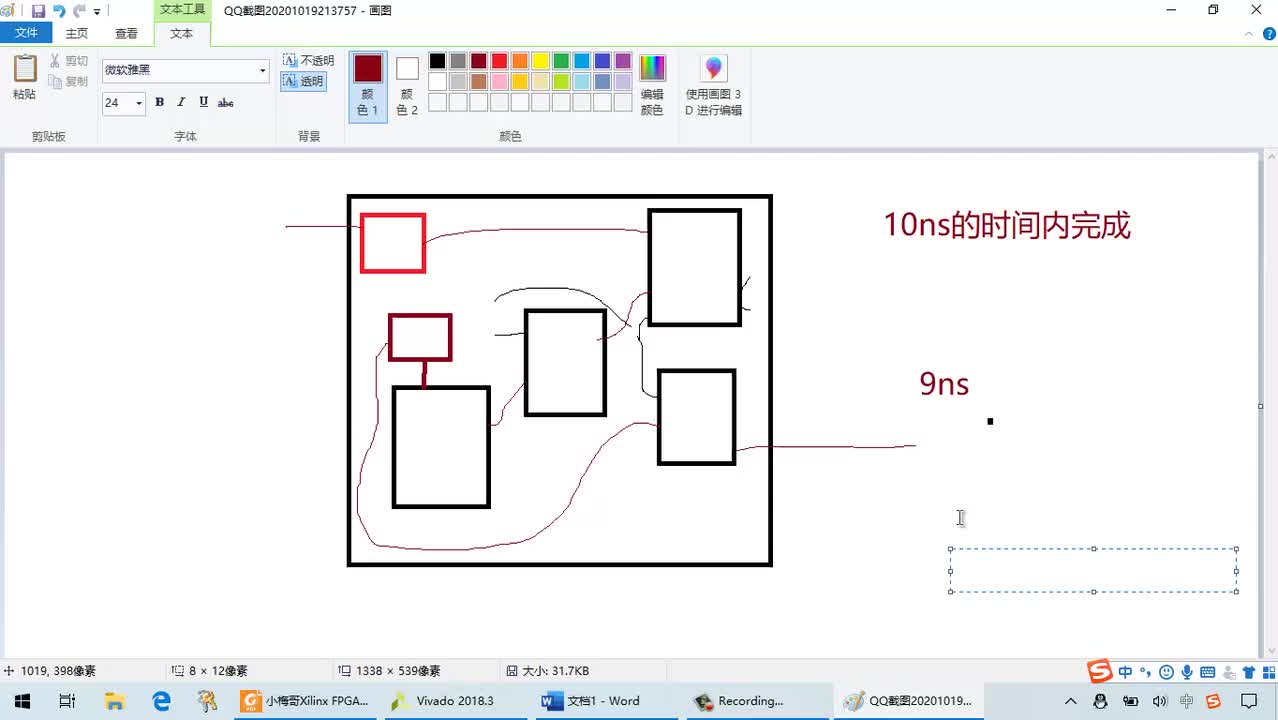

基本的时序分析理论2本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面我们再来看一个例子,如图8.2所示

2015-07-14 11:06:10

FPGA开发全攻略(全,分为上下2部)

2019-03-25 14:44:29

大家好我FPGA应用需要用到8GDDR,目前采用2片4GDDR2,发现一个有趣问题,美光,2GDDR2支持16位,速率可达200M,但美光4G的DDR2只有8位,速率才125M~150MHz。怎么会慢呢?有没有更快的?

2013-06-22 22:02:28

是 IDELAY2 和 ODELAY2 原语。这些原语为开发人员提供了一个由 32 个抽头组成的可编程延迟线,可提供可调节或固定的延迟。实际可用的原语取决于我们正在使用的 IO bank 的类型。High

2022-10-12 14:19:39

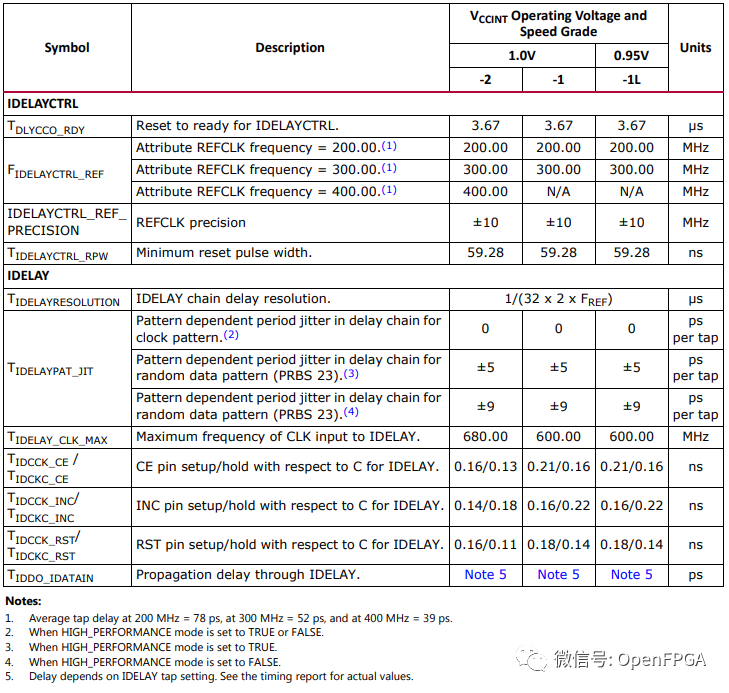

嗨,我使用的是Kintex 7(325,-2速度等级)。我想在VAR_LOAD模式下使用ODELAY并非常频繁地更改抽头值。我看到ODELAY上的最大时钟速度为800MHz的数据表,但我没有看到

2020-08-25 15:48:58

fpga应用篇(四):binary2bcd在实际中,我们常常需要将数据通过数码管或者LCD显示出来,例如,我们要将224显示到数码管上,我们要做的事就是分别提取出2,2,4这三个数字,然后分别送到

2017-04-10 18:04:37

嗨,大家好 *我在主串行模式下使用spartan-3e fpga和XCFxxS Prom。*对于fpga开始初始化,必须进行2次进行: 1)通电良好(正常工作), 2)引脚prog_B必须为高电平

2019-05-07 10:31:43

我的基本配置如下:1.SYNC信号连接至FPGA io口,并配置该IO口高电平输出2.ADC没有外接晶振,使用的内部晶振,并且内部晶振没有配置输出3.SCLK信号通过FPGA晶振分频得到,频率为

2019-01-30 11:24:43

MPS2和MPS2+FPGA原型板是ARM Cortex-M评估和开发的开发平台。

MPS2和MPS2+FPGA原型板提供以下功能:

Altera Cyclone FPGA和主板上电和配置MPS2

2023-08-18 07:25:28

`BPI-F2S 嵌入式和FPGA教育套件是一套基于凌阳7021 SOC的单片机高度集成的开发平台。具有高性能、低功耗的特点;嵌入式Linux嵌入式系统,适用于语音图像处理、通信、便携式工业控制设备

2020-04-26 14:51:09

_VALUE => 0, IDELAY2_VALUE => 0, IDELAY_MODE =>“正常”, ODELAY_VALUE => 0, IDELAY_TYPE =>

2018-10-11 14:52:33

我有兴趣在IDDR2和ODDR2前面使用一个IODELAY2作为Spartan 6上60MHz DDR接口的一部分。但我对一些属性和端口感到困惑。对于IDELAY_TYPE:不管您将其设置

2019-07-25 13:49:13

使用高云®半导体 GW2A/GW2AR 系列 FPGA 产品做电路板设计时需遵循一系列规则。本文档详细描述了 GW2A/GW2AR 系列 FPGA 产品相关的一些器件特性和特殊用法,并给出校对表用于

2022-09-29 06:32:25

GW2ANR 系列 FPGA 产品数据手册主要包括高云半导体 GW2ANR 系列 FPGA 产品特性概述、产品资源信息、内部结构介绍、电气特性、编程接口时序以及器件订货信息,帮助用户快速了解高云半导体 GW2ANR 系列FPGA 产品以及特性,有助于器件选型及使用。

2022-09-29 06:13:24

GW2AR 系列 FPGA 产品数据手册主要包括高云半导体 GW2AR 系列FPGA 产品特性概述、产品资源信息、内部结构介绍、电气特性、编程接口时序以及器件订货信息,帮助用户快速了解高云半导体 GW2AR 系列FPGA 产品以及特性,有助于器件选型及使用。

2022-09-29 06:59:13

GW2A 系列 FPGA 产品数据手册主要包括高云半导体 GW2A 系列FPGA 产品特性概述、产品资源信息、内部结构介绍、电气特性、编程接口时序以及器件订货信息,帮助用户快速了解高云半导体 GW2A 系列 FPGA产品特性,有助于器件选型及使用。

2022-09-29 06:37:08

使用我刚刚放入的ODELAY组件从DRC引擎获得以下错误:错误:[DRC 23-20]规则违规(PLOD-1)ODELAY检查3.3 V标准 - 端子p1750_hclk具有3.3 V标准,但连接到ODELAY。此组合无法清除。我在哪里可以找到有效的组合?TomT ...

2020-08-28 13:10:52

- >(到FPGA逻辑) | 时钟数据iddrdata - > ibufds - > idelay - > iddr - >(到FPGA逻辑)1 - 大多数情况下,我

2020-06-18 07:36:38

你好我最近购买了带有DDR SDRAM的FPGA Mimas V2 Spartan 6 FPGA开发板。我正在使用xilinx ise 14.7,verilog代码,当使用工

2019-08-08 09:44:18

喜我有一个设计,我连接了2个FPGA- 一个vlx75T(发送125MHz clk和txdata)到vlx760 FPGA。并且vlx760 FPGA在由vlx75生成的相同clk处将数据

2019-04-08 10:27:05

敬启者!在“Spartan-6 FPGA数据手册:DC amd开关特性”之后,IODELAY2元件Spartan6的最大延迟定义为:最大延迟=整数(抽头数/ 8)X Ttap8 + Ttapn。因此

2019-05-30 10:27:55

从光盘上拷下来的,Xilinx FPGA2 pro使用说明,想要的拿去吧

2013-10-24 10:14:16

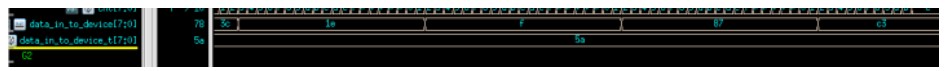

7A100,lvds经过idelay2,使用2个iserdes2级联后输出1:10。在idelay2扫描tap时,后面的iserdes输出的数据发生对齐错误,发现其中iserdes2(master

2023-05-09 11:23:05

ps2_keyboardfpga

2012-08-12 15:56:04

DDR2电路设计在高速大数据的应用中,高速大容量缓存是必不可少的硬件。当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR

2016-12-30 20:05:09

IODELAY2,以便可以将其校准为HALF_MAX。以下是主IODELAY2的配置: DATA_RATE =>“DDR”,IDELAY_MODE =>“正常”,SERDES_MODE

2019-06-26 07:14:40

大家好,我有一个使用Artix7 200部件的大型设计,该设计有超过100个输入,使用IDELAY2跨越8个库,根据这里的建议,我只需要为整个设计实例化1个IDELAYCTRL,我已经完成了它工作

2020-08-10 06:36:18

嗨!我正在试验用作解串器的Spartan-6。我无法100%无错误,所以不幸的是我需要更仔细地分析我的代码的行为(以及我在那里使用的原语:ISERDES,ODELAY2和校准机制 - 也许他们给了我

2019-07-24 06:17:58

`例说FPGA连载74:FX2与FPGA之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例有4个工程,一个8051 MCU

2017-02-17 10:24:06

`例说FPGA连载75:FX2与FPGA之SignalTap II与功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc FPGA

2017-02-19 20:28:01

`例说FPGA连载2:FPGA是什么特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc2015年伊始,Intel欲出资百亿美金收购

2016-06-23 16:04:27

FX2是不是类似于一个仿真器,内部的固件程序在下载FPGA程序时模拟JTAG协议将程序下进去吗,这时是不是工作在主模式下;还有上位机通过FX2与FPGA通信时是不是工作在被动模式下, 主动模式和被动模式的切换是通过什么来实现的?

2018-05-09 14:14:44

嗨,我在Kintex7上运行。我(我承认)我正在测试的ODELAY2原语的一个不寻常的应用程序。行为模拟表明设计应该有效,但实际上并非如此。我已经在硬件管理器中监视了尽可能多的信号,除了

2020-08-28 07:14:42

] .idelaye2_bus:mb_subsystem_pre_idelay_0_group''mb_subsystem_i / pre_idelay / inst / pins [0] .idelaye2

2018-11-08 11:29:47

_TYPE => "VAR_LOADABLE",IDELAY_VALUE => 0,ODELAY_TYPE => "VAR_LOADABLE"

2018-10-11 14:53:18

基于FPGA和AD1836的I2S接口该如何去设计?

2021-05-26 06:45:37

`积分商城兑换的礼品《基于FPGA的数字信号处理(第2版)》晒晒,:-)`

2016-03-28 23:53:15

Cyclone III系列型号为EP3C16F484C6N的FPGA作为控制器,以Micron公司生产的型号为MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM为存储器。用一个IP核完成

2011-05-03 11:31:09

我在sp601板上使用tri-ethernet-mac示例。gmii接收器接口使用IODELAY2原语来延迟接收器侧的输入信号。vhdl代码提到应该根据设计在ucf中更改IDELAY_VALUE。我

2019-05-28 06:40:20

海, 我的电路板由2个Kintex-7 fpga和两个独立的BPI闪光灯(微米级闪光灯)组成。如何使用单JTAG连接器(菊花链)progaram 2 fpga?theertha

2020-05-29 13:47:54

你好根据我的要求,我需要在一个IOB上使用2 odelay。我需要延迟这两个信号“ts_dqs”和“out_dqs”,如下所示。u_iobuf_dqs(.I(out_dqs),//来自FPGA .T

2020-07-14 10:59:46

”),. IDELAY_TYPE(“VAR_LOADABLE”),. IDELAY_VALUE(0),. REFCLK_FREQUENCY(200.0),. SIGIG_PATTERN(“DATA”))ODELAY

2020-06-13 06:54:13

是 IDELAY2 和 ODELAY2 原语。这些原语为开发人员提供了一个由 32 个抽头组成的可编程延迟线,可提供可调节或固定的延迟。实际可用的原语取决于我们正在使用的 IO bank 的类型。High

2022-10-09 16:00:19

大家好,我正在使用IDELAY原语来实现DDR的DQ和DQS延迟。这是我的代码:IOBUF pad_xb_dq7(.O(bus_data_in_flh [7]),. IO(xb_dq [7

2020-06-01 16:57:41

我有一些源同步系统,它可以在8条线路上为FPGA提供DDR数据。时钟频率在> 500 MHz范围内。我知道我需要使用ISERDES和IDELAY来正确捕获这些数据。 8 ISERDES提供64

2019-04-15 14:18:39

我阅读了UG381第71页,DS162第47页以及该主板上的各种主题,以帮助我了解如何正确配置抽头延迟。我使用Spartan 6 IODELAY2块来恒定数据总线的ODELAY,以满足下游CPU

2019-07-17 08:47:54

您好!我有FPGA Cyvon和FX2LPB开发板。在我的项目中,我需要将流数据从FPGA发送到FX2LP,我使用流IVHDL代码FROMAN61345项目和非周期化PLL,DDR和引脚分配为

2019-10-22 10:37:10

你好,我正在使用MCB连接fpga到DDR2内存。我可以从fpga端写入内存,但是当我尝试阅读它时。数据没有出现。有没有办法查看加载到内存中的数据。我正在使用模拟模型,但似乎没有任何帮助。如果有

2019-05-27 13:52:30

怎么实现基于FPGA视频采集中的I2C总线设计?

2021-06-03 06:51:15

Input3Input4Input8Input16Input32output信号Output1Output2Output3Output4Output8Output16Output32要使用上面快捷命令,需要明德扬的配置文件,欢迎关注明德扬公众号“fpga520”,或群544453837索取。口号:多用模板,减少记忆,专注设计!

2017-11-29 15:19:11

DDR2控制和FPGA实现

2015-07-21 19:28:14

我的开发板是XEVMK2LX,板上使用的XC3S400 FPGA来控制编程CDCM6208,我需要FPGA的源程序,请问从哪里可以下载到?

2018-06-21 05:37:37

各位大哥大姐求一个 基于FPGA的PS/2鼠标接口的设计与实现的程序设计可有偿~~~~联系qq392404578

2016-05-11 14:17:48

` 本帖最后由 rousong1989 于 2015-6-11 13:17 编辑

特权同学FPGA抢楼赠书第2波活动规则:获得赠书必须符合以下所有的条件:1.回复本帖报名。2.回复《特权

2015-05-31 20:41:07

嗨,各位,我正在与FX3S进行图像流传输。是为FLIGIN模式的16位GPIF2设计器工作的FPGASTER Verilog代码,请提供给我感谢和最好的关心 以上来自于百度翻译 以下为原文Hi

2018-11-26 15:49:06

你好,世界,在我的设计中,我将有2个FPGA:Virtex 5和Virtex 6。FPGA将使用ACE文件从COMPACT FLASH配置。我是否必须在1中混合2个ACE文件,或者每个FPGA都有一

2019-01-18 08:50:08

”= PERIOD“Sysclk”16 ns HIGH 50%;OFFSET = IN 5 ns有效16 ns在“Sysclk”之前;我的问题是:Virtex5 FPGA如何通过路由资源,IDELAY或其他方式实现5 ns延迟?谢谢。克里斯

2020-06-13 19:23:05

下方法约束IDELAYE2实例时:set_property LOC IDELAY_X0Y48 [get_cells system_i / adc_8lvds_0 / inst / lvds0

2020-08-18 08:28:10

IDELAYE2提供数据,IDELAY2为GBUF提供数据。时钟频率为335 MHz。 IDELAY参考时钟频率为300 MHz。任何可能出错的想法都可以解决这个问题吗?PN是XC7VX485T-2FFG1157C。 - 保罗塔多尼奥

2020-07-15 06:06:24

亲爱的先生/女士,请建议我使用Xilinx FPGA完全替代smartfusion2 FPGA。我们希望在我们的新设计中用Xilinx等效FPGA取代smartfusion(M2

2019-04-29 10:13:39

mode是指由Column和Row I/O混合。从表1中可以看出,Cyclone III只有6系列的FPGA在Top和Bottom BANK才支持200MHz频率的DDR2。为了满足设计要求,我们将4片

2019-05-31 05:00:05

NVIDIA DGX-2

2021-11-22 09:26:58

微信公众号《FPGA2嵌入式》原创文章

2021-11-22 09:26:58

斑梨电子FPGA CycloneII EP2C5T144 学习板 开发板产品参数1. 采用ALTERA公司的CyclonellEP2C5T144芯片作为核心最小系统,将FPGA

2023-02-03 15:14:29

上千M。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23:00 21423

21423

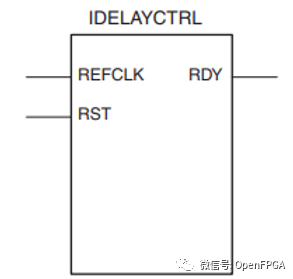

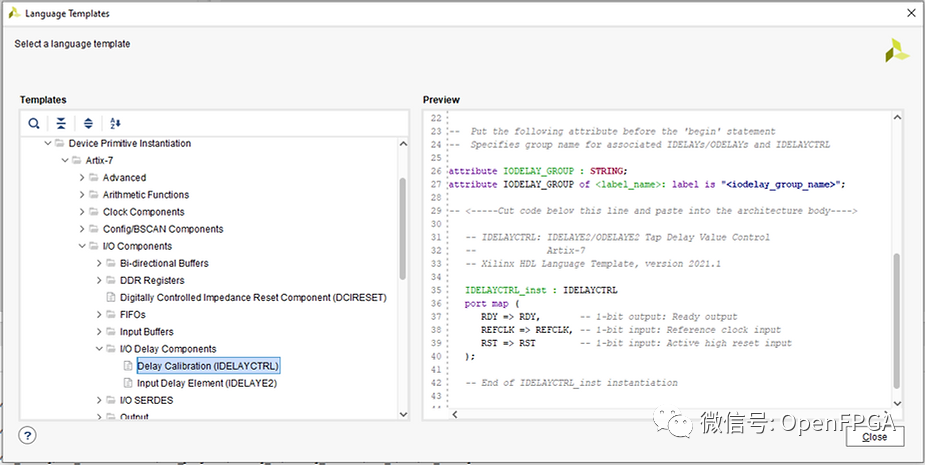

同样,为了减小相同参考时钟下Idelay2与IDELAYCTRL 的FPGA内部走线延时,必须使用IODELAY_GROUP将它们绑定在一起,使用方法参考上面的做法。

2022-08-20 10:50:23 3575

3575

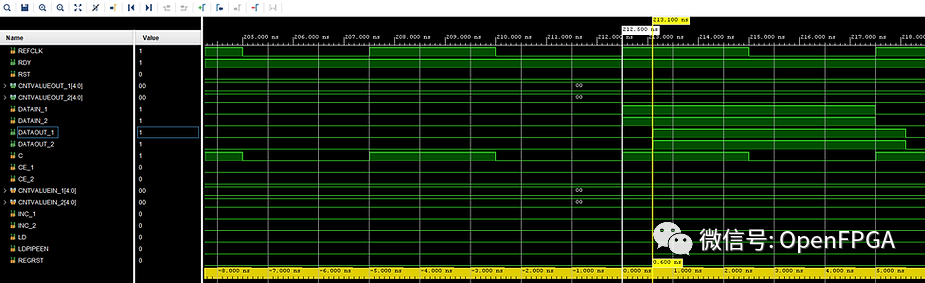

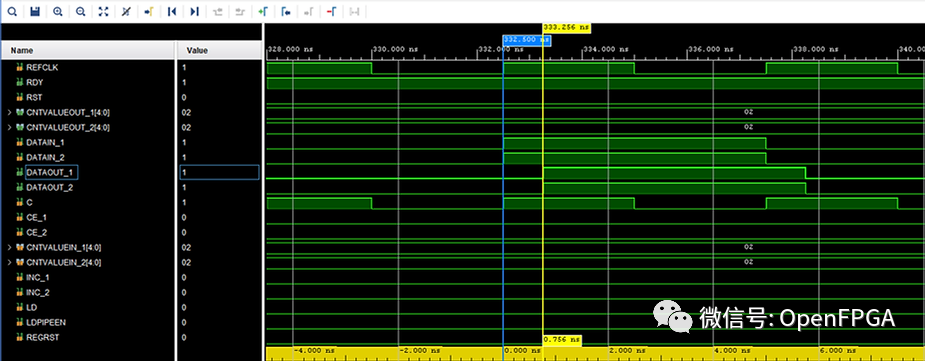

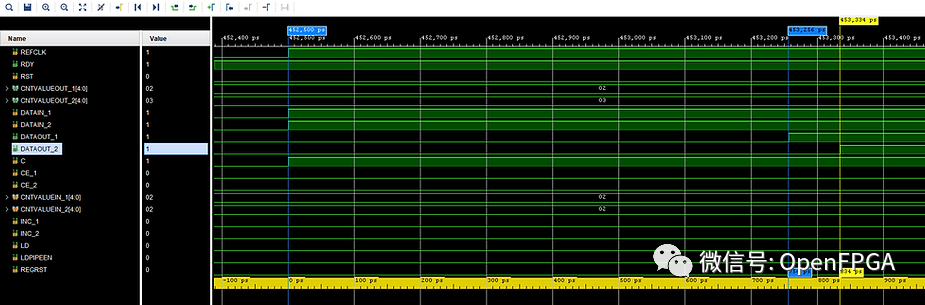

最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

2023-06-06 11:09:56 1597

1597

电子发烧友App

电子发烧友App

评论