本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 15422

15422

以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

9177 数据。 对于第一种方法,FPGA 包括LUT/FF/RAM 等资源,分析各种资源等效门数时,总原则是等效原则,就是实现相同的功能,在标准门阵列中需要的门数就是FPGA 该资源等效门数,例如实现一个带

2012-08-11 10:29:07

FPGA 如何进行浮点运算

2015-09-26 09:31:37

时,总原则是等效原则,就是实现相同的功能,在标准门阵列中需要的门数就是FPGA 该资源等效门数,例如实现一个带寄存器输出的4 输入XOR,在FPGA 中需要用一个LUT 和1 个FF 实现,在标准门阵列

2012-03-01 10:08:53

在Quartus中怎样在工具在设置使得代码可以被映射到FPGA上的指定区域?在书上看到要进行位置约束,不知怎么弄!本人刚接触这个,求大神解答

2017-06-10 22:25:21

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

)是两种不同的硬件实现方式。

FPGA是一种可编程逻辑器件,其内部资源可以根据需要进行配置和重新配置。这些资源包括但不限于:

逻辑单元(Logic Cells):这些是FPGA的核心计算资源,可以实现各种

2024-02-22 09:52:22

也无法对原始的网表进行解密操作。在阿里云FaaS IP 市场的帮助下,即便是从来没有任何FPGA开发经验的用户,也可以一键从IP市场中获取相应的加速逻辑,并部署到对应的FPGA器件上面去。相信通过即开

2018-05-22 11:58:12

图像采集系统的结构及工作原理是什么FPGA逻辑设计中的常见问题有哪些

2021-04-29 06:18:07

FPGA中等效逻辑门概念数的计算方法有两种,一是把FPGA基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA基本单元的等效门数,然后乘以

2012-08-10 14:05:35

FPGA小白一枚,个人理解的FPGA本质上或者核心就是查找表(LUT),即将所有的函数/方法 转换为固定的查找表(使用DSP除外)。但是为什么所有的文章提到FPGA全部都注重逻辑门呢?其实FPGA本身内部也没有多少物理的逻辑门吧?

2019-05-30 10:53:46

转化成较低层次的描述。综合优化根据目标与要求优化生成的逻辑连接,使层次设计平面化,以便用FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等

2023-12-31 21:15:31

●低成本开发套件●专用参考设计将设计从构思变为产品,更迅速推向市场。采用Cyclone III FPGA,一切皆有可能。(特权同学,版权所有)在过去,衡量一个逻辑器件的资源情况,仅仅看他的逻辑资源便可

2015-04-17 12:05:21

逻辑复制与资源共享本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 逻辑复制是一种通过增加面积来改善时序条件

2015-07-05 19:54:33

测试脚本编写本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt Testbench的编写其实也没有想象中那么

2015-08-25 21:30:23

在线调试方式大都是通过FPGA器件引出的JTAG接口,同时使用了一些FPGA片内固有的逻辑、存储器或布线资源就能够实现的。这些调试功能通常也只需要随着用户设计所生产的配置文件一同下载到目标FPGA器件中

2015-09-02 18:39:49

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-10-08 14:43:50

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2021-09-03 07:00:00

生成的逻辑连接,使层次设计平面化,以便用FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级

2020-11-30 16:22:59

和坏,或者电路的通和断、电灯的亮和暗、门的开和关等等。这种只有两种对立逻辑状态的逻辑关系成为二值逻辑。当使用两个数码表示逻辑状态时,它们之间可以按照指定的某种因果关系进行推理计算,将这种运算称为逻辑

2023-02-20 17:24:56

时序电路)。 在组合逻辑电路中,任何时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。在上一节中,设计的三人表决器就是组合逻辑电路,输出与输入一一对应,和其他

2023-02-21 15:35:38

`FPGA面积优化1.对于速度要求不是很高的情况下,我们可以把流水线设计成迭代的形式,从而重复利用FPGA功能相同的资源。2.对于控制逻辑小于共享逻辑时,控制逻辑资源可以用来复用,例如FIR滤波器

2014-12-04 13:52:40

;"小于"这样的判断语句, 这样会明显增加使用的逻辑单元数量 .看一下报告,资源使用差别很大.例程:always@(posedge clk)begincount1=count1+1

2018-03-24 11:04:41

组合逻辑:基本逻辑门Wirewire线型的基本描述已在笔记整理(1)中给出了。题目:实现输入与输出的连接。答案:module top_module ( input in, output out

2021-09-08 07:32:26

逻辑门及组合逻辑电路实验实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法。4.

2008-09-25 17:28:34

我们还看到,每个门分别具有与非门,或非门和缓冲器形式的相反或互补形式,并且这些门中的任何一个都可以连接在一起以形成更复杂的组合逻辑电路。我们还看到,在数字电子产品中,“与非”门和“或非”门都可以被

2021-01-27 08:00:00

及方案改进 在FPGA设计中,必须首先明确HDL源代码编写非常重要;不同综合工具包含的综合子集不同致使有些HDL语句在某些综合工具中不能综合;同一逻辑功能可用不同HDL语句进行描述,但占用资源却可

2008-06-26 16:16:11

对于单元测试是程序员基本修养,下面介绍对于harmonyos开发的过程中如何进行单元测试。假如我要对以下方法进行测试,按住Alt+enter > Create Ohos Test创建测试类。选择测试要测试的方法。便会生成测试方法。接着编写测试逻辑内容。运行。附件:

2022-01-25 09:44:49

USB OTG的工作原理是什么?IP设计原理是什么?如何进行IP模块设计?USB OTG IP核有什么特性?如何对USB OTG IP核进行FPGA验证?

2021-04-27 06:44:33

TTL逻辑门与普通逻辑门的区别在哪里为什么引入OC门?

2021-03-29 07:23:21

,电路图是用来指定配置的,就像对asic的配置一样,但这种情况越来越少)FPGA包含一个可编程逻辑块的数组,以及一个可重构互连的层次结构,允许块被“连接在一起”,就像许多逻辑门一样,可以在不同的配置中

2018-12-13 14:39:07

labview中 如何进行图像的梯度化请大神指点迷津{:4_107:}

2013-12-17 18:51:34

请问大家,pspice的逻辑门模型,比如说与门7408,该怎样修改其参数?我想修改7408的延迟时间,输出电平等等,怎么弄?关于右键点击然后edit pspice model的方法,我试过,只是出来

2014-06-24 10:09:17

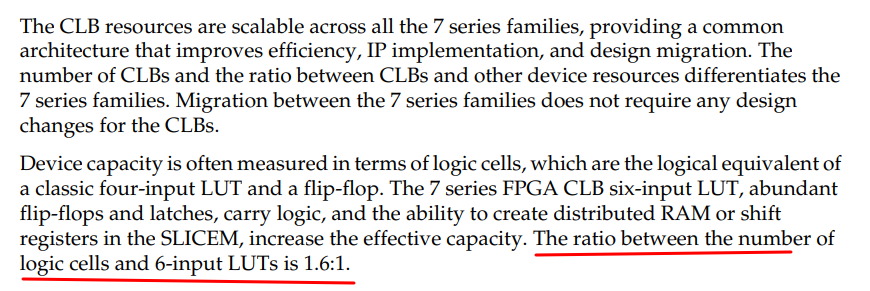

或6 个输入、一些选型电路(多路复用器等)和触发器组成。开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。在Xilinx 公司的FPGA 器件中,CLB 由多个(一般为4 个

2012-03-08 11:03:49

四路2输入CMOS逻辑或门CD4071四路2输入CD4075三路3输入CD4072双4输入7432四路2输入逻辑或门在下一本关于数字逻辑门的教程中,我们将介绍TTL和CMOS逻辑电路中使用的数字逻辑NOT门功能,以及其布尔代数定义和真值表。

2021-01-20 09:00:00

四路2输入CMOS逻辑或门CD4071四路2输入CD4075三路3输入CD4072双4输入7432四路2输入逻辑或门在下一本关于数字逻辑门的教程中,我们将介绍TTL和CMOS逻辑电路中使用的数字逻辑NOT门功能,以及其布尔代数定义和真值表。

2021-01-21 08:00:00

够大;从确保足够的驱动电流考虑应当足够小.2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能.在总线传输等实际应用中需要多个门 的输出端并联连接使用,而一般TTL门输出端

2016-08-23 21:39:46

FPGA的逻辑电路基础知识四、逻辑值 逻辑0:表示低电平,对应GND。 逻辑1:表示高电平,对应VCC。 逻辑X:表示未知,可能高电平,可能低电平。 逻辑Z:表示高阻态,外部没有激励信号,悬空状态

2019-12-10 20:32:03

我用fpga生成的两路分辨率很高的脉冲,想在fpga外进行逻辑与。对与门参数有什么要求吗。比如上升沿下降沿的识别能力或者带宽等等

2019-05-13 10:57:47

器件中的重要创新之一,2D NoC 为 FPGA 设计提供了几项重要优势,包括:· 提高设计的性能,让 FPGA 内部的数据传输不再成为瓶颈。· 节省 FPGA 可编程逻辑资源,简化逻辑设计,由

2020-09-07 15:25:33

逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能,看!

2019-07-23 07:03:30

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

1、集成逻辑门及其基本应用介绍本实验涉及到的基本逻辑门有“与门”、“与非门”、“或门”、“或非门”、“异或门”和“同或门”,功能简单,实验时使用2个拨动开关模拟逻辑门的输入信号,通过LED灯的点亮或

2022-07-01 15:18:51

一个地址进行查表,找出地址对应的内容,然后输出即可。从表中可以看到,LUT 具有和逻辑电路相同的功能。实际上,LUT 具有更快的执行速度和更大的规模。由于基于LUT 的FPGA 具有很高的集成度,其

2018-08-23 09:14:59

在labview中如何进行数据存储?

2013-07-26 09:19:08

、RAM、DSP和处理器核心。带有关键块、逻辑块、IO块和可编程互连的FPGA如图9.3所示。互连现场可编程设备中的布线资源称为互连。可编程开关用于将一条互连线连接到另一条互连线或将逻辑块连接到互连线的开关

2022-10-27 16:43:59

文件为txt文件中共有10000个数据点,每个数据点由6个元素组成,分别对应6路信号即6条曲线,每个波形由200个数据点组成,每个文件中共有50个波形如图后面那个 读后标记 如何进行下次数据的读取求解

2017-05-24 22:07:49

本文使用符合PCI电气特性的FPGA芯片进行简化的PCI接口逻辑设计,实现了33MHz、32位数据宽度的PCI从设备模块的接口功能,节约了系统的逻辑资源,且可以将其它用户逻辑集成在同一块芯片,降低了成本,增加了设计的灵活性。

2021-05-08 08:11:59

逻辑结构之上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了大约高达27Tbps的超高带宽。作为Speedster7t FPGA器件中的重要创新之一,2D NoC为FPGA

2020-10-20 09:54:00

的发生,不是通过调用芯片内不同区域不同逻辑资源的组合来实现,而是通过对具有专门缓存逻辑资源的FPGA,进行局部和全局芯片逻辑的动态重构而快速实现。

2019-09-20 07:15:52

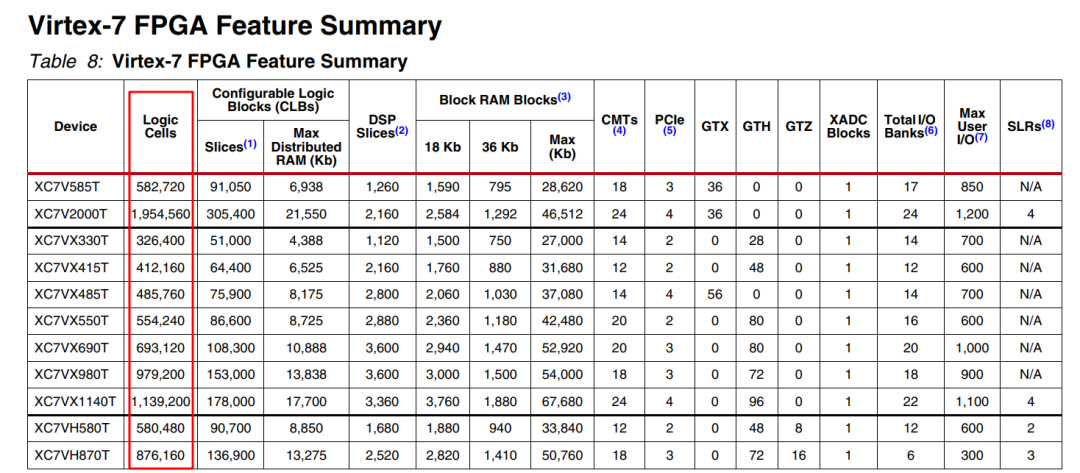

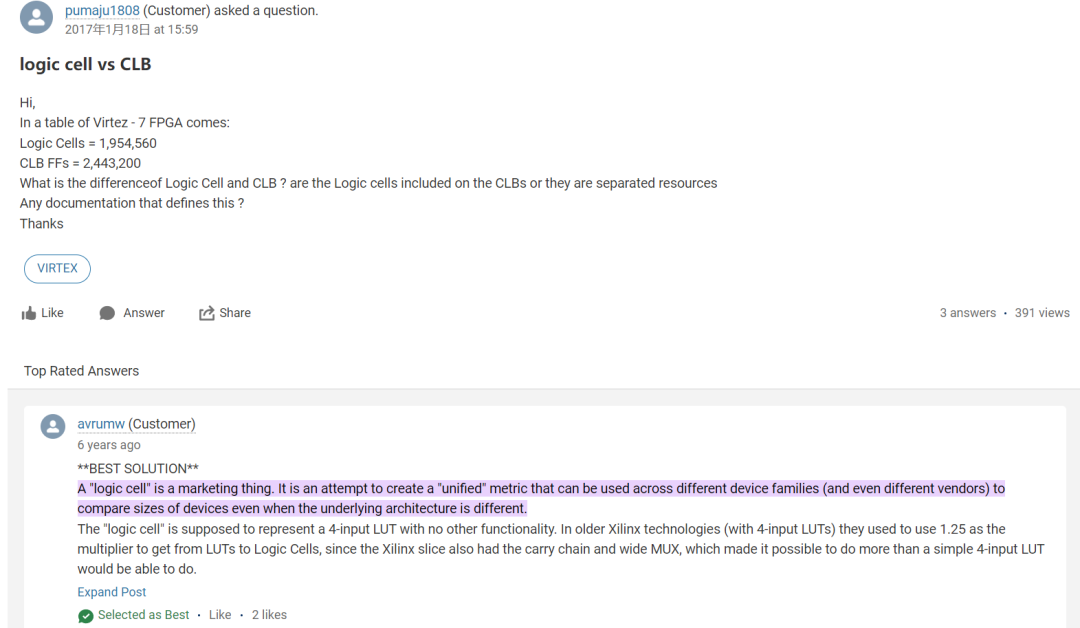

嗨,我目前正在对设计进行初步分析。我正在研究关于实现不同功能所需资源的不同FPGA。我找不到一种方法来将设计使用的LUT数量相关联,并将其转换为virtex和spartan范围的逻辑单元格。如果可能

2019-01-08 10:18:36

你好。我是在FPGA上设计系统的初学者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想计算基本15位2输入加法器的逻辑延迟。如果我能检查AND门或OR门的延迟等

2020-05-25 07:28:24

(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析

2019-06-17 09:03:28

请问怎么将无源器件连接到逻辑门?

2021-04-13 06:48:09

我们在实现FPGA逻辑电路时,时常会在Verilog代码里添加一些约束原语。前言我们在描述FPGA电路时,我们经常会在电路里添加一些像这样的约束原语:通过这种方式,我们可以指导FPGA在综合及布局

2022-07-22 14:28:10

2GHz)的传输速率运行。NoC为FPGA设计提供了几项重要优势,包括:提高设计的性能。减少逻辑资源闲置,在高资源占用设计中降低布局布线拥塞的风险。减小功耗。简化逻辑设计,由NoC去替代传统的逻辑去做高速

2020-05-12 08:00:00

灌电流是什么?灌电流越大与逻辑门输出端的低电平有何关系?拉电流是什么?拉电流越大与逻辑门输出端的高电平有何关系?

2021-10-11 08:53:52

与否。 4.问题与思考实验中以与门作为例子进行设计,你如何经过简单改动,按照同样的方式来设计或门,非门和以或门并进行仿真验证?逻辑门运算符Verilog算法代码与门&assign y

2015-04-03 11:18:25

现在我需要一个逻辑门器件,与门和或门。要求是在输入时间为100ns的脉冲信号(可调),两个输入,一个输出。然后通过这个逻辑门器件之后可以用示波器检测到。。。新人也不懂 啊,需要什么型号的器件呢?

2018-09-17 16:01:36

套件这个学习工具包将允许用户了解逻辑门是如何工作的,这对初学者来说非常有用。该套件已打开所有逻辑门,并允许用户使用不同的逻辑门进行实验。图 1 是该套件的示意图。(对不起,原理图做得不好)图 1 - 示意图 图 2 是可以制造的 PCB 的图片。图 2 - PCBPCB

2022-09-08 07:42:05

在使用FPGA进行生成位文件时候,提示"请求的DMA通道过多或存在冲突。当前终端的DMA通道数量为3。查看请求通道列表,删除一个或多个请求方以释放资源"。请问论坛大神,可否多个

2016-09-01 19:14:47

今天和大侠简单聊一聊FPGA设计中不同设计方法硬件资源消耗对比,话不多说,上货。

在这里,我们使用Verilog HDL 设计计数器,通过两种不同的写法,对比资源消耗。计数器实现的功能是计数记到24

2023-05-31 17:25:21

列出4中能做非门的逻辑门(非门除外)

2010-04-29 18:54:58

我理解的比较简单。将代码烧写进FPGA,芯片内部的各个逻辑门通过逻辑连线实现逻辑功能,这些逻辑门的输入是通过查找表获得的。比如我用到两个与门和一个或门,对于4输入的LUT来讲,则至少需要两个LUT。

不知道这样理解对不对。

还有具体LUT内部是如何实现查找的,请知明人能够提点提点。

谢谢

2023-04-23 14:12:58

异成门逻辑符号图/同或门逻辑符号图

2019-10-23 03:49:43

嗨朋友们, 我想知道在Virtex 5 LX110中有多少门数等于1个逻辑单元?此外,从逻辑单元计算栅极数量的公式也是必须的。请尽快发给我。还要把附件文件和我的问题的答案一起发给我。再见,MUTHU

2020-05-28 17:18:52

和灵活性,可实时完成运动控制过程中复杂的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。本文选用DSP与FPGA作为运动控制器的核心部件,设计了通用型运动控制器。其中DSP用于运动轨迹规划、速度控制

2019-07-31 08:15:26

钟控传输门绝热逻辑电路和SRAM 的设计本文利用NMOS管的自举效应设计了一种新的采用二相无交叠功率时钟的绝热逻辑电路---钟控传输门绝热逻辑电路,实现对输出负载全绝热方式充放电.依此进一步设计了

2009-08-08 09:48:05

集成在一块板子上的fpga和arm如何进行通信呢?

2022-11-07 15:31:04

由于同步动态随机存储器SDRAM内部结构原因导致其控制逻辑比较复杂。现场可编程逻辑门阵列FPGA作为一种半定制电路具有速度快、内部资源丰富、可重构等优点。本文设计了一种基于FPGA的SDRAM

2017-11-18 12:42:03 2054

2054

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 本文档的主要内容详细介绍的是数据库概念结构和逻辑结构与物理结构如何进行设计的详细资料免费下载

2018-10-23 16:42:37 17

17 本文档的主要内容详细介绍的是单片机教程之如何进行单片机内部资源的C51编程详细资料免费下载

2018-11-30 18:02:52 21

21 在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 3580

3580 FPGA由逻辑单元、RAM、乘法器等硬件资源组成,通过将这些硬件资源合理组织,可实现乘法器、寄存器、地址发生器等硬件电路。

2019-12-27 07:05:00 1613

1613

线的 的RAM。 当用户通过原理图或HDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

2020-12-29 16:59:44 4

4 本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

2020-12-29 17:27:00 3

3 介绍IO口与FPGA管脚对应关系表。

2021-03-18 10:02:26 12

12 如何进行OPCDCOM配置(四会理士电源技术有限公司招聘)-如何进行OPCDCOM配置

2021-09-18 14:23:09 11

11 (06)FPGA资源评估1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA资源评估5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 如何进行电源设计 - 第1部分

2022-11-02 08:16:07 1

1 而且现在的LUT都是4输入或者6输入,可以做成逻辑门的组合,跟普通的逻辑门个数肯定不会是一对一关系。今天我们来看下这个关系如果对应。

2022-11-11 09:06:23 1035

1035 关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 1099

1099 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密。

2023-02-16 09:26:57 11450

11450

电子发烧友App

电子发烧友App

评论