本小节通过使用XPS中的定制IP向导(ipwiz),为已经存在的ARM PS 系统添加用户自定IP(Custom IP ),了解AXI Lite IP基本结构,并掌握AXI Lite IP的定制方法,为后续编写复杂AXI IP打下基础。同时本小

2012-12-23 15:39:12 11129

11129 FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门

2020-12-25 14:07:02 2957

2957

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。

2022-07-08 09:24:17 1281

1281 在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)。

2022-07-08 09:31:38 1945

1945 在某些情况下,通过嗅探 AXI 接口来分析其中正在发生的传输事务是很有用的。在本文中,我将为大家演示如何创建基本 AXI4-Lite Sniffer IP 以对特定地址上正在发生的读写传输事务进行计数。

2022-07-08 09:35:34 775

775 首先对本次工程进行简要说明:本次工程使用AXI-Full接口的IP进行DDR的读写测试。在我们的DDR读写IP中,我们把读写完成和读写错误信号关联到PL端的LED上,用于指示DDR读写IP的读写运行

2022-07-18 09:53:49 3902

3902

主设备接口表示为S_AXI_HPn_FPD,两个高性能一致性(HPC)AXI主设备接口表示为S_AXI_HPCn_FPD。

2022-07-22 09:25:24 2501

2501 AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下

2023-07-27 09:19:33 633

633

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。它根据IP的编程和选择的操作模式生成各种类型的AXI事务。是一个比较好用的AXI4协议测试源或者AXI外设的初始化配置接口。

2023-11-23 16:03:45 580

580

首先我们看一下针对AXI接口的IP设计,在介绍之前我们先回顾一下AXI所具有的一些feature。

2024-02-20 17:12:56 518

518

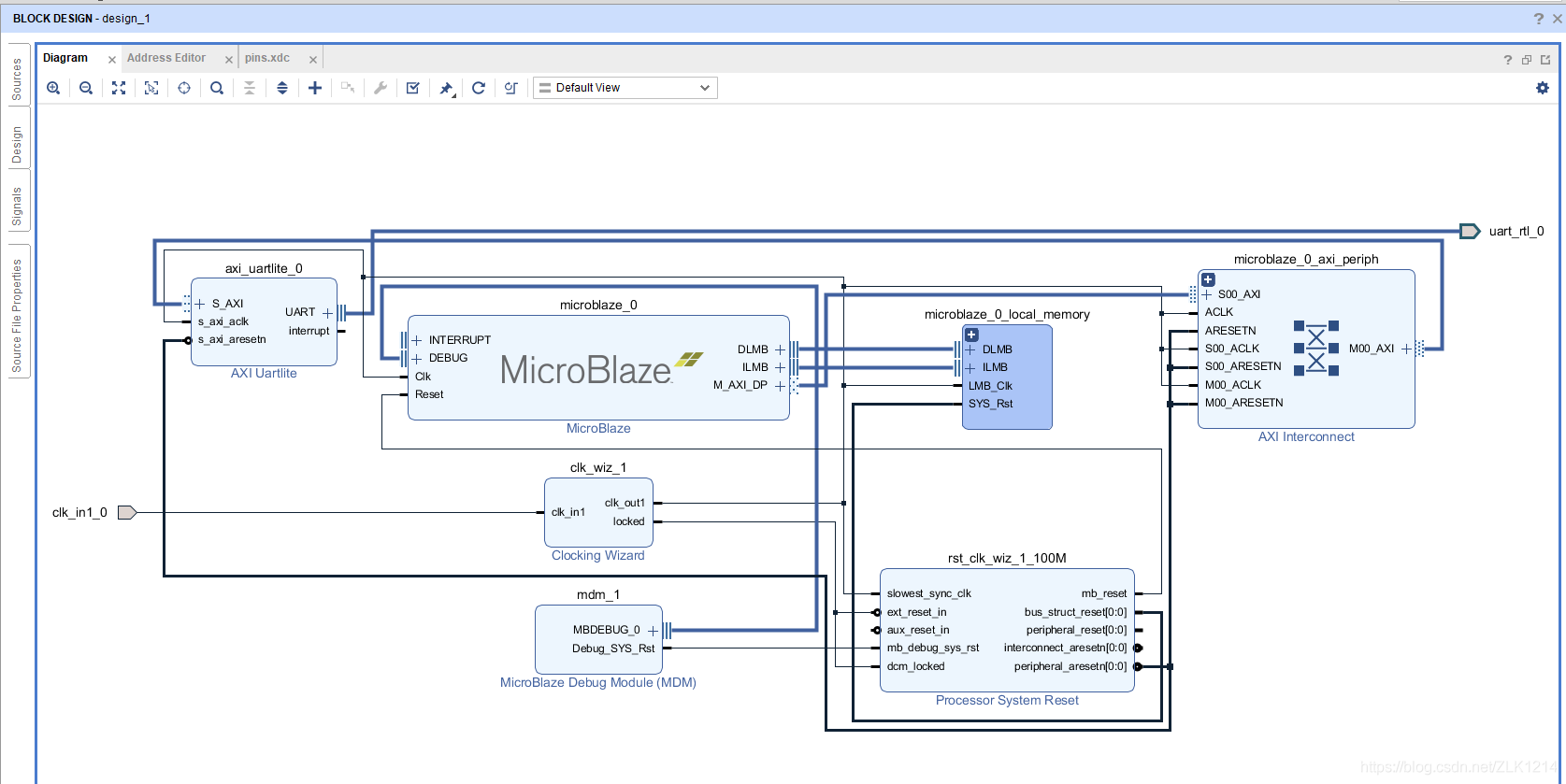

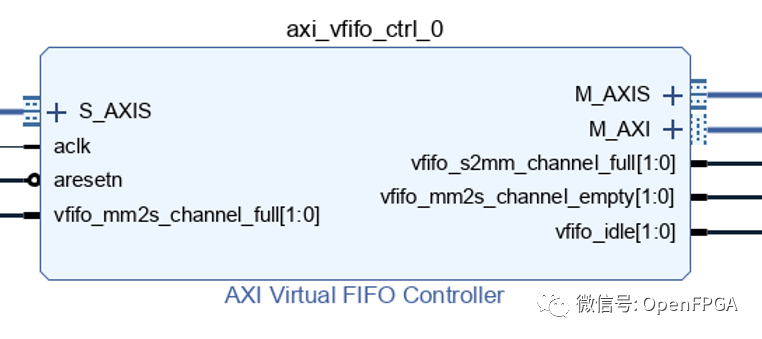

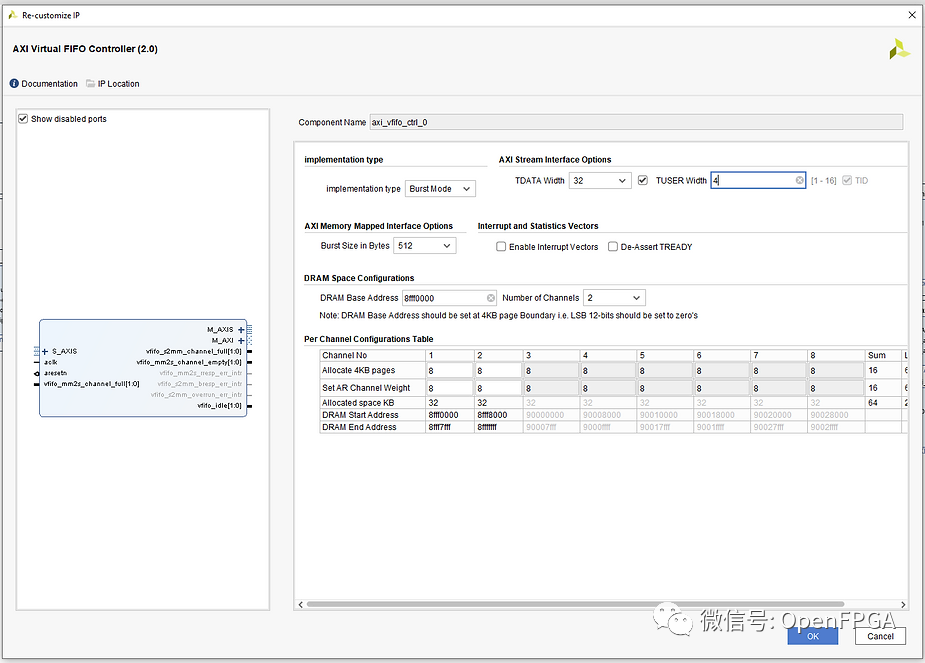

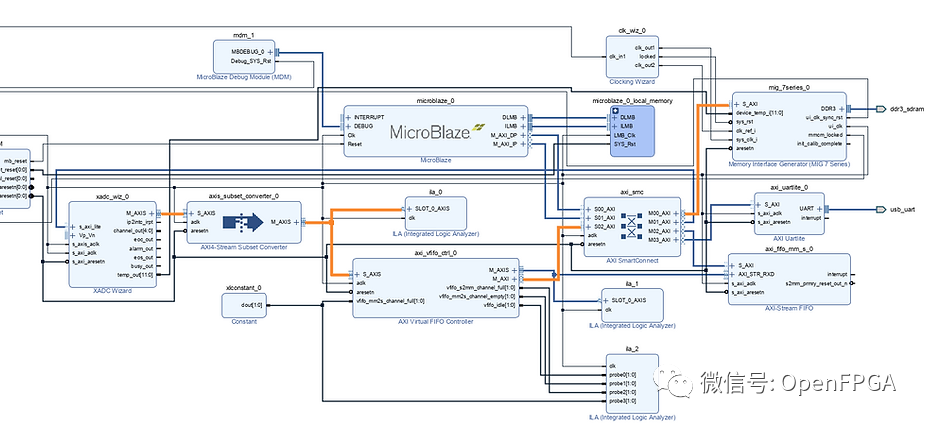

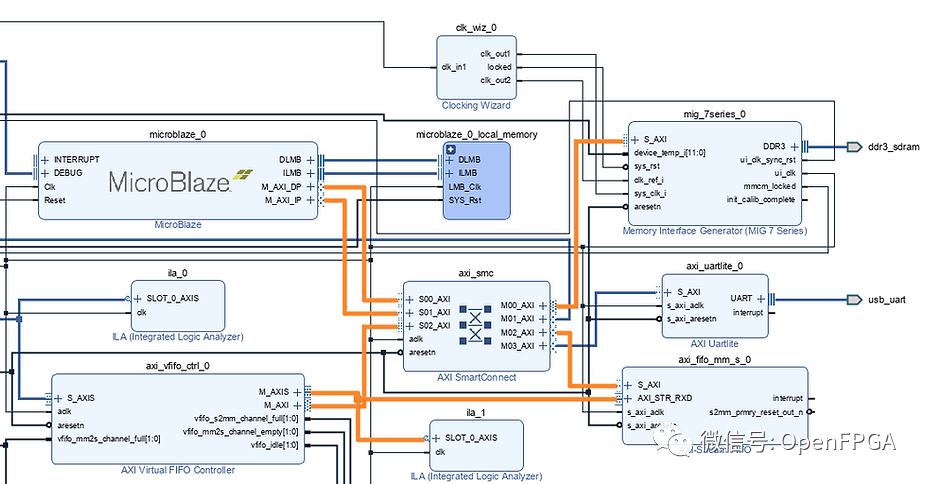

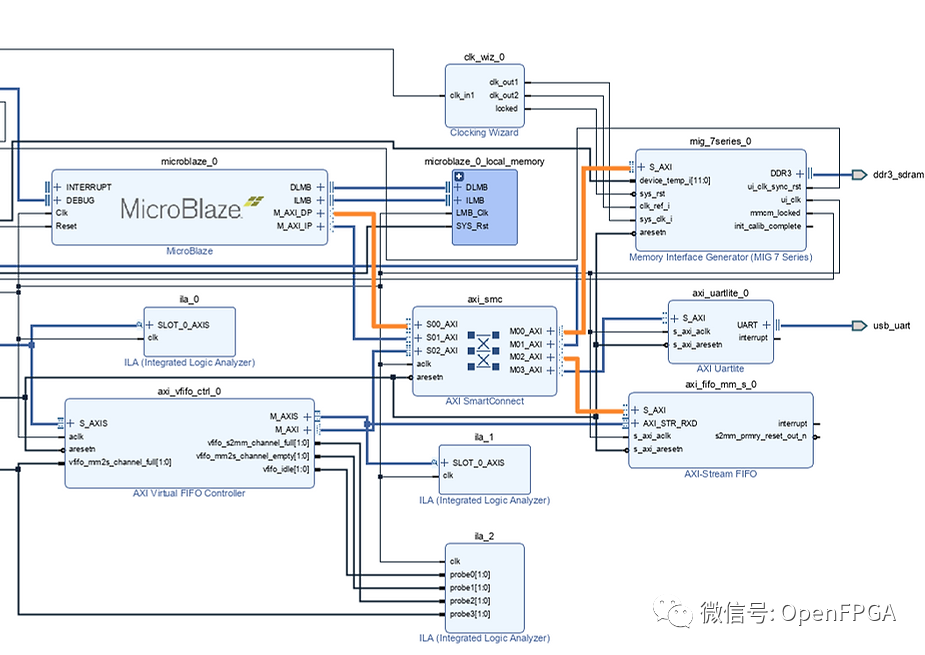

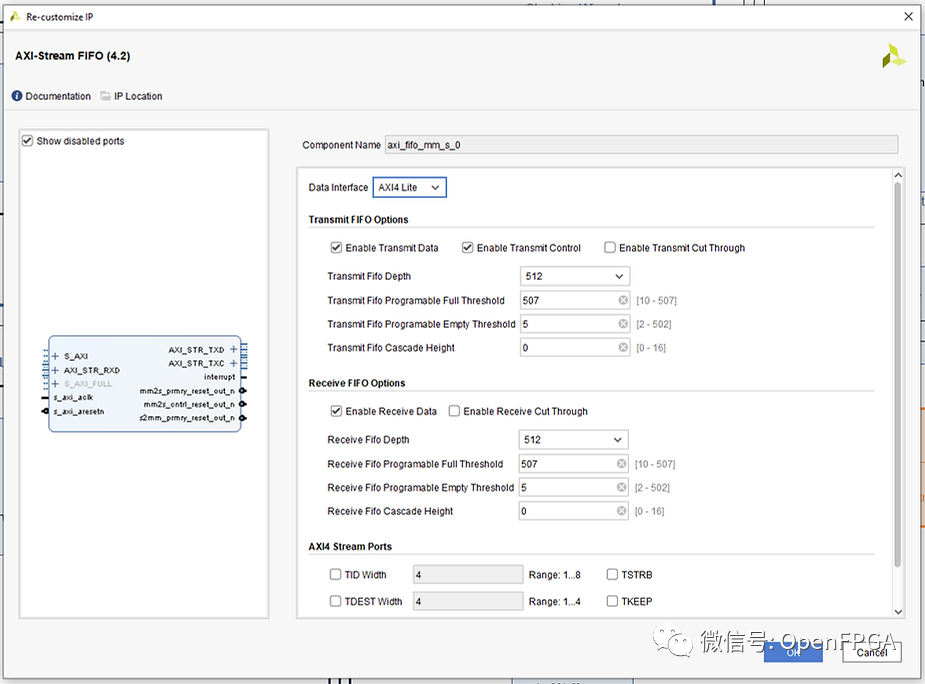

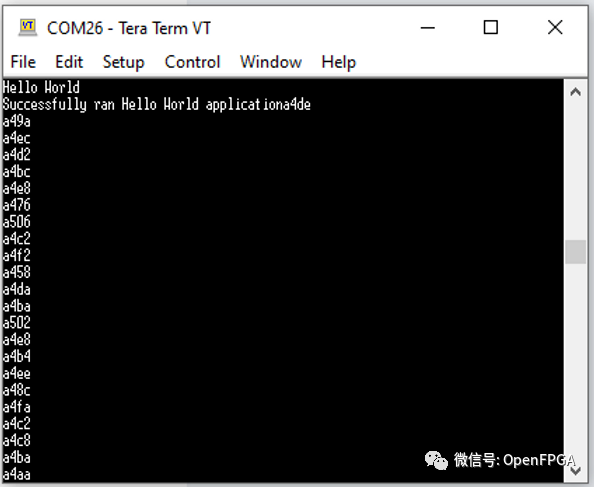

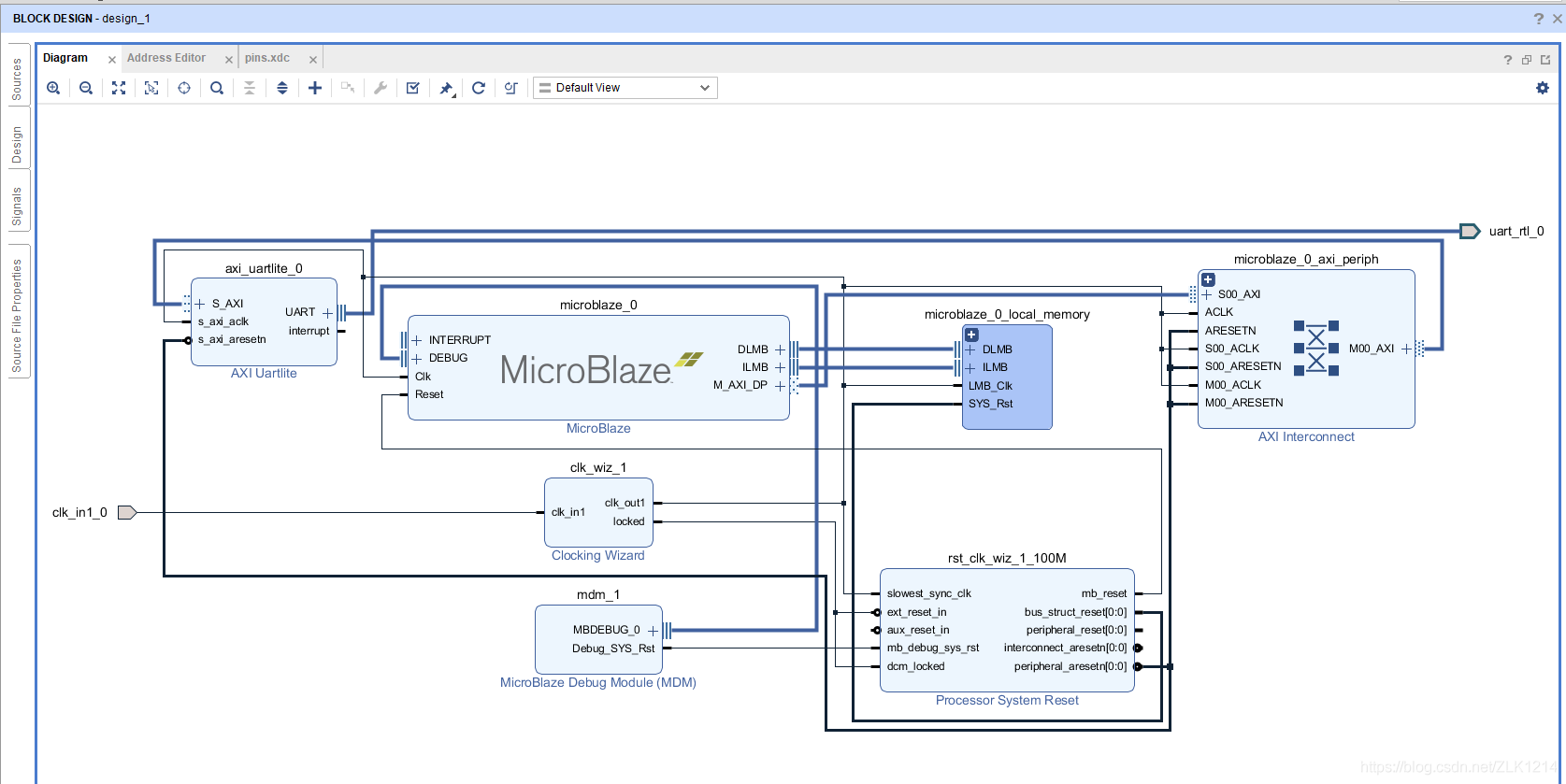

,MicroBlaze 应用程序)可能会发生冲突。在 IP 定制时,我们能够分配的空间需要注意。接下来创建一个以 Xilinx FPGA(S7-50 )为目标的小项目,项目主要演示AXI Virtual FIFO

2022-11-04 11:03:18

Checker IP 的检测呢 ? https://www.xilinx.com/support/documentation/ip_documentation/axi_protocol_checker/v2_0

2020-02-28 13:44:01

:尽管本规范支持动态更改每个数据拍的像素/样本数,但不建议这样做,因为并非所有IP都支持此功能。Figure 1‐8: 每个数据拍两个像素,每个分量八位(RGB888,VF码2),每个数据拍两个像素

2022-11-14 15:15:13

PL端的编写和使用,接下来是PS端的介绍AXI_Lite总线使用方法(上)pl端读写BRAM一、总览如图,main函数实现的功能主要是初始化中断,中断来自WRRD模块发送数据完毕,中断触发为上升沿。具体功能往下看。我们首先来看#define。不知道还有没有记得..

2022-01-10 08:00:55

表4‑11 各种 AXI 的应用的例子AXI 接口三种AXI接口分别是:AXI-GP接口(4个) :是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过改接口可以访问PS中的片内外

2022-04-08 10:45:31

我正在使用AXI流FIFO将数据流式传输到Rx端,最终也将通过AXI总线从处理器读回。当我尝试读取“base_address + 0x1C”时,系统挂起......以前有人遇到过这种情况吗?在阅读

2019-04-24 12:54:04

- master_clk_o slave_spisel - master_ss_o 两个ip核心都以标准spi模式配置,频率比为4。 从中断线连接到zynq ps IRQ_F2P [0:0]端口并使能从

2020-04-17 10:13:04

今天有空来学习一下xilinx的axi_iic ip。下面的链接是xilinx官网关于axi_iic的数据手册,大家点一下就可以看了pg090-axi-iic pdf数据手册先给我们这个ip的顶层

2022-01-18 07:00:13

。ncvlog:* F,MAXERR:达到最大错误计数(5)。source_verilog.f是这样的文件列表:../axi_bridge/14.4/axi_pcie3_0/ip_2/source

2020-07-25 11:26:47

层次结构仍然类似于vivado 14.3生成的核心,但源代码文件在核心文件夹ip0和ip1源文件夹中减少了很多。 ip1 / fifo_generator_v12_0 / hdl中不存在

2020-07-25 08:31:47

IP核均采用AXI总线接口,已经不再支持native接口。故做除法运算的重点从设计算法电路转变成了调用AXI总线IP核以及HDL中有符号数的表示问题,极大降低了开发难度。以下就上述两个方面进行探讨

2018-08-13 09:27:32

本手册主要描述 FIFO 的功能特性、端口、时序、相关配置及参考设计,旨在帮助用户快速了解 Gowin FIFO IP 的产品特点及使用方法。

2022-10-09 06:31:58

本手册主要描述 FIFO HS 的功能特性、端口、时序、相关配置及参考设计,旨在帮助用户快速了解 Gowin FIFO HS IP 的产品特点及使用方法。

2022-10-09 06:09:15

查看2015年11月发布的JTAG-to_AXI IP产品指南(PG174)(据我所知,最新版本)第19页,它显示了创建“具有8个32位数据”的写AXI突发事务的示例。这不可能是正确的。这看起来只

2020-05-20 09:11:18

的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。今天,首先说一下自定义AXI4的IP核,至于AXI

2019-12-13 17:10:42

嗨,我已经创建了一个带有IP-Core的硬件设计。但它不能正常工作。对于我提到的调试问题,我创建了一个IP-Core,然后通过AXI Stream。所以我可以检查我的IP-Core是否不起作用

2020-04-14 09:25:10

有效;(8)TUSER信号 :用户定义信号,宽度为128bit。三种AXI接口分别是:AXI-GP接口(4个):是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过改接口可以访问PS

2018-01-08 15:44:39

您好,我正在使用Zynq 7设备在Vivado上运行AXI UART 16550示例项目。从AXI UART 16550 v2.0的文档中,Tx和Rx的FIFO深度为16个字节。我修改了测试台,看看

2020-05-25 07:42:05

中有两个是“hw_axi_1和hw_ila_1”。 ..但是当我编程时,我的设计只有“hw_ila_1”ip;怎么了?以及如何消除“hw_axi_1”ip谢谢..

2020-08-12 09:16:08

大家好我对7系列家族的XADC向导提出了一个小问题。我设计了我的XADC并且它运行成功,但是因为我想在其后放置一个FIFO内存,我想在XADC中启用AXI4Stream以实现更好的同步。所以我现在

2020-05-20 14:53:11

result [64])核心有两个端口,一个64个整数/元素的输入数组(合成为ap_memory),输出端口合成为ap_fifo。我使用Axi4Lite / Slave向顶级模块发出指令,以便将生成

2019-02-28 13:47:30

/cpu_uart/ip/cpu_uart_axi_quad_spi_0_0/cpu_uart_axi_quad_spi_0_0_clocks.xdc":52] set_max_delay -from

2018-10-18 14:37:32

了)。IP添加完成就可以在tb中实例化。1.2、在sv格式的tb中加入下面两条import语句 ,第一个import是固定不变的,axi_vip对应axi_vip_pkg,axi-stream vip

2022-10-09 16:08:45

嗨,我开始使用Vivado了。我正在尝试配置从Dram读取数据的自定义IP,处理它们然后将结果发送到Bram控制器。我想过使用AXI主接口制作自定义IP。但是,我不知道将AXI主信号连接到我的自定义逻辑,以便我可以从Dram读取数据并将结果发送到Bram。谢谢。

2020-05-14 06:41:47

你好我想实现一个同步FIFO 2点有两个输出eindpoints和两个端点,我创造的这些enpoints描述符中并创建为每个端点的DMA通道,但我仍然找不到工作。我怎么能用2在端点的端点,实现Slave FIFO亲切问候Ragy;

2019-09-20 14:06:58

有人知道为什么MIG IP核中的AXI协议。为什么没有AXI_WID这个信号呢。

2018-04-13 09:22:30

),要用verilog实现AXI Stream的异步FIFO1、读写不同的时钟,设一个100M,另一个333M2、读写不同的位宽,设写为8bit,读为32bit3、fifo深度为324、控制信号没有

2014-02-21 16:24:45

的网络最终会出现在两个不同的ILA内核(每个16位)中。任何指针?或者任何人都可以指出我在UISng PA其他UG677上的chipcope pro调试中的任何其他材料。问候钱德拉以上来自于谷歌翻译以下

2019-03-08 13:57:18

不做过多的讲解(小伙伴可以自行下载AMBA总线协议规范或者翻看网络上AXI4总线协议相关文章)。在SpinalHDL中,关于Axi4总线,包含了配置和实现两块内容,其内容均在

2022-08-02 14:28:46

于FIFO,搞逻辑的人都不陌生,对于FIFO的使用场景,哪怕是十年的老司机碰到两个信号也是十分惊惧的:Overflow、Underflow。在整个的工程设计里,不管你对自己的设计多么有信心也要老老实实

2022-06-30 15:28:00

。当我移除ASVO核心时,我还尝试使用Video-In到Axi4-Stream核心(VIAS)测试Video Scaler核心。视频流也可以通过这两个核心。正如我上面所说,我使用了两个VTC核心。一个

2019-11-08 09:53:46

嗨,我在Vivado 2016.3模块设计中集成了PCIe DMA BAR0 AXI Lite接口和AXI IIC IP。在DMA IP端,它显示S_AXI_Lite端口,但在AXI_IIC IP端

2020-05-14 09:09:35

嗨,我正在研究Spartan 6的设计。数据来自PCIe IP核,频率为62.5MHz,通过AXI4-Stream FIFO同步到100 MHz系统时钟。这是一个示例波形;m_axis_tvalid

2019-08-12 07:29:20

我没有Fifo的设计运行速度为227 Mhz。实施AXI Fifo the Max后。频率降至179 Mhz。这是XC6SLX150-2CSG484I设备中此Fifo的最大频率

2019-06-20 15:35:42

突发。AXI信号就像以前的AMBA版本中的AHB,ASB和APB信号一样,每个AXI通道都有许多与之相关的信号。有两个全局信号称为ACLK和ARESETn。它们分别是系统的全局时钟和复位信号

2020-09-28 10:14:14

1.什么是FIFO?FIFO是英文First In First Out 的缩写,是一种先进先出的数

2009-07-22 16:00:48 0

0 摘要:使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FUFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路

2006-03-24 12:58:33 680

680

什么是fifo (First Input First Output,先入先出队列)这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。1.什么是FIFO

2007-12-20 13:51:59 11835

11835 AXI Reference Guide (AXI).pdf

2012-12-23 16:41:36 55

55 Xilinx的视频的IP CORE 一般都是 以 AXI4-Stream 接口。 先介绍一下, 这个IP的作用。 下面看一下这个IP 的接口: 所以要把标准的VESA信号 转为

2017-02-08 08:36:19 531

531

本小节通过使用XPS中的定制IP向导(ipwiz),为已经存在的ARM PS 系统添加用户自定IP(Custom IP ),了解AXI Lite IP基本结构,并掌握AXI Lite IP的定制方法,为后续编写复杂AXI IP打下基础。

2017-02-10 20:37:12 5407

5407 本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面。使用的硬件平台是Zedboard。 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块,先简要描述各个版本的主要内容。

2018-06-29 14:34:00 7834

7834

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 7873

7873

本文包含两部分内容:1)AXI接口简介;2)AXI IP核的创建流程及读写逻辑分析。 1AXI简介(本部分内容参考官网资料翻译) 自定义IP核是Zynq学习与开发中的难点,AXI IP核又是十分常用

2018-06-29 09:33:00 14958

14958

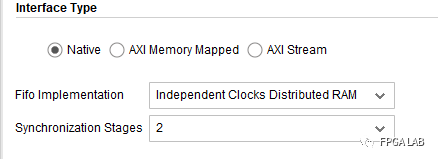

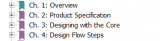

IP核的全称是: AXI4-STREAM FIFO 设置注意事项:一定要选择异步时钟,也就是双时钟,如下: 关于其他配置: TLAST 一般要选择的,作为边界界定。其他可以不选。深度不必太深,因为只起到穿越时钟区域的作用。

2018-03-26 14:40:00 4916

4916

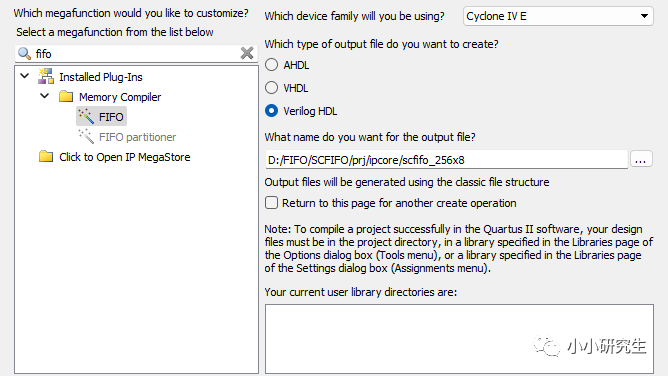

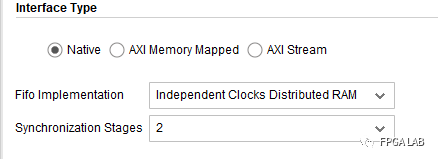

配置FIFO的方法有两种:

一种是通过QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中选择FIFO参数编辑器来搭建自己需要的FIFO,这是自动生成FIFO的方法

2018-07-20 08:00:00 17

17 了解如何使用Xilinx AXI验证IP有效验证和调试AXI接口。

该视频回顾了使用的好处,以及如何使用示例设计进行模拟。

2018-11-20 06:38:00 3561

3561 AXI USB 2.0设备IP概述

2018-11-30 06:29:00 3378

3378 由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2019-05-12 09:10:33 10860

10860

。

AXI-HP由我提供的AXI-HP转FIFO模块实现。需要给这个模块提供控制信号:

即从哪读,读多少个到FIFO中;

从FIFO中读多少个数,并写往哪里。

2019-08-06 06:15:00 2101

2101 这将创建一个附带 BD 的 Vivado 工程,此 BD 包含 AXI VIP (设置为 AXI4-Lite 主接口) 和 AXI GPIO IP。这与我们在 AXI 基础第 3 讲一文 中完成的最终设计十分相似。

2020-04-30 16:24:50 2068

2068

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过

2020-10-30 12:32:37 3953

3953

引言 近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq、Zynq MP、MicroBlaze 和全新的 Versal 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有

2020-09-27 11:06:45 5857

5857

XDMA是Xilinx封装好的PCIE DMA传输IP,可以很方便的把PCIE总线上的数据传输事务映射到AXI总线上面,实现上位机直接对AXI总线进行读写而对PCIE本身TLP的组包和解包无感。

2020-12-28 10:17:23 2692

2692 DMA的总结 ZYNQ中不同应用的DMA 几个常用的 AXI 接口 IP 的功能(上面已经提到): AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP----AXI

2020-10-09 18:05:57 6391

6391

AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口。 Xilinx提供的从AXI到AXI-Stream转换的IP核有:AXI-DMA,AXI-Datam

2020-11-02 11:27:51 3880

3880

[导读] 前面写过篇介绍ZYNQ基本情况的文章,今天来肝一篇实战文章介绍AXI quad SPI 使用方法,如果你正使用ZYNQ的这个IP,希望对你有所帮助。 初识AXI quad SPI

2021-04-09 17:45:59 6679

6679

设计。最后介绍了基于AXI协议的设计实例,探讨了利用IP复用技术和DesginWare IP搭建基于AXI协议的SOC系统。

2021-04-12 15:47:39 28

28 在一个项目中,当你使用microblaze作为控制器来进行系统调度的时候,一般是建议将所有模块封装成AXI形式的IP核,这样好管理,也容易调试。

2021-04-27 11:17:36 5652

5652

学习内容 近期设计需要用到AXI总线的IP,所以就对应常用的IP进行简要的说明,本文主要对AXI互联IP进行介绍。 基础架构IP 基础的IP是用于帮助组装系统的构建块。基础架构IP往往是一个通用IP

2021-05-11 14:52:55 5612

5612

本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 7547

7547

本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2022-07-03 16:11:05 6846

6846 由于平时我们工作中,FIFO都是直接调用IP核,对于FIFO深度选择并没有很在意,而在笔试面试过程中,经常被问及的问题之一就是如何计算FIFO深度。

2022-07-03 17:25:28 2222

2222 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818 前面简单学习了关于GPIO的操作,本次将使用PL 端调用 AXI GPIO IP 核, 并通过 AXI4-Lite 接口实现 PS 与 PL 中 AXI GPIO 模块的通信。

2022-07-19 17:36:52 3230

3230 在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP

2022-08-02 09:43:05 579

579

逻辑核™ IP FIFO生成器用户指南描述了FIFO生成器,以及有关设计、定制和实现的信息核心。

2022-08-28 11:09:00 2

2 如果 STRIDE 等于 HSIZE,那么 AXI VDMA IP 会在没有任何跳转的情况下读取帧缓存。但是,由于输入大小大于输出大小,我们需要在地址之间跳转以便能够正确地对齐下一行的开头。

2023-02-15 11:25:24 712

712 上面两图的区别是相比AXI3,AXI4协议需要确认AWVALID、AWREADY握手完成才能回复BVALID。为什么呢?

2023-03-30 09:59:49 668

668 AXI 是一种接口规范,它定义了 IP 块的接口,而不是互连本身。

2023-05-04 09:27:39 703

703

大家好!今日分享一些关于Video In to AXI4-Stream IP 核的知识。在具体学习IP核的过程中,我也将分享一些关于如何看xilinx英文文档的技巧。

2023-05-18 14:55:16 966

966

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 911

911

最近需要用到AXI接口的模块,xilinx的IP核很多都用到了AXI总线进行数据和指令传输。如果有多个设备需要使用AXI协议对AXI接口的BRAM进行读写,总线之间该如何进行仲裁,通信?

2023-06-19 15:45:14 4243

4243

FIFO?还是FIFO IP核?这也需要写总结吗?太容易了吧。如果我是一个正在处于面试找工作中的年轻人,肯定关注的是如何手撕FIFO,这也是当时校招时候干过的事情。

2023-06-21 14:22:09 817

817

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

2023-06-25 16:31:25 1914

1914

可以看到,在AXI到UART中,是通过寄存器和FIFO进行中介的。因为从AXI总线往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下AXI VIP当作master时如何使用。

2023-07-27 09:16:13 792

792

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FIFO(First In First Out, 先入先出 ),是一种数据缓冲器,用来实现数据先入先出的读写方式。数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线,有一个写端口和一个读端口。

2023-09-07 18:30:11 821

821

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE IP AXI以太网内核,而无需使用完整的DMA解决方案。

2023-09-25 10:55:33 497

497

Xilinx 从 Spartan-6 和 Virtex-6 器件开始采用高级可扩展接口 (AXI) 协议作为知识产权 (IP) 内核。Xilinx 继续将 AXI 协议用于针对 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado

2023-10-16 10:12:42 410

410

LogiCORE IP AXI 通用异步接收发送器 (UART) 16550 连接到高级微控制器总线架构 (AMBA) AXI,为异步串行数据传输提供控制器接口。该软 IP 核旨在通过 AXI4-Lite 接口进行连接。

2023-10-16 11:02:01 1762

1762

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用? 1. 同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO在处理时序有明显的区别。同步FIFO相对来说是较为

2023-10-18 15:23:58 790

790 以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

电子发烧友App

电子发烧友App

评论