FPGA设计:为什么要做同步设计?

- FPGA(591969)

- 同步设计(6550)

相关推荐

基于FPGA的通信系统同步提取的仿真与实现

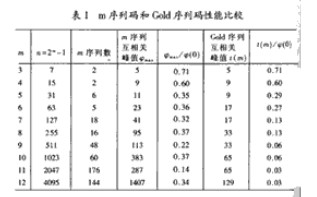

本文介绍一种基于现场可编程门阵列(FPGA)的通信系统同步提取方案的实现。本文只介绍了M序列码作为同步头的实现方案,对于m序列码作为同步头的实现,只要稍微做一下修改,即加一些相应的延时单元就可以实现。

2013-04-11 10:53:23 3829

3829

3829

3829

基于FPGA的通用位同步器设计方案

摘要本文提出了一种基于FPGA的通用位同步器设计方案。方案中的同步器是采用改进后的Gardner算法结构,其中,内插滤波器采用系数实时计算的Farrow结构,定时误差检测采用独立于载波相位偏差的GA-TED算法,内部控制器和环路滤波器的参数可由外部控制器设置,因而可以适应较宽速率范围内的基带码元。

2013-10-14 13:58:10 5135

5135

5135

5135

基于FPGA的帧同步系统设计方案

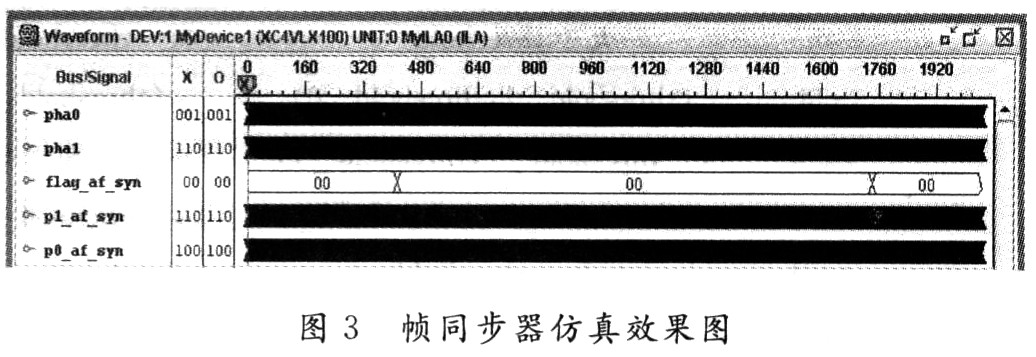

本文介绍了集中式插入法帧同步系统的原理,分析了帧同步系统的工作流程。采用模块化的设计思想,利用VHDL设计了同步参数可灵活配置的帧同步系统,阐述了关键部件的设计方法,提出了一种基于FPGA的帧同步系统设计方案。

2013-11-11 13:36:01 4359

4359

4359

4359

FPGA案例解析:针对源同步的时序约束

约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步

2020-11-20 14:44:52 6859

6859

6859

6859

FPGA/CPLD同步设计若干问题浅析

FPGA CPLD同步设计若干问题浅析摘要:针对FPGA/CPLD同步设计过程中一些容易被忽视的问题进行了研究,分析了问题产生的原因、对可靠性的影响,并给出了解决方案。关键词:FPGA/CPLD

2009-04-21 16:42:01

FPGA中的同步与异步复位

和removal时序检查;异步复位同步撤离(推荐使用) 优点:能避免纯异步或纯同步复位的潜在问题。它是FPGA设计中最受欢迎的复位,Altera建议使用这种复位方法。这种复位在使用前需要同步到各个使用时

2014-03-20 21:57:25

FPGA异步时钟设计中的同步策略

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

FPGA板卡如何与非FPGA板卡同步

我有一块IN的FPGA板卡PXI-7854R和非FPGA板卡PXI-6733,请教各位大神,数据输出和采集时如何将这两块板卡同步

2014-12-06 20:47:27

FPGA设计中帧同步系统的实现

FPGA设计中帧同步系统的实现数字通信时,一般以一定数目的码元组成一个个“字”或“句”,即组成一个个“帧”进行传输,因此帧同步信号的频率很容易由位同步信号经分频得出,但每个帧的开头和末尾时刻却无法由

2012-08-11 16:22:49

FPGA设计中帧同步系统的实现

FPGA设计中帧同步系统的实现数字通信时,一般以一定数目的码元组成一个个“字”或“句”,即组成一个个“帧”进行传输,因此帧同步信号的频率很容易由位同步信号经分频得出,但每个帧的开头和末尾时刻却无法由

2012-08-11 17:44:43

fpga和ad9789是如何同步的?

我们的设计用到了FPGA和AD9789进行CMOS电平的数字通信。fpga的时钟跟AD9789的时钟是异步的,不知道这样的设计会不会导致fpga和ad9789的通信不稳定,如何避免。fpga和ad9789是如何同步的?通信速率fs=18.284MHz,fdac=2.395204GHz。谢谢!

2023-12-21 08:29:25

fpga和外围芯片的接口同步问题

fpga和外围芯片进行通讯是不是需要把所有外围芯片传进来的信号进行同步,就是用寄存器打一拍(就是把所有wire类型的输入变量变为reg),输出也应该用寄存器打一拍(就是说不能以wire类型的数据输出)。这样做是不是能一定程度保存信号同步?

2012-10-28 22:31:25

OFDM系统中频域同步技术及FPGA实现方法是什么

本文主要介绍各部分的算法方案及电路实现时所用的FPGA元件的基本结构、设计思路。最后通过对电路的仿真波形可以看出,这些频域同步算法和FPGA电路能够满足多载波传输系统的同步要求。

2021-05-07 06:52:34

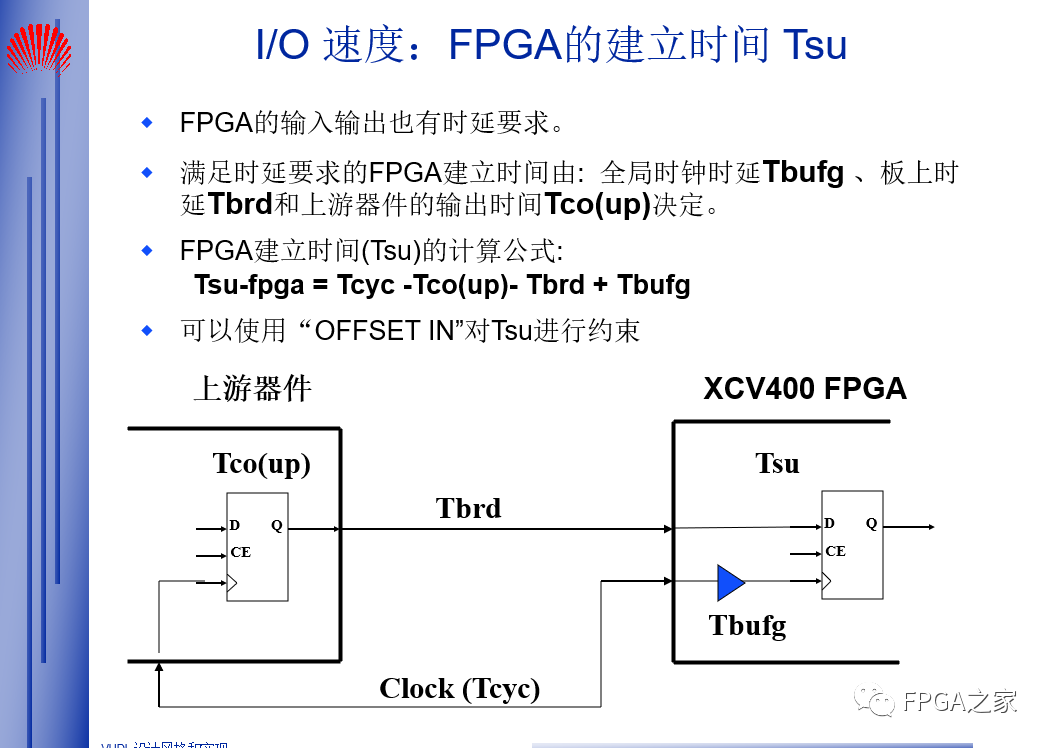

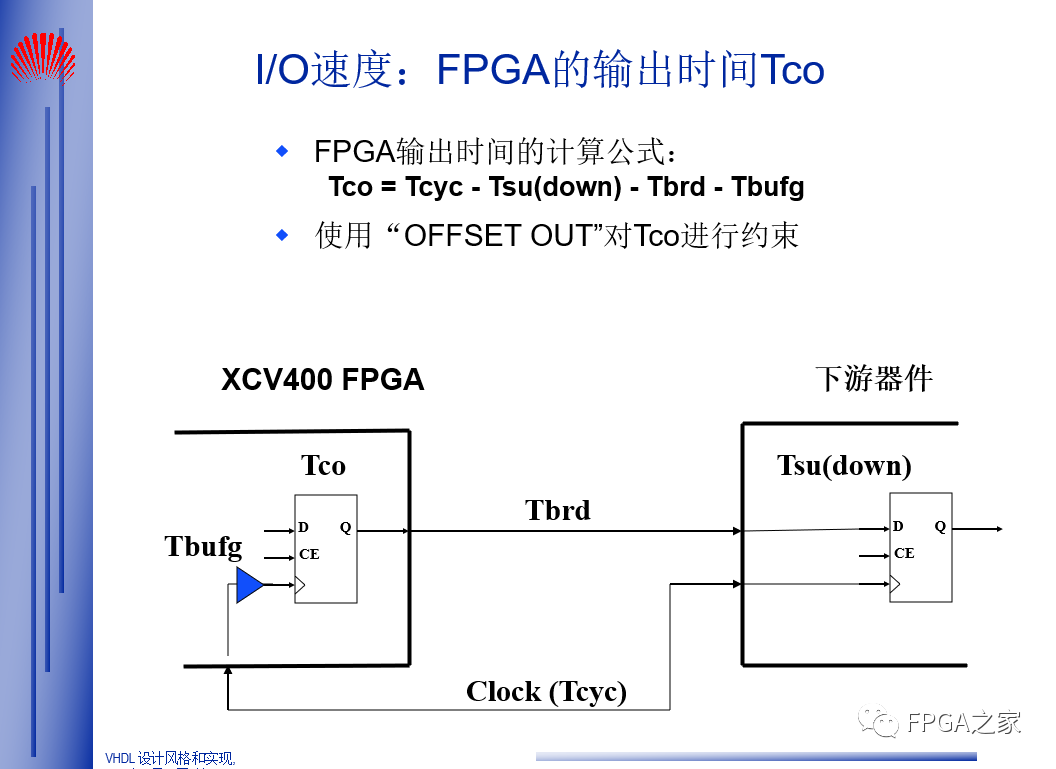

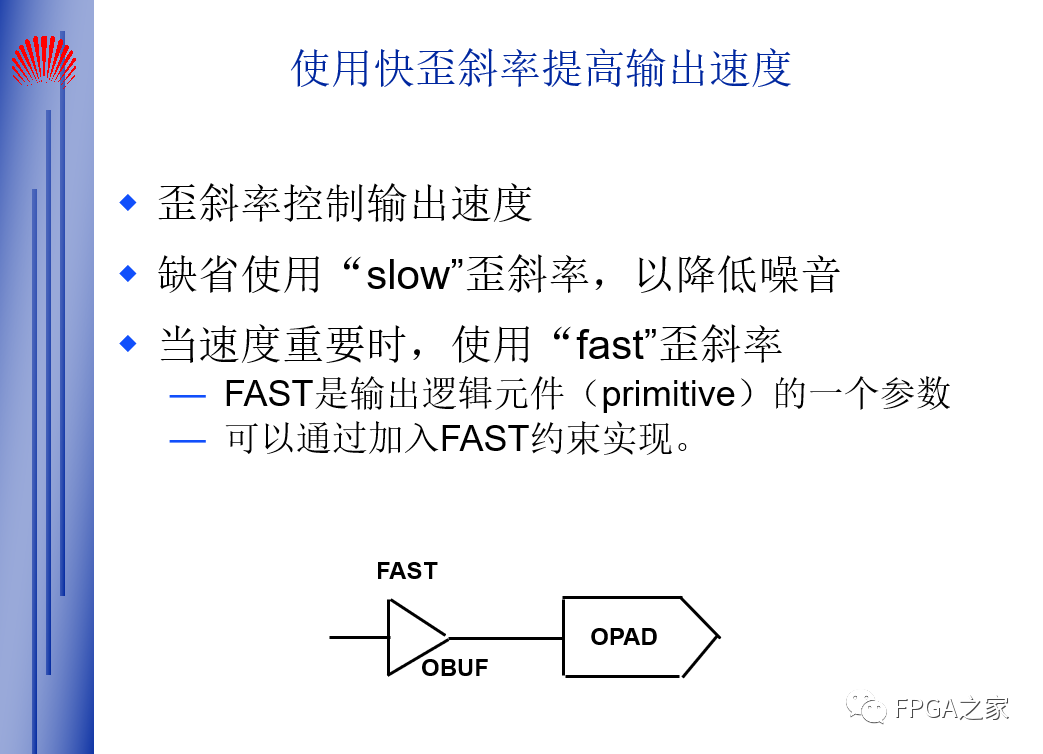

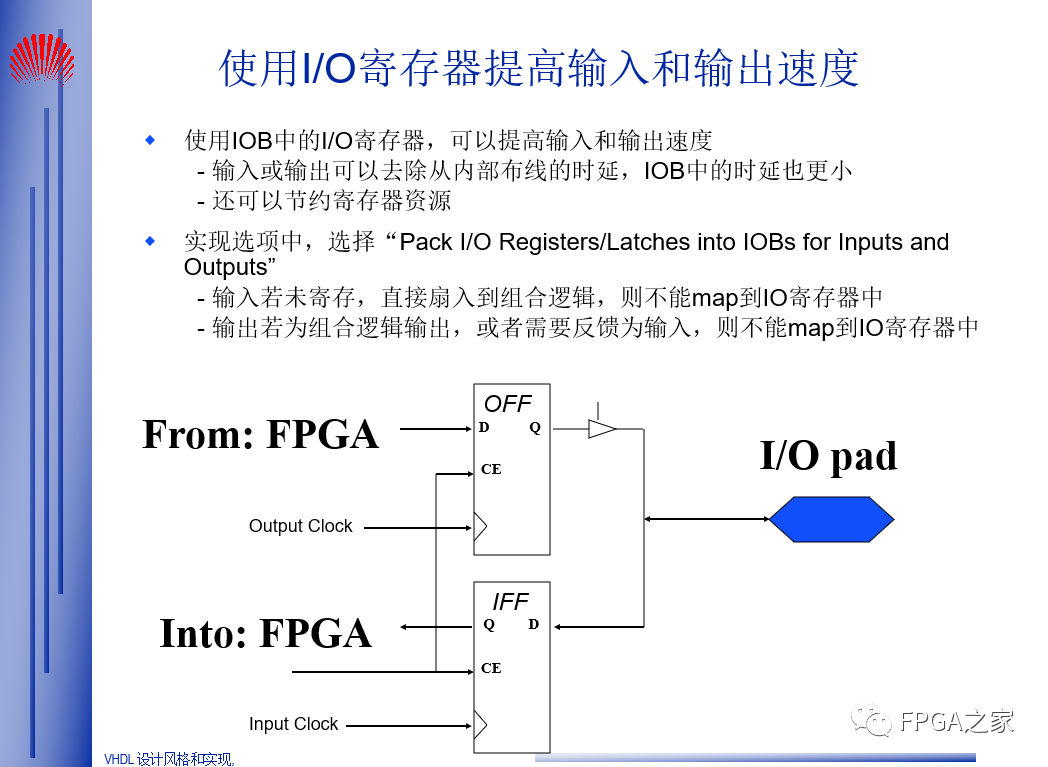

xilinx教程:基于FPGA的时序及同步设计

。 对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。在CPLD/FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动的单个主时钟去控制设计项目中的每一个触发器。 只要

2012-03-05 14:29:00

使用FPGA进行CAN通信,需不需要进行位同步

CAN里有一个位同步的概念,我以前用STM32时,还有专门用于做位同步的结构体请问我现在用FPGA作CAN,需不需要设计位同步?还是外接的独立CAN控制器自己本身就有位同步

2018-10-10 09:35:45

做多通道数据同步采集用哪个系列的fpga功耗低?

项目里用到fpga和单片机,采样率24bit100kHz。使用fpga一个是用来GPS PPS时钟同步,一个是多通道A/D数据同步采集(起始沿和clk时钟同步),采集后存到RAM里,采满后通知单

2018-11-06 09:35:33

关于FPGA设计的同步信号和亚稳态的分析

同一个时钟域中,或者来自不同的源(即使它们具有相同的时钟频率)在将信号同步到 FPGA 或不同的时钟域时,有多种设计可供选择。在xilinx fpga中,最好的方法是使用xilinx参数化宏,创建这些

2022-10-18 14:29:13

基于FPGA的时序及同步设计

数字电路中,时钟是整个电路最重要、最特殊的信号:因此, 在FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动单个主时钟去控制设计项目中的每一个触发器。同步设计时,全局时钟输入一般都接在器件的时钟端, 否则会使其性能受到影响。

2012-05-23 19:51:48

基于FPGA的时钟恢复以及系统同步方案设计

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

基于FPGA的源同步LVDS接收正确字对齐实现方法

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

多个FPGA小系统板的同步问题。

我想做多个FPGA的时钟同步,目前的想法是用一个FPGA的内部时钟,复制到外接IO口,接到另一个FPGA的外部时钟引脚,波形有较小的相移但是可以保证同步。想问一下可以复制多次,驱动多个FPGA的同步吗。对驱动能力有什么要求?其中每一个FPGA都用的是一个EP4CE的最小系统板。

2019-01-21 15:07:41

如何利用FPGA设计提取位同步时钟DPLL?

信息。自同步法又可以分为两种,即开环同步法和闭环同步法。开环法采用对输入码元做某种变换的方法提取位同步信息。闭环法则用比较本地时钟和输入信号的方法,将本地时钟锁定在输入信号上。闭环法更为准确,但是也更为复杂。那么,我们该怎么利用FPGA设计提取位同步时钟DPLL?

2019-08-05 06:43:01

如何避免FPGA内部操作和ADC数据之间的同步问题?

我们建议的设置如下:希望ADC工作在200 MHz,采样速率为200 MSPS。最初,为了避免FPGA内部操作和ADC数据之间的同步问题,我们计划从FPGA驱动ADC输入时钟。现在我们担心高采样率

2020-08-25 09:23:10

求教FPGA准确采集同步信号

请教各位大大:我最近做FPGA采集100MHz的信号,另一路同步触发。但触发信号上升沿在40ns左右,最后导致信号波形左右晃动。请问在FPGA中如何处理可以准确采集到触发信号,排除左右晃动的情况?

2013-03-06 00:22:42

求解,现在是一个FPGA新手,主要做的是高速接口设计,模块里有些RS422等

求解,现在是一个FPGA新手,主要做的是高速接口设计,模块里有些RS422等,想问问各位大神应该怎么学习 或者看些哪些高速接口的书籍吗?

2017-03-30 20:38:43

用FPGA要做pc与以太网数据的通信的话,是不是可以用lwip+ftp协议,将FPGA做成那种ftp服务器?

我现在用FPGA要做pc与以太网数据的通信的话,是不是可以用lwip+ftp协议,将FPGA做成那种ftp服务器,通过ftp协议进行文件传输?如果要做成这种效果,我应该从哪方面入手啊?感觉看了一堆协议,例程,还是没有思路。

2017-01-16 21:38:44

请问AD转换芯片数字输出A0-A11这12根数据线与FPGA连接时要做等长吗?

AD转换芯片数字输出A0-A11这12根数据线与FPGA连接时要做等长吗?

AD转换芯片时钟为70MHz,如果不需要,那么时钟速率达到多少需要做等长,就是画蛇形线!

2023-12-12 08:15:53

请问AD转换芯片数字输出A0-A11这12根数据线与FPGA连接时要做等长吗?

AD转换芯片数字输出A0-A11这12根数据线与FPGA连接时要做等长吗?AD转换芯片时钟为70MHz,如果不需要,那么时钟速率达到多少需要做等长,就是画蛇形线!

2019-01-21 15:55:14

请问DSP与FPGA之间EMIF通讯需要做数据校验吗?

请教,一般DSP与FPGA之间EMIF通讯需要做数据校验吗?如果需要的话采用什么校验方式呢?如果DSP采用的是DMA读写,那传错一个数据就得把那一堆数据重新传了,这样会不会影响实时性呢?

2020-07-30 06:24:46

请问我需要将FPGA外部引脚的频率与内部FPGA时钟同步吗?

计算FPGA外部引脚的频率。我需要将其与内部FPGA时钟同步吗?内部参考时钟以60Mhz运行,外部频率在10khz到15khz之间变化,不同步的外部频率是否会导致错误或问题?以上来自于谷歌翻译以下

2019-06-18 09:37:29

EasyGo FPGA Solver

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

基于FPGA 的OFDM 宽带数据通信同步系统设计与实现

基于FPGA 的OFDM 宽带数据通信同步系统设计与实现:正交频分复用(OFDM)是第四代移动通信的核心技术,本文介绍了一种基于FPGA的OFDM 宽带数据通信同步系统的设计方案,该方案为OFDM

2009-06-25 08:18:06 44

44

44

44基于FPGA的GPS同步时钟装置的设计

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 40

40

40

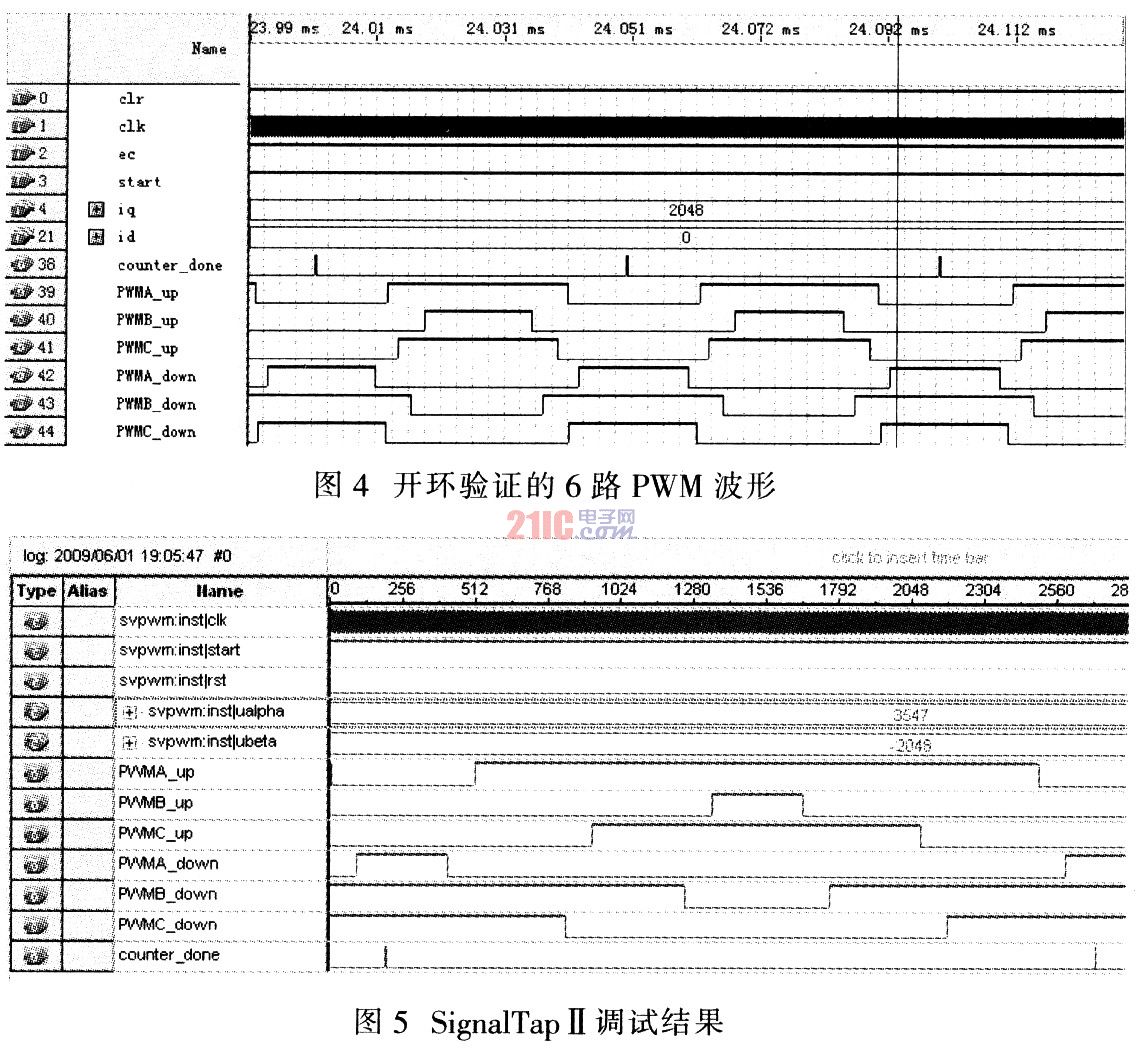

40基于FPGA 的永磁同步电动机矢量控制IP 核的研究

基于FPGA 的永磁同步电动机矢量控制IP 核的研究

摘 要论文首先分析了永磁同步电动机的数学模型及矢量控制的原理。研究了使用现代EDA 工程设计方法,在FPGA

2009-11-11 15:45:18 28

28

28

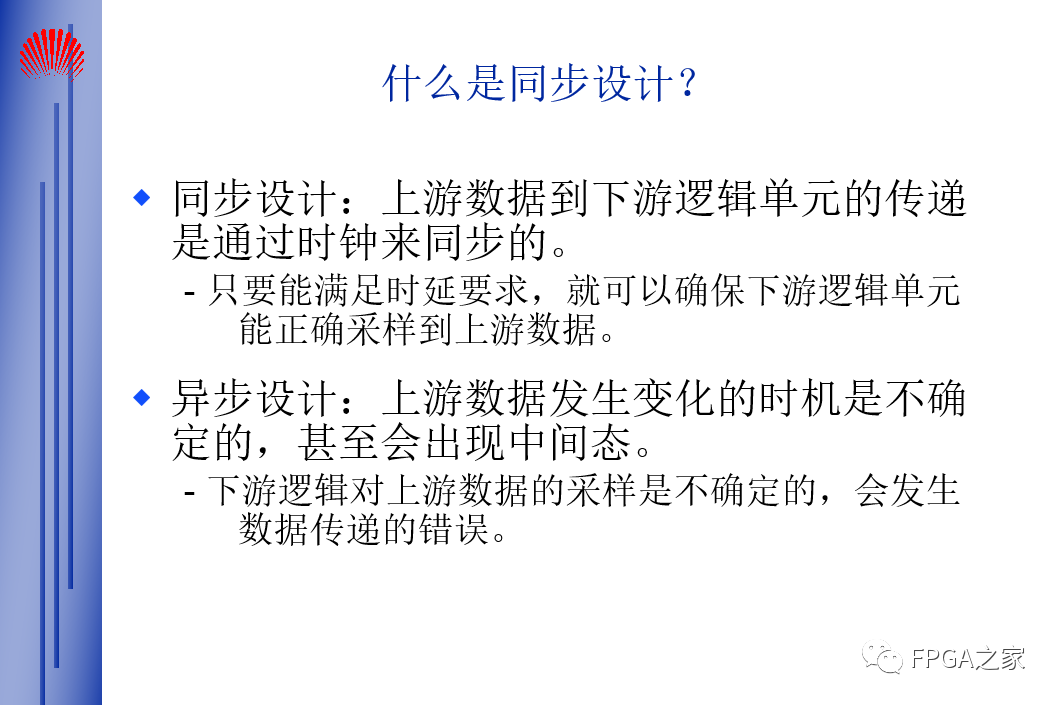

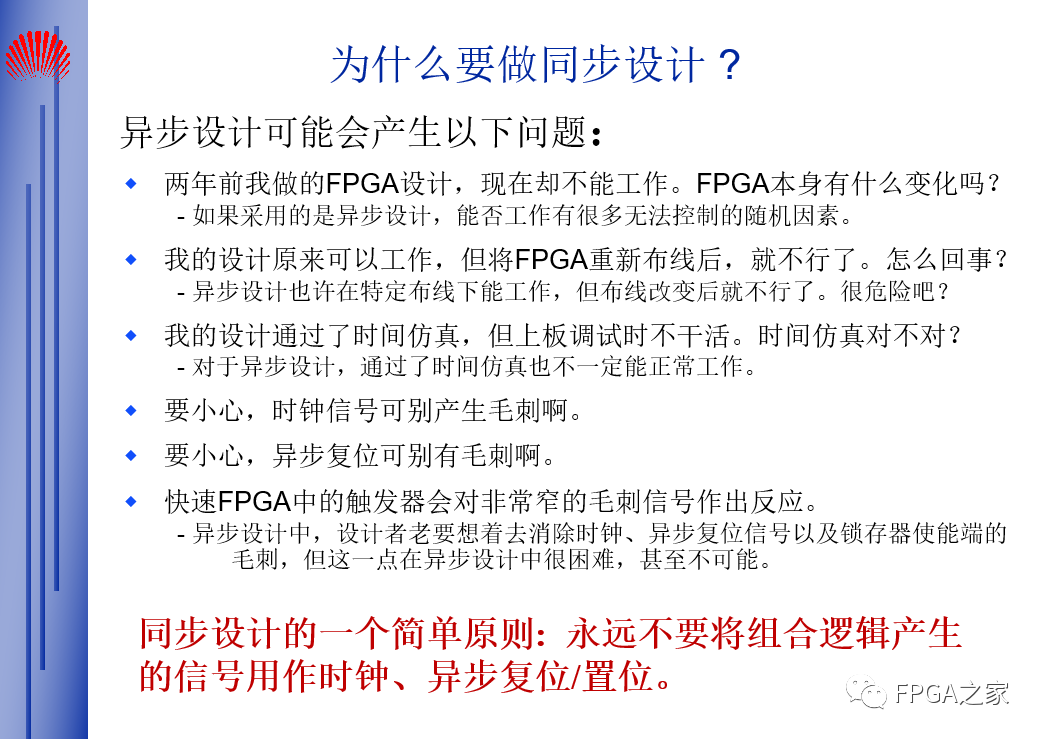

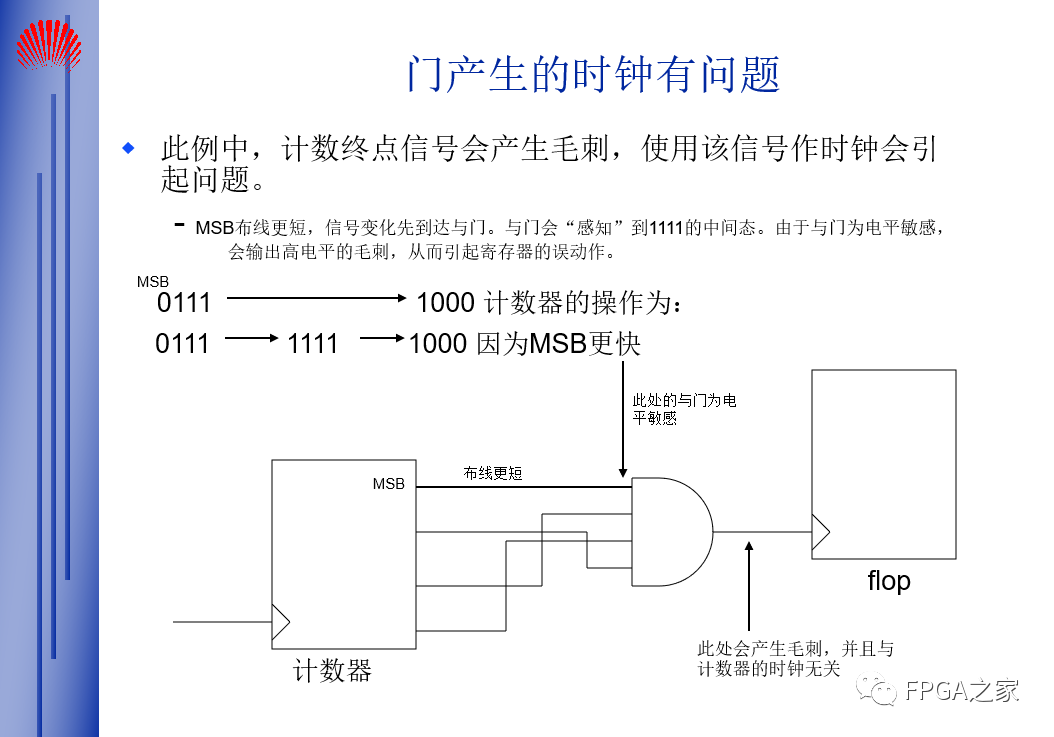

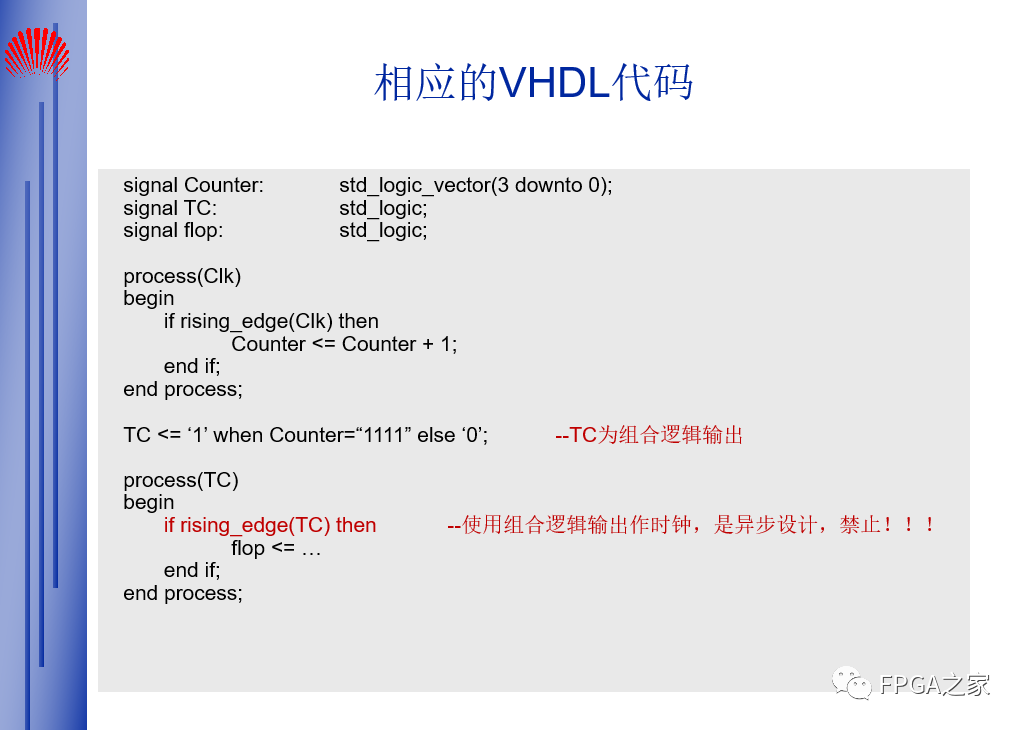

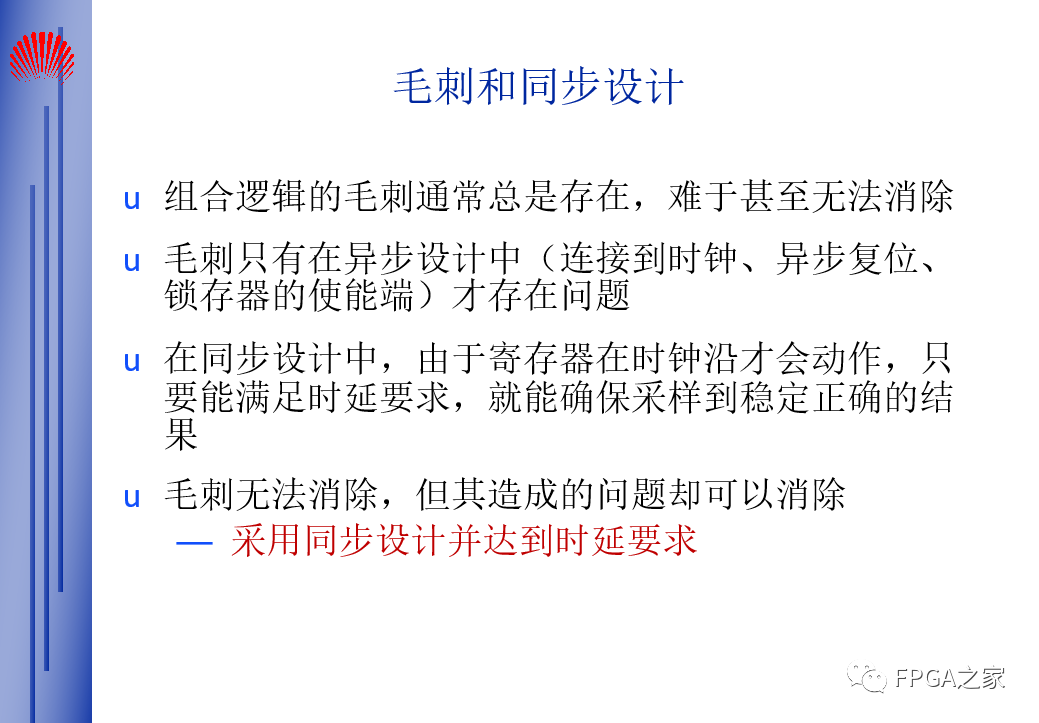

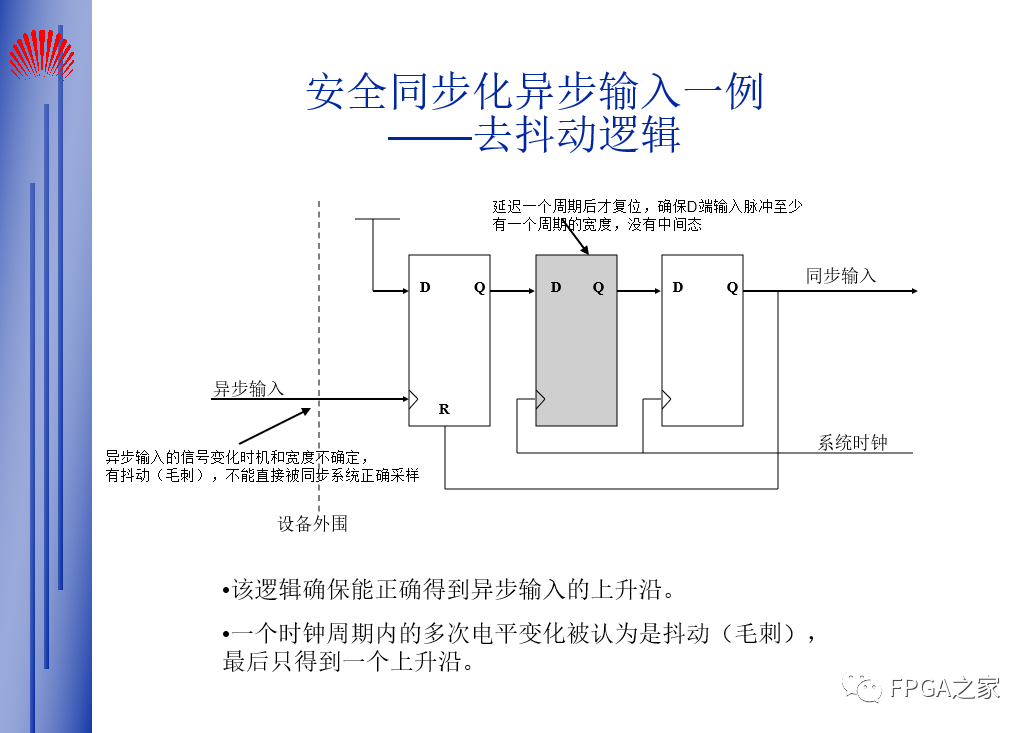

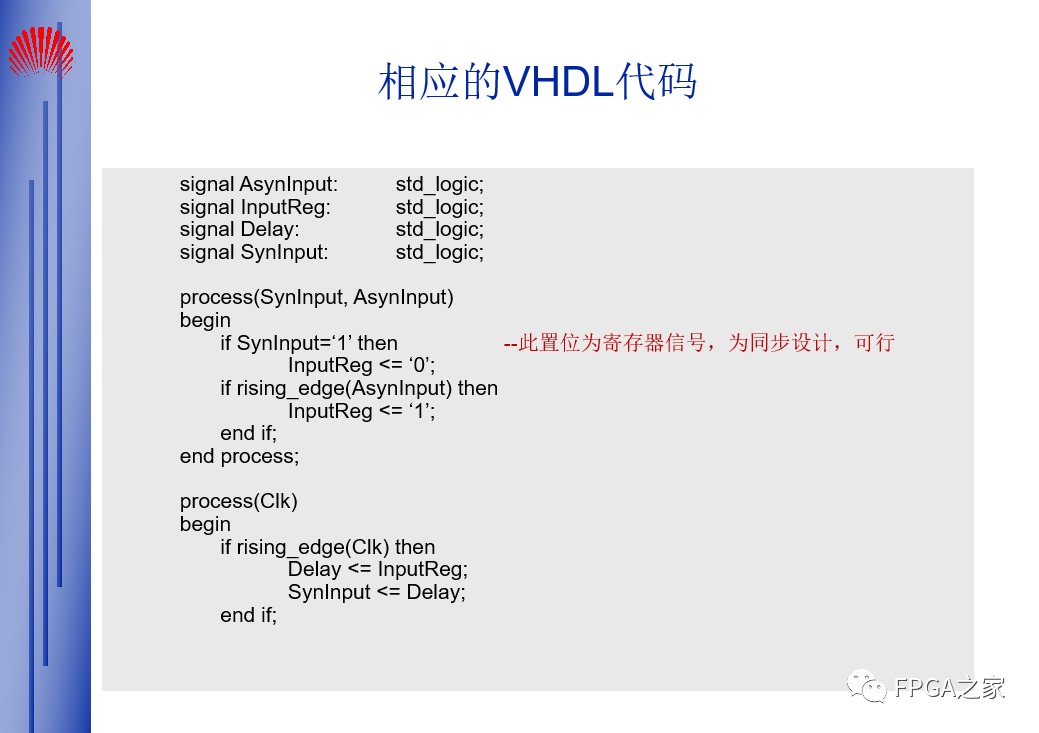

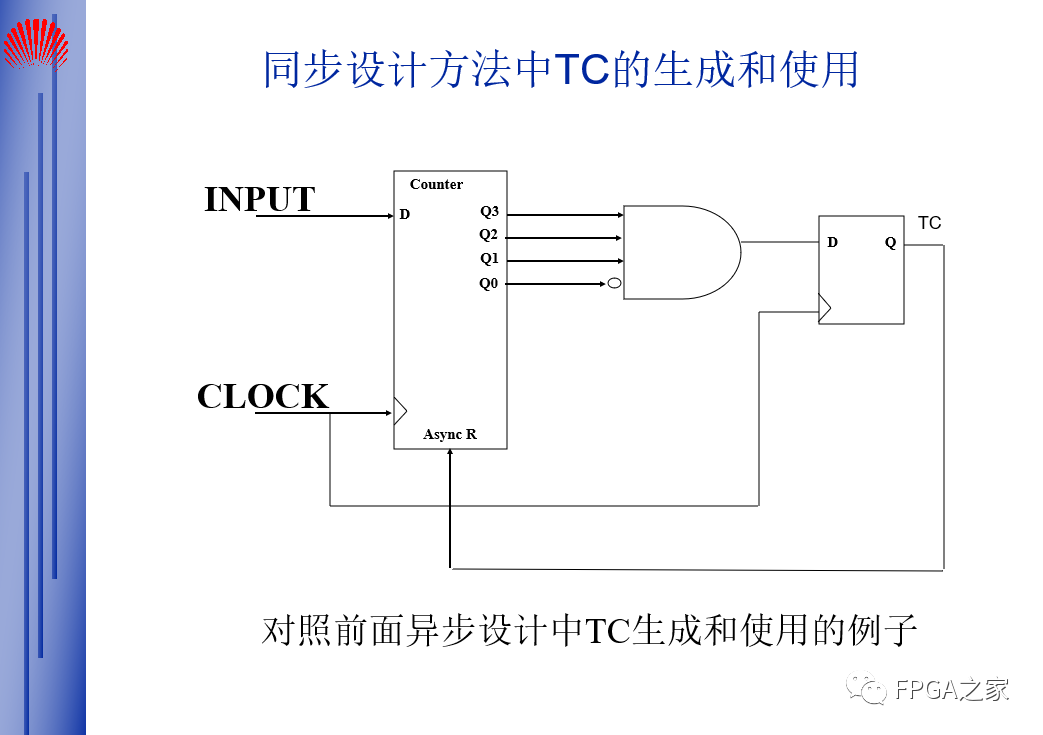

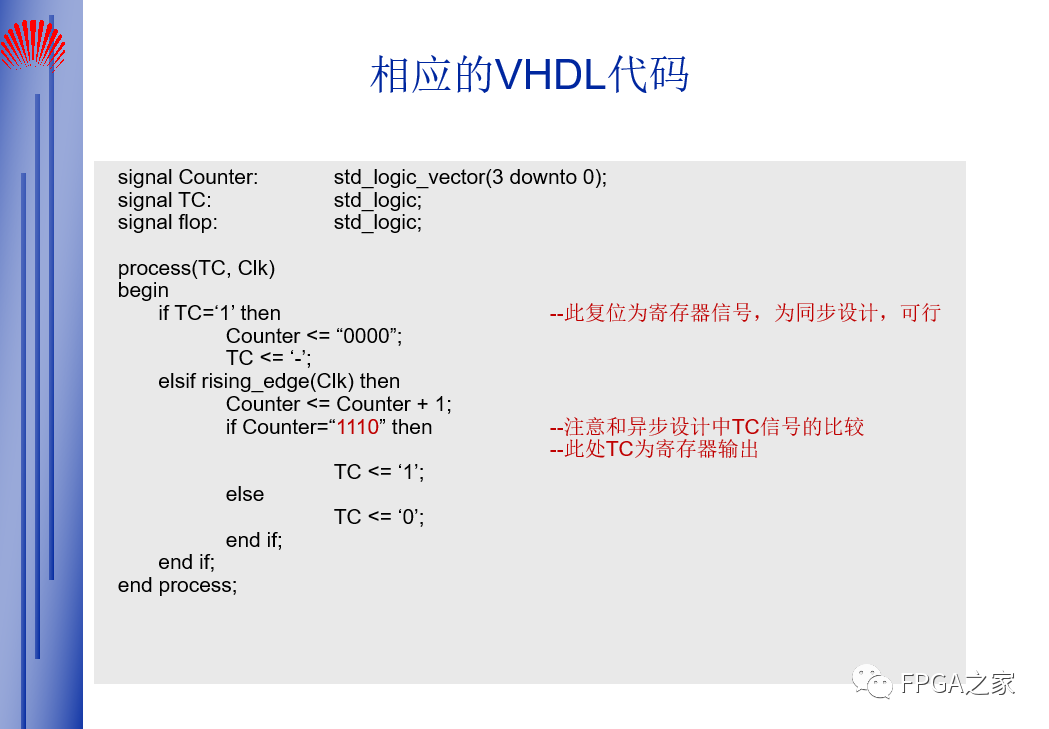

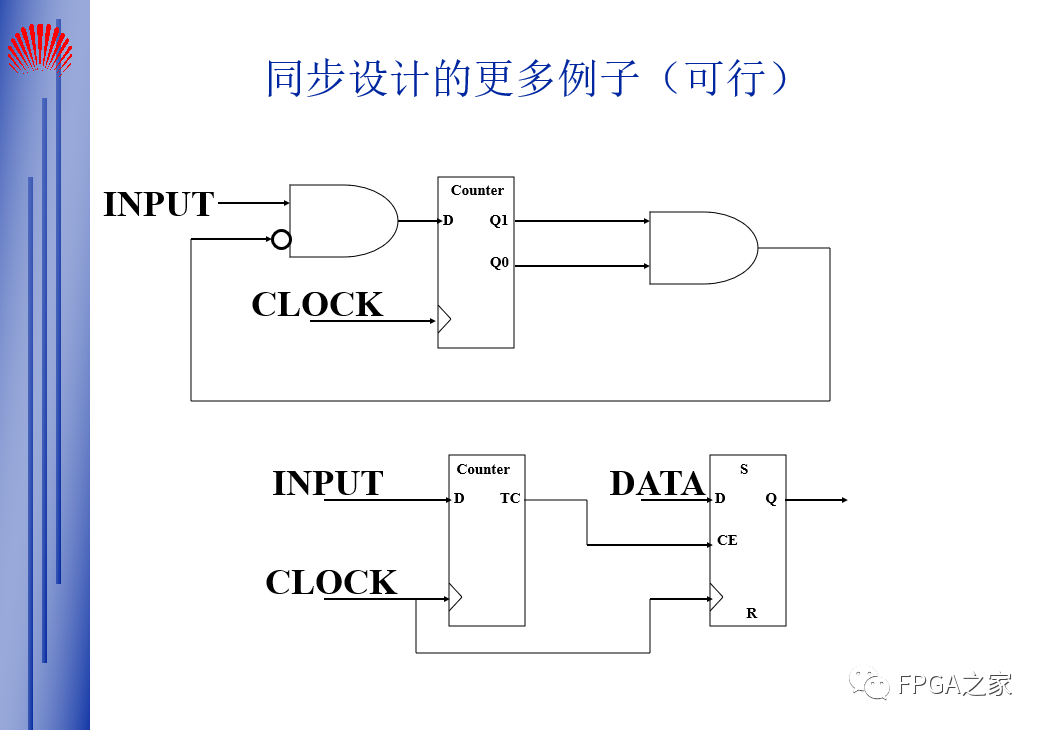

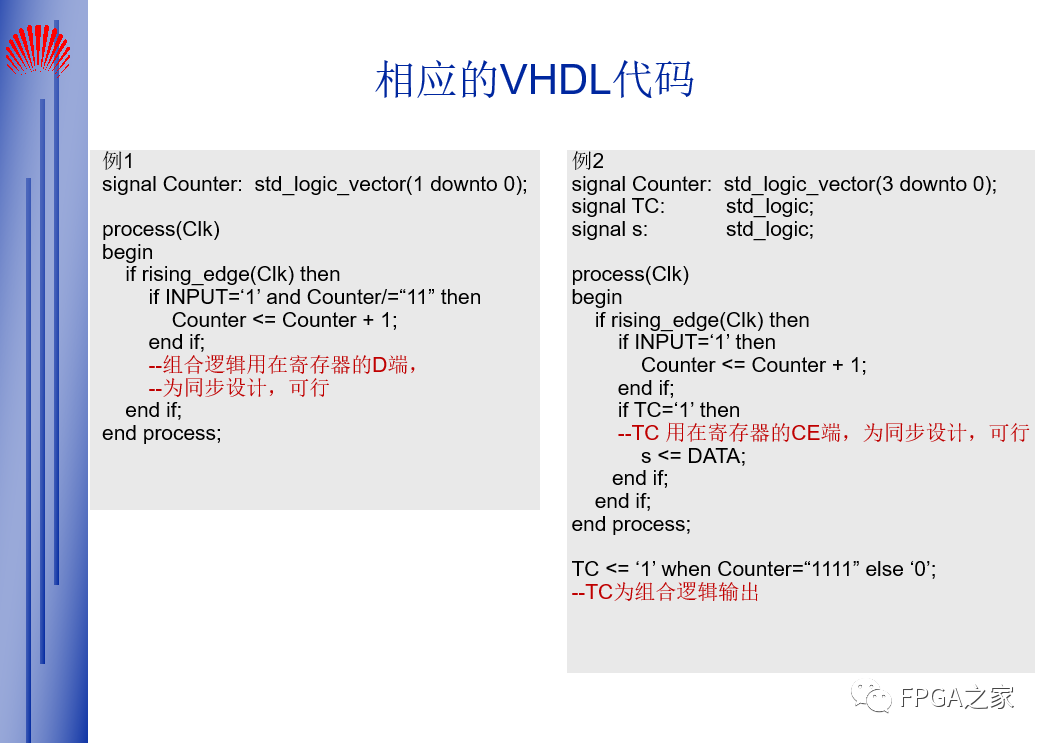

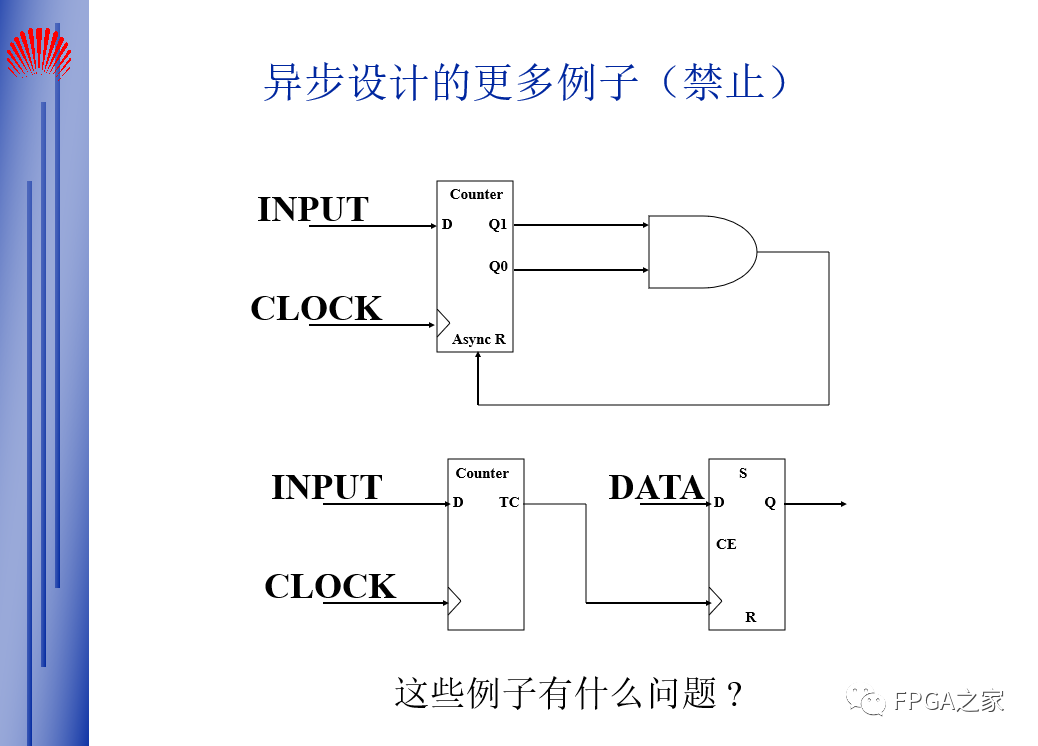

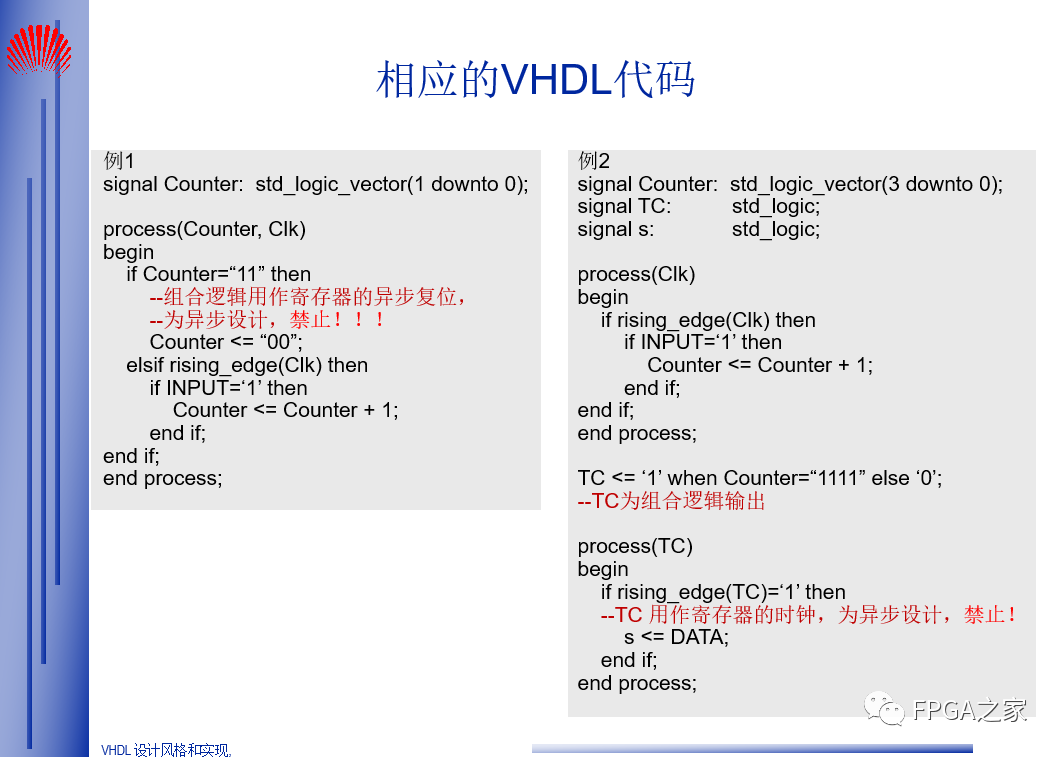

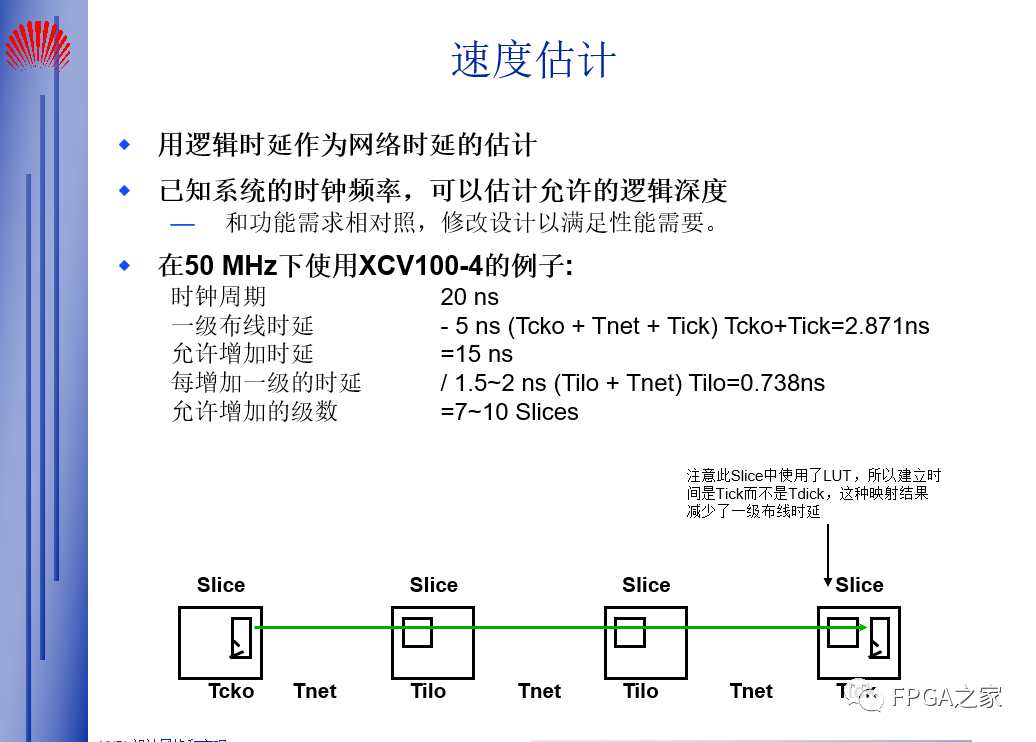

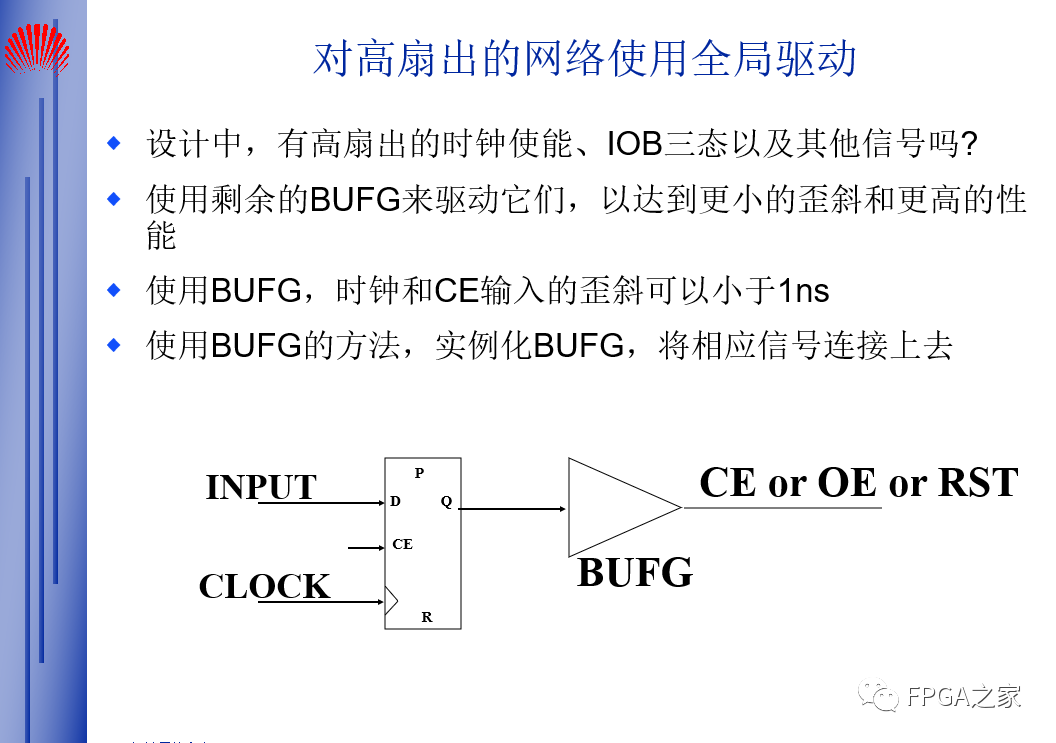

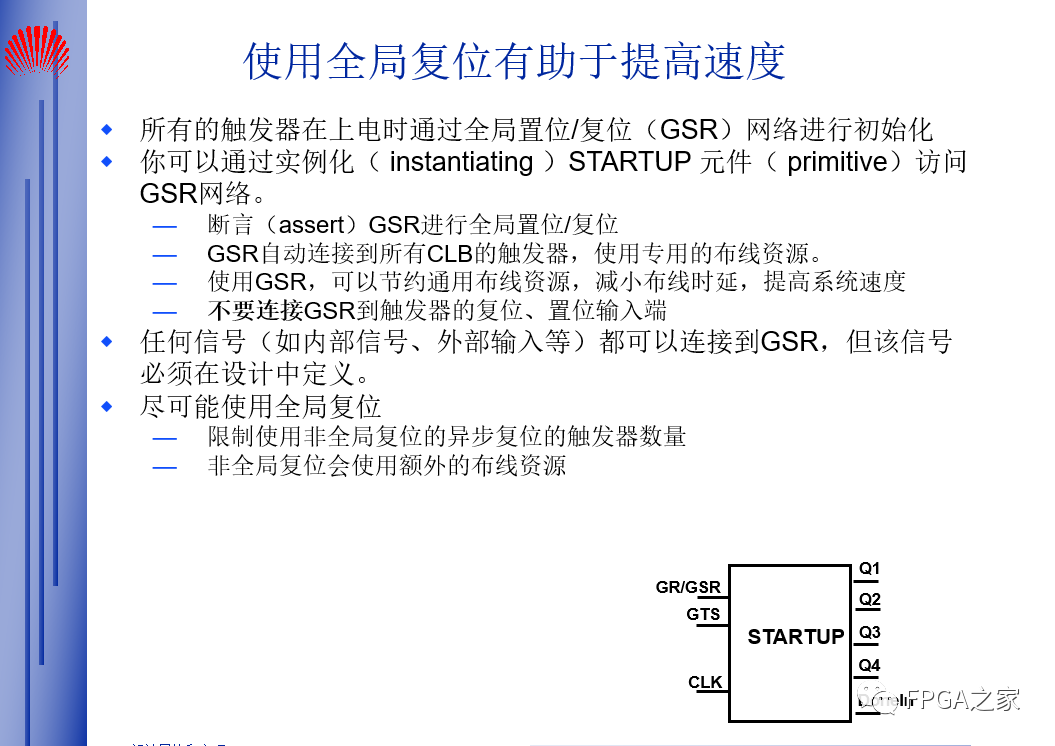

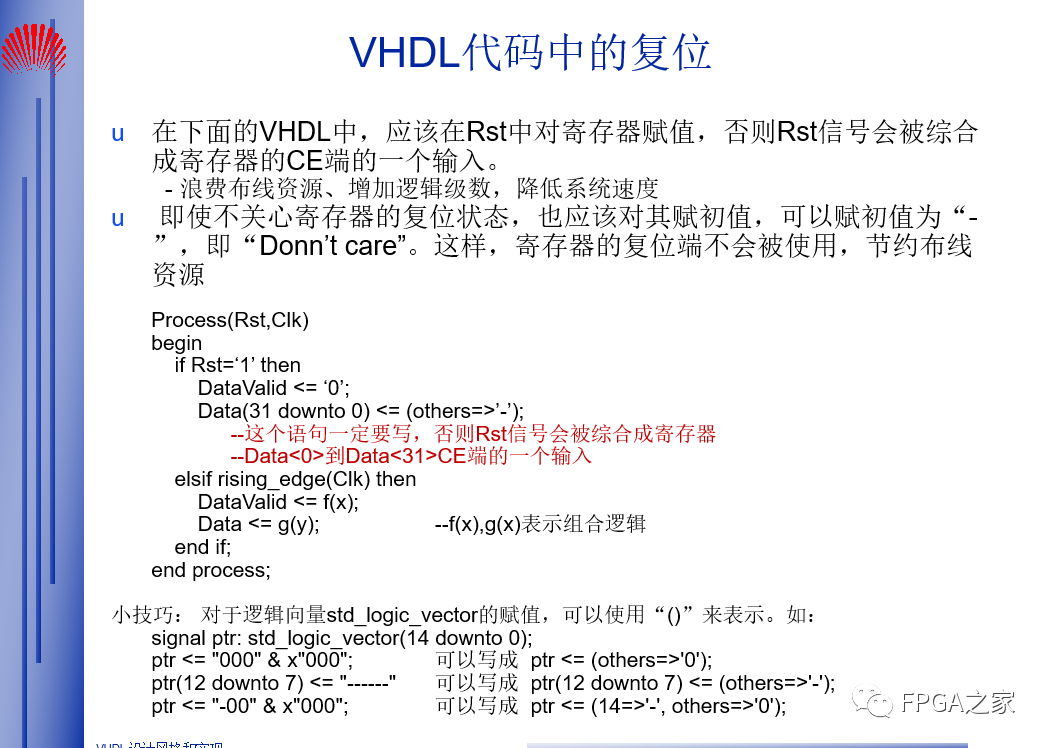

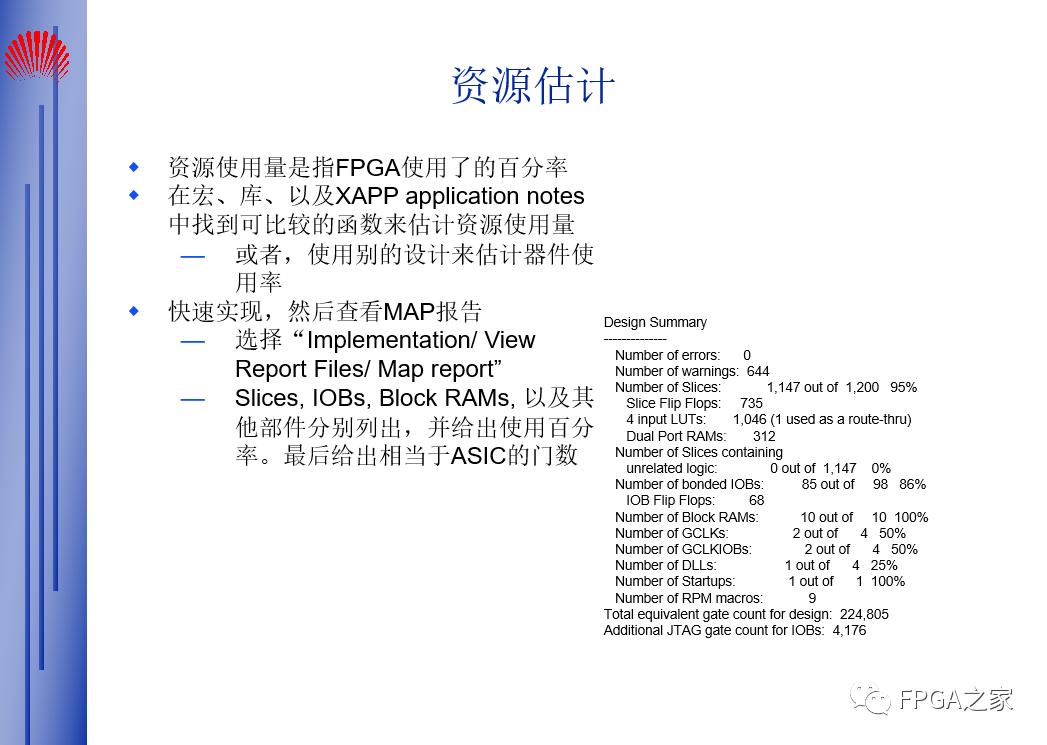

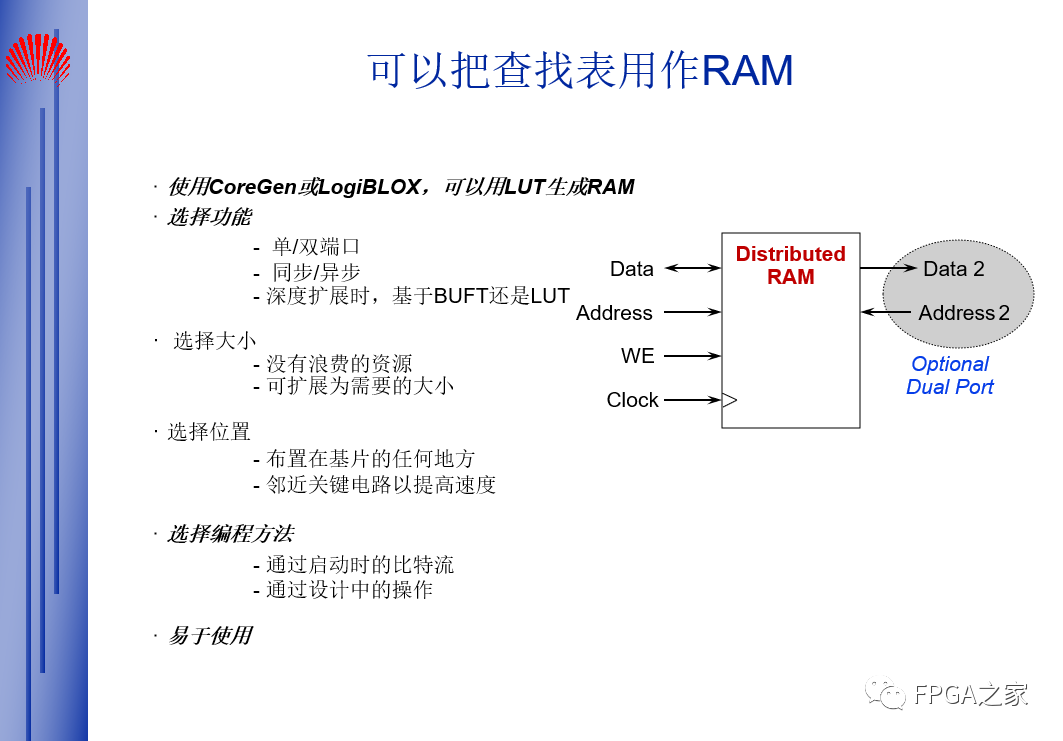

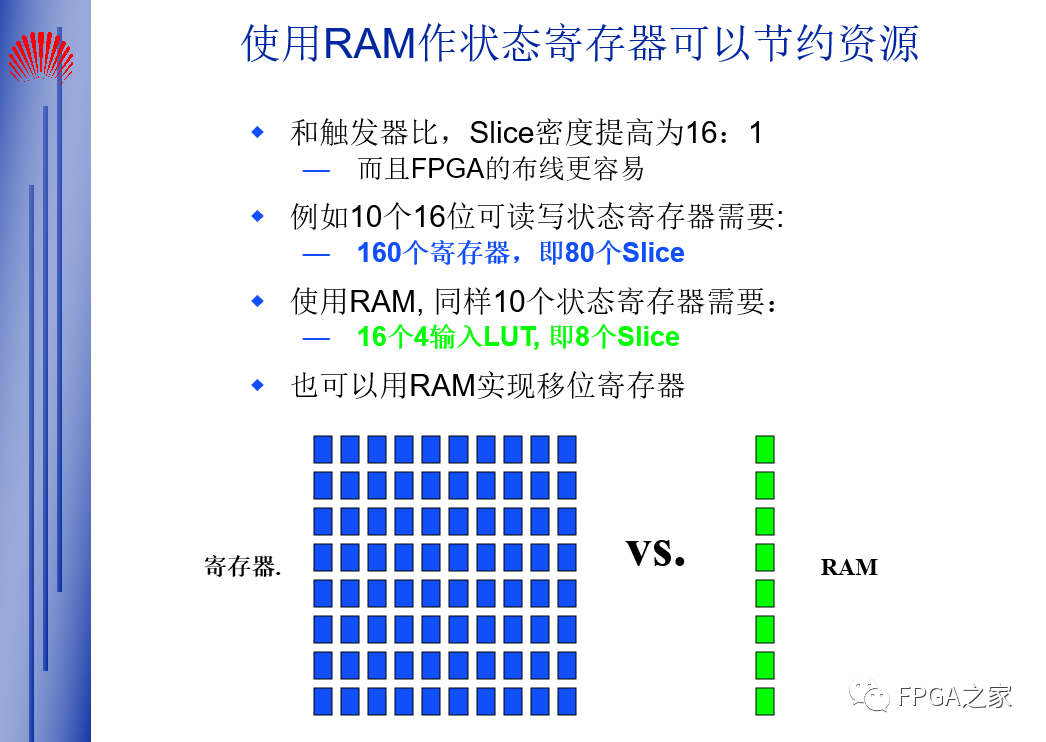

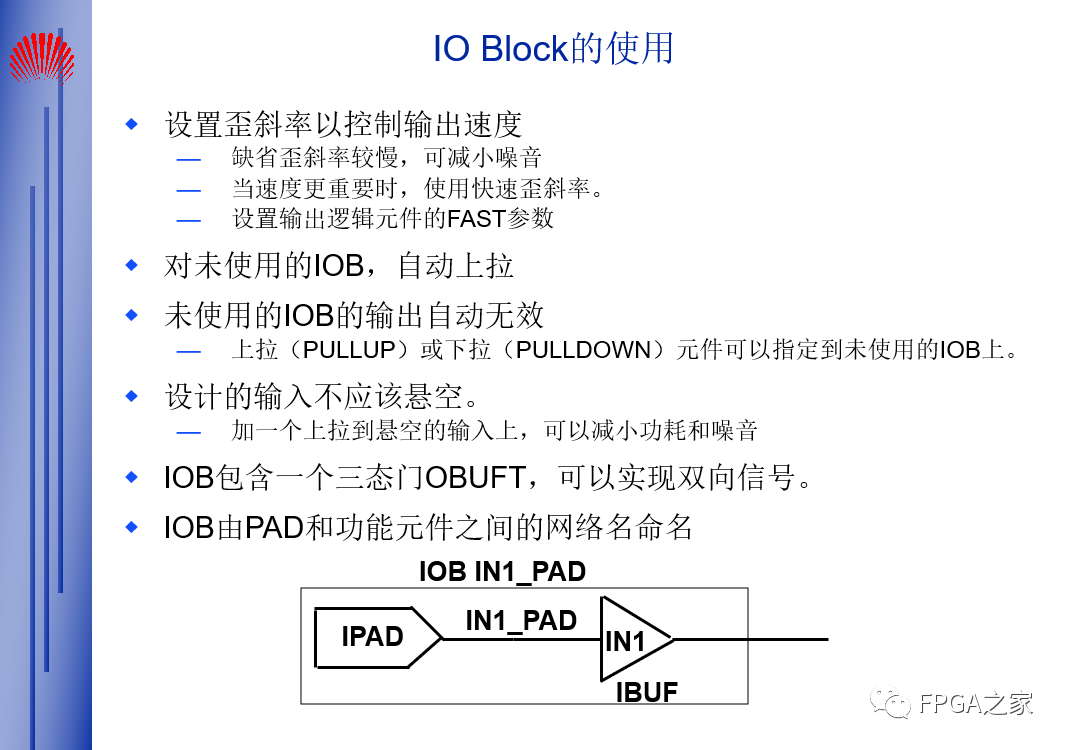

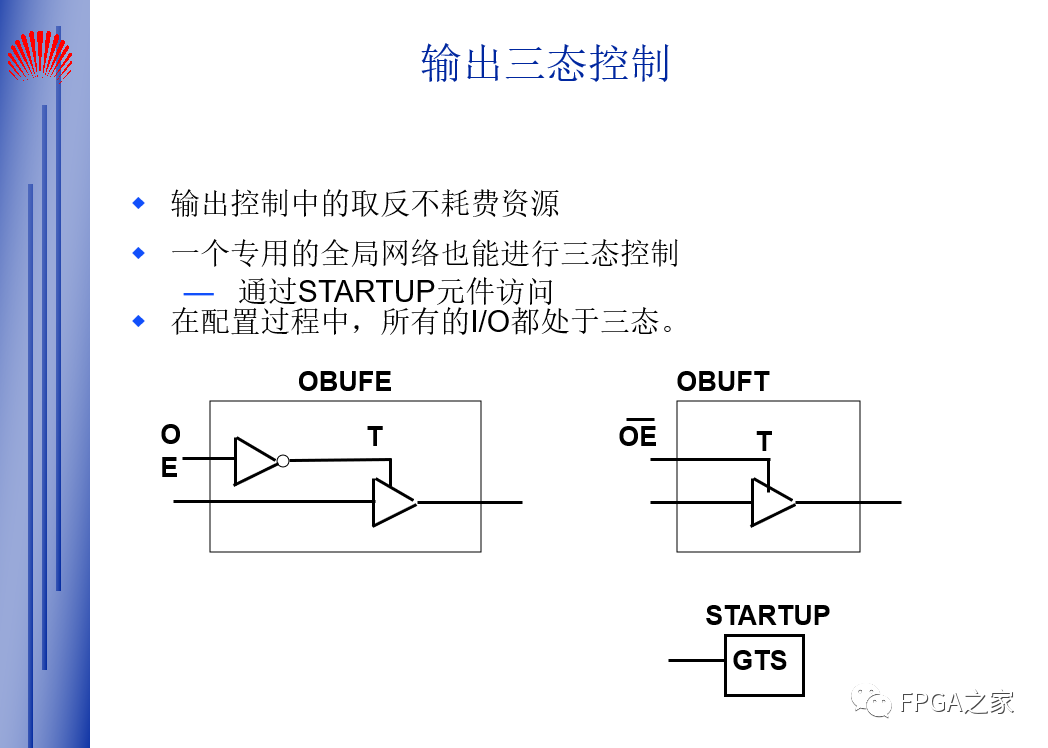

28FPGA的同步设计

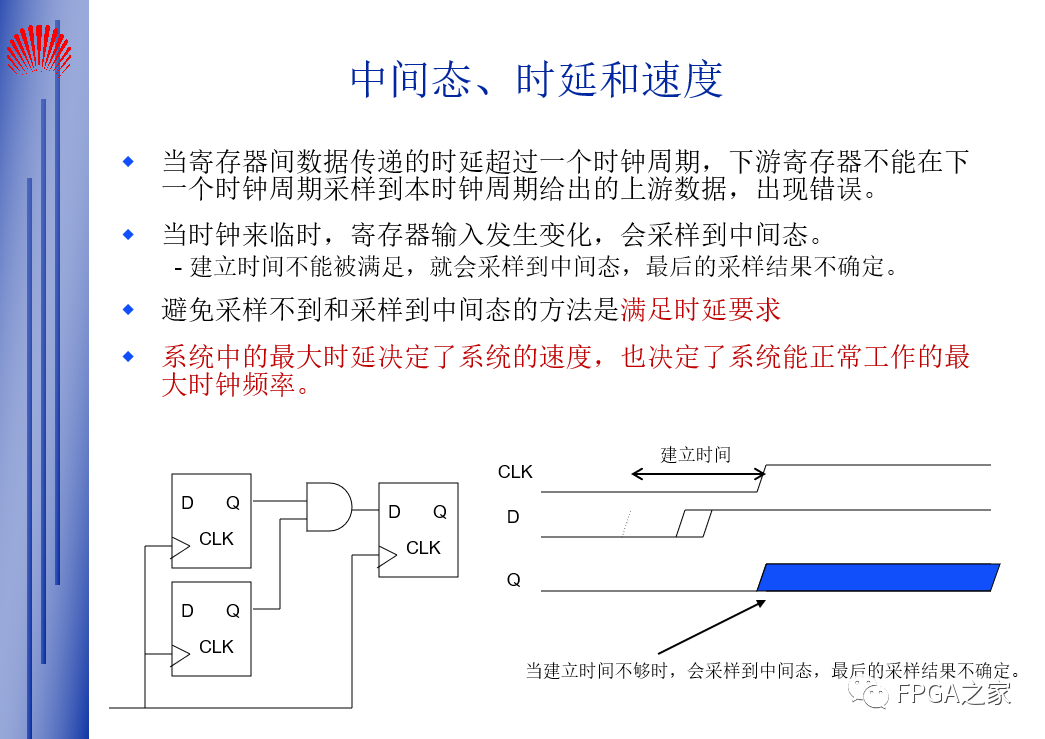

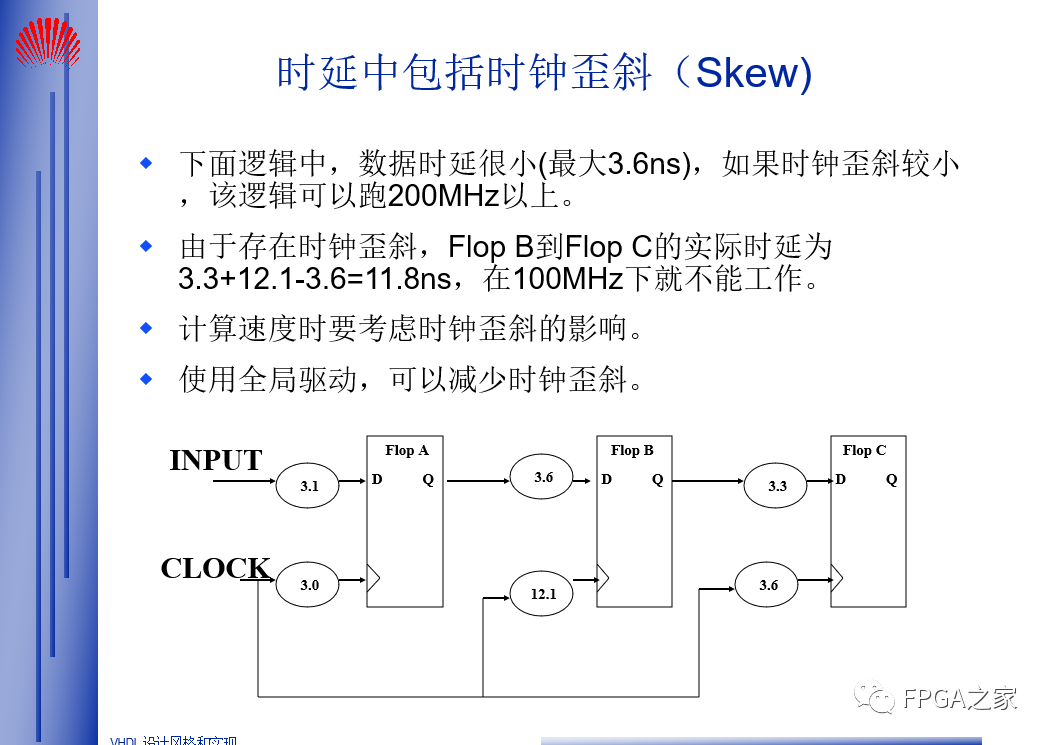

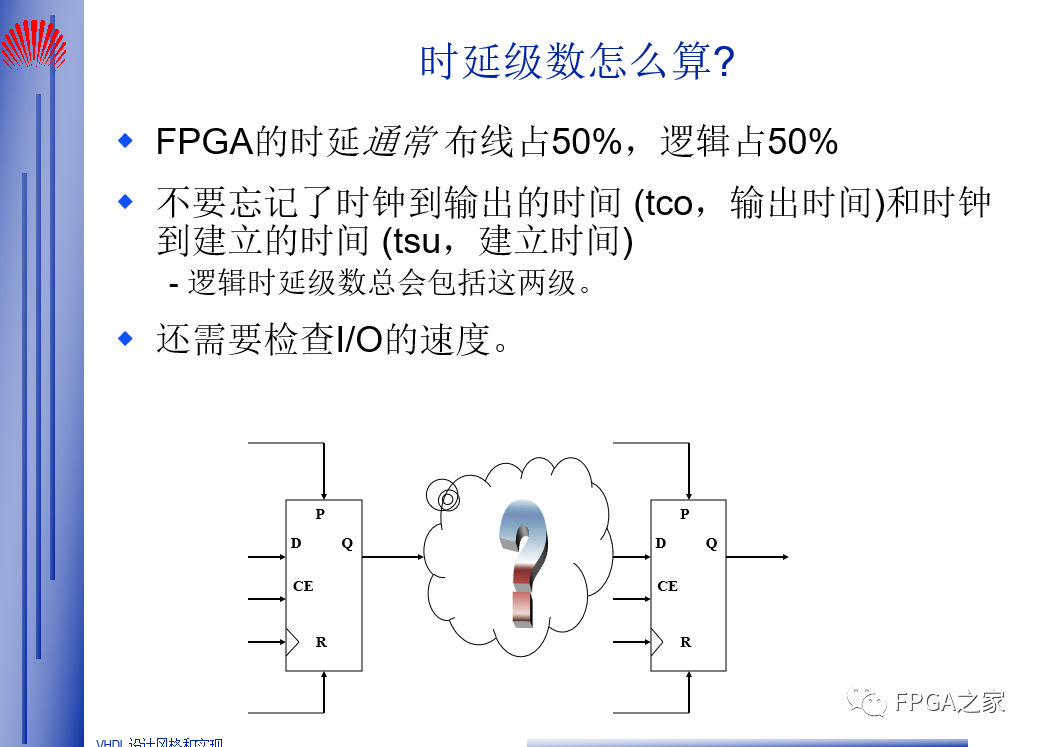

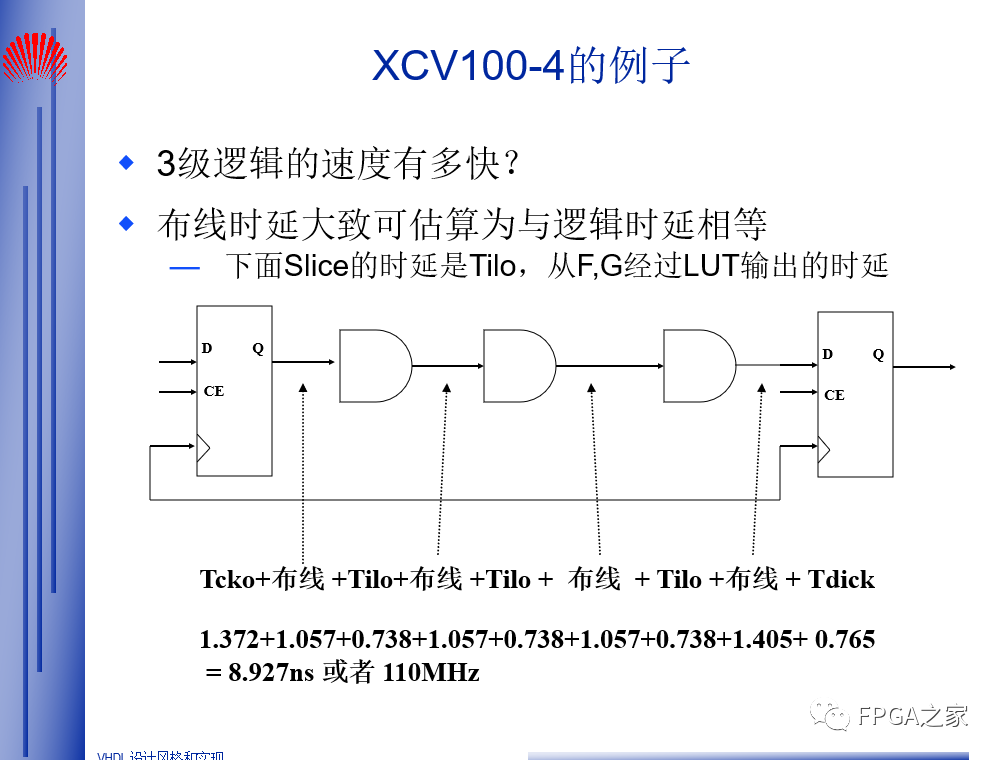

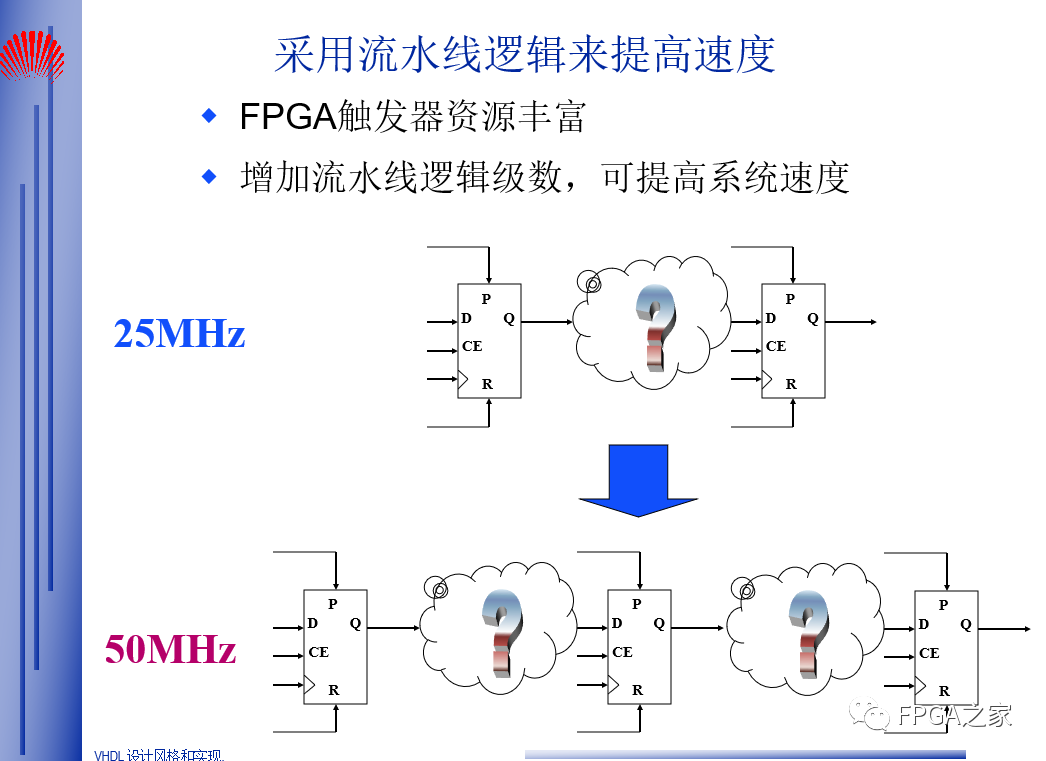

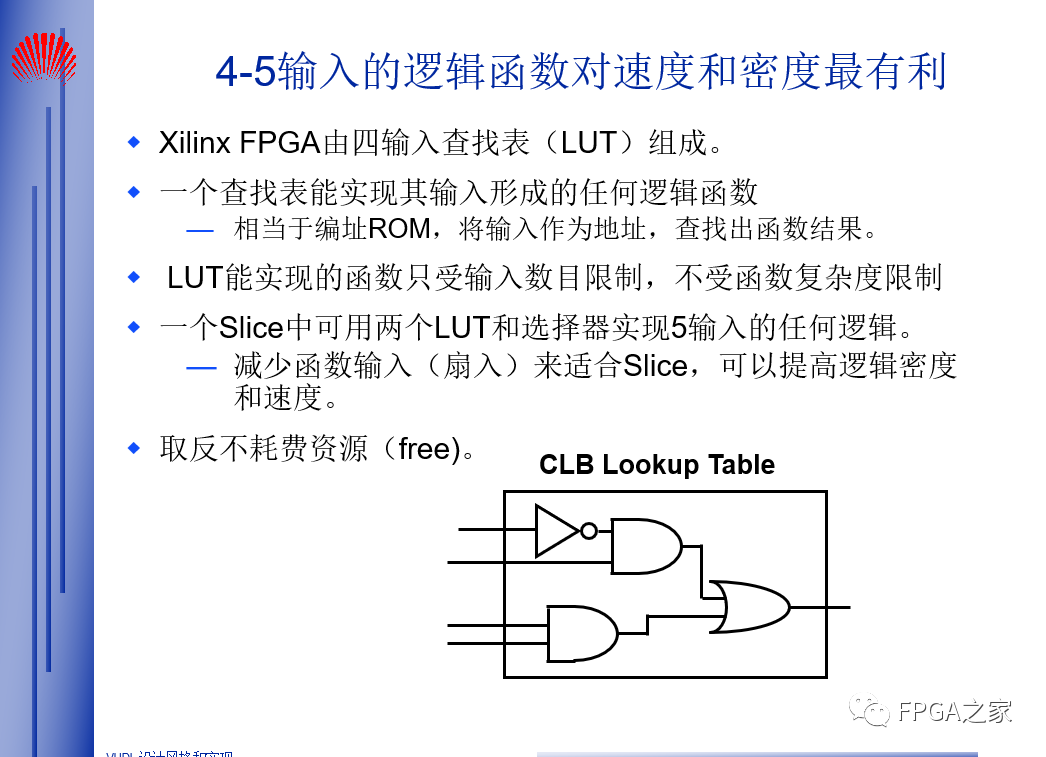

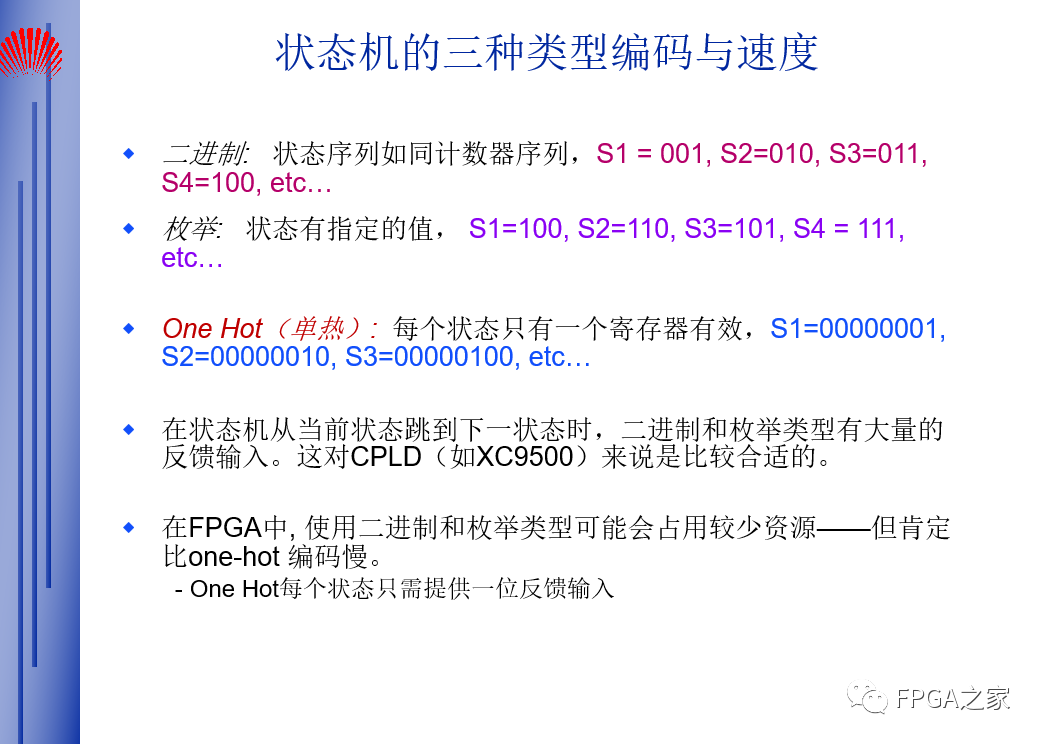

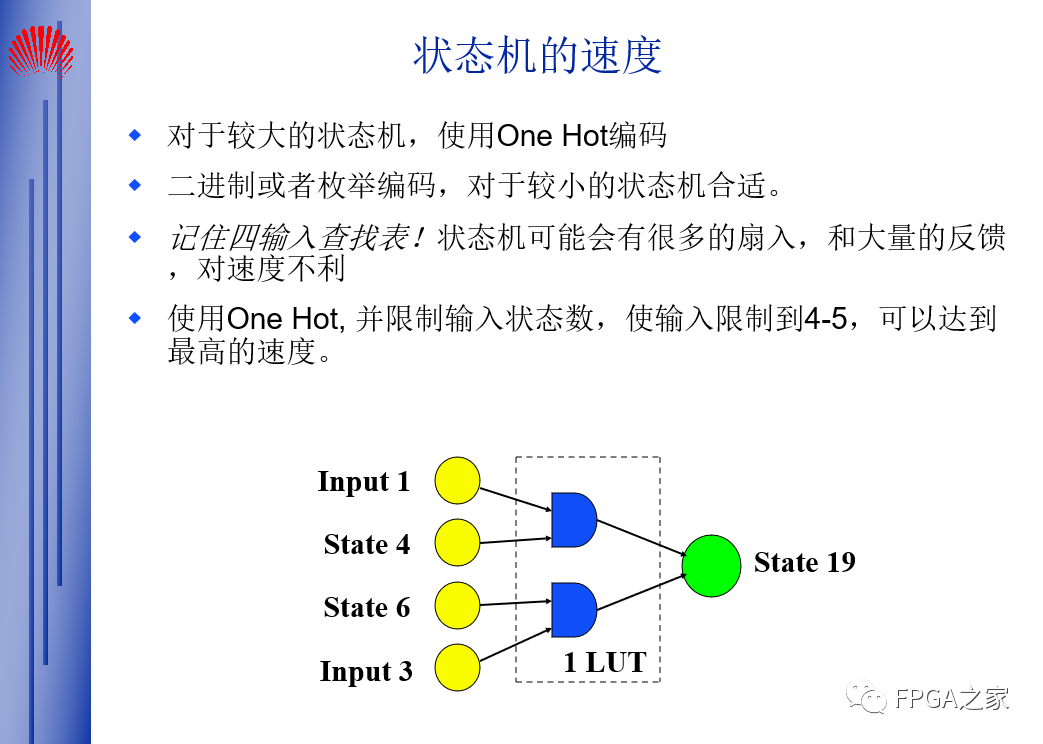

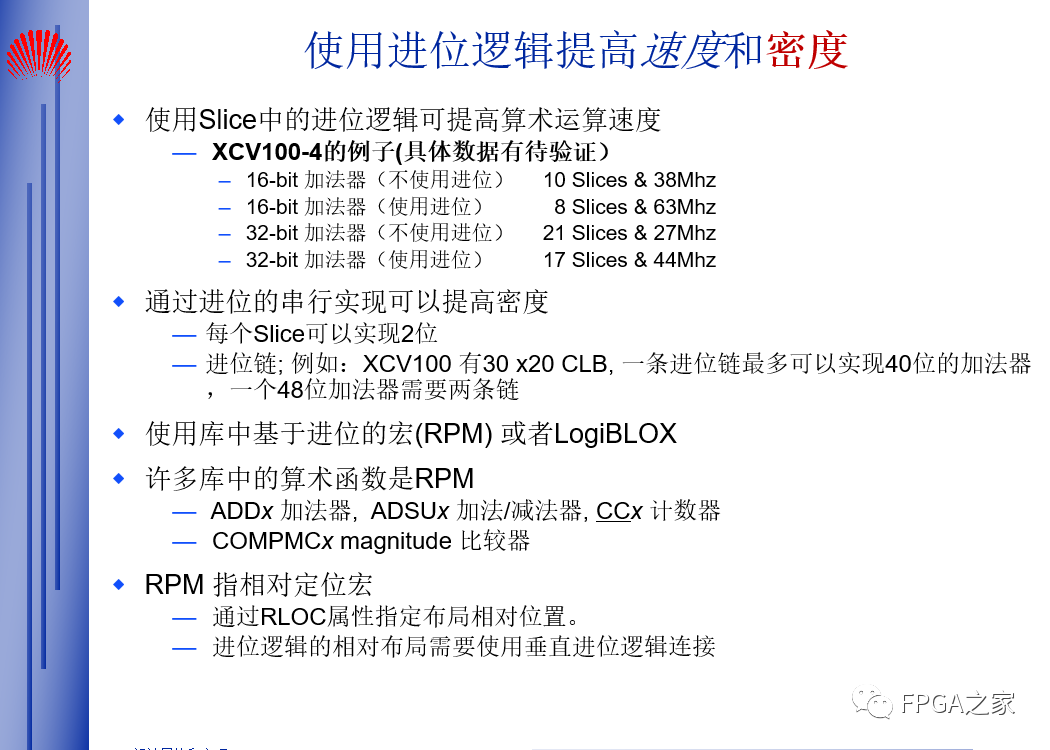

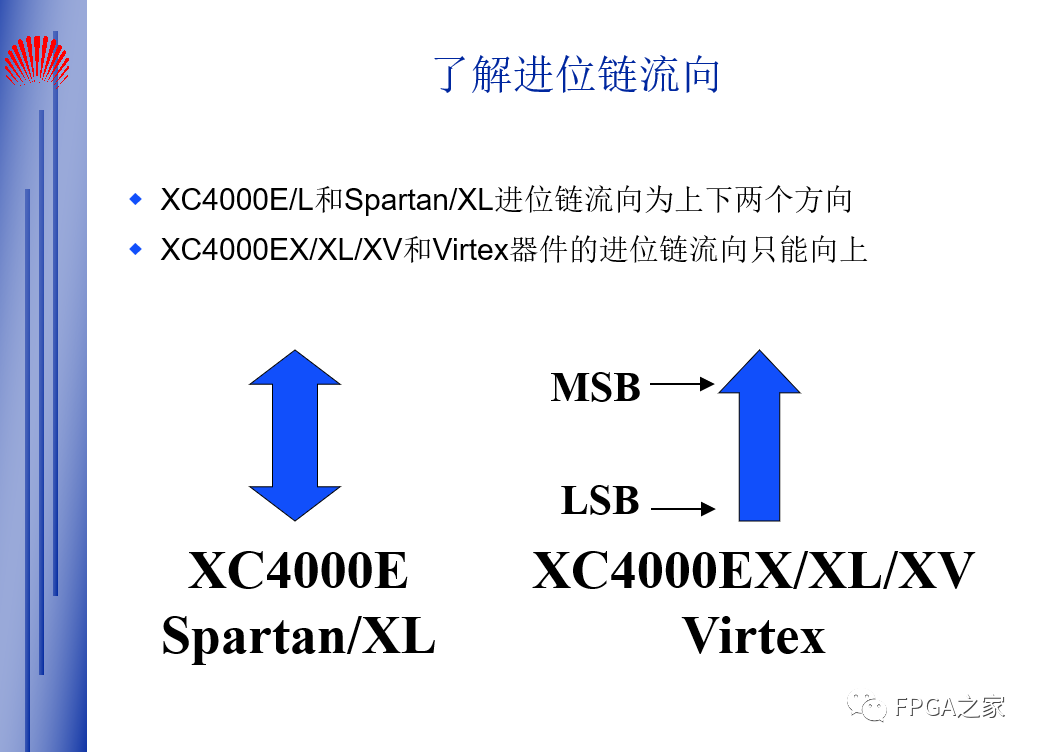

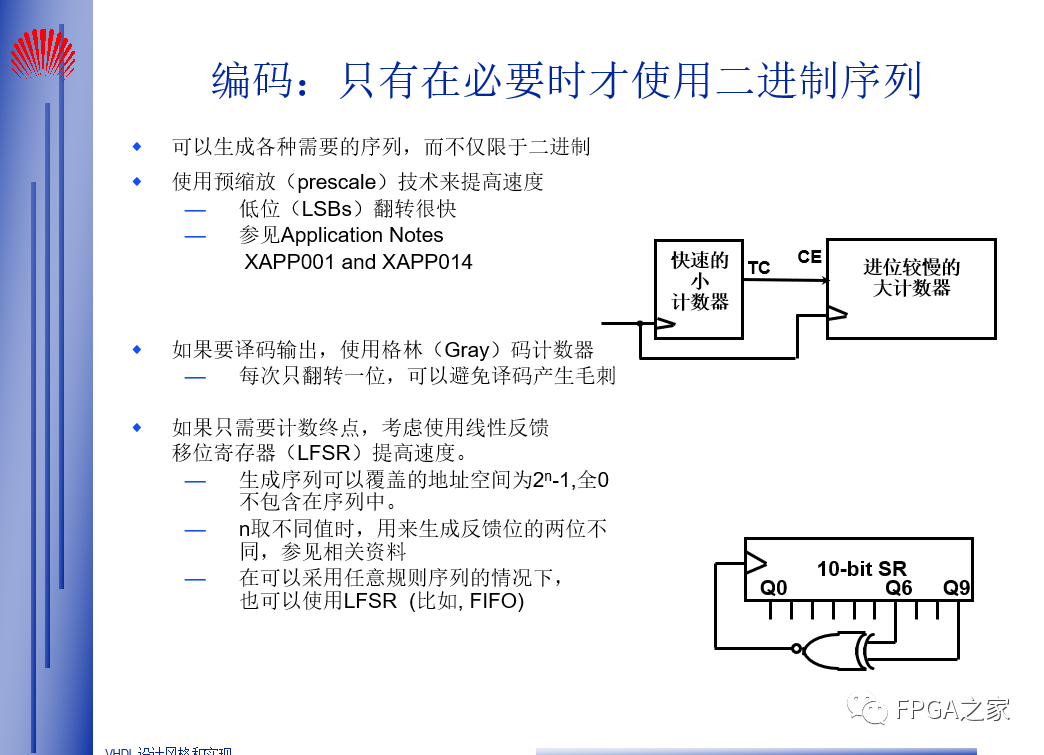

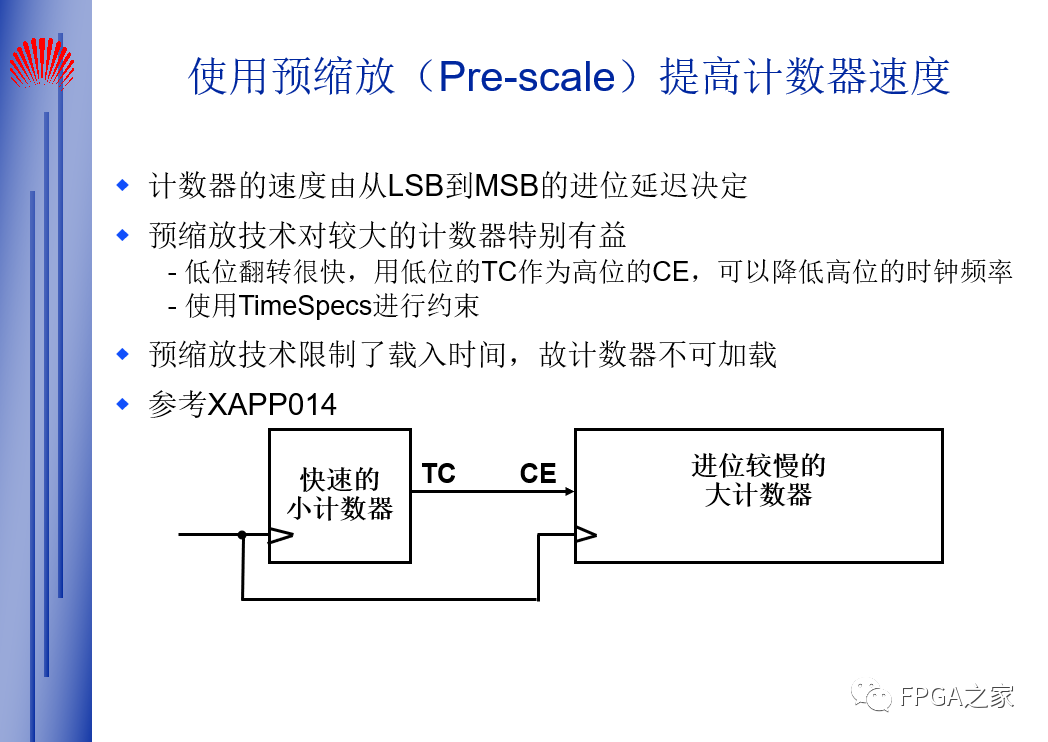

目标完成本单元的学习后你将会:•有效地利用层次•通过采用同步设计技术提高电路可靠性及性能

概览•层次化设计•Xilinx FPGA的同步设计•总

2010-01-25 08:20:16 33

33

33

33基于FPGA的快速位同步系统设计

从时分复接系统对位同步系统的性能要求出发,提出了一种基于FPGA的快速位同步系统的设计方案,给出了位同步系统的实验仿真,结果表明该系统有较快的位同步建立时间,节省了F

2010-07-28 18:13:40 20

20

20

20帧同步系统的FPGA设计

从时分复接系统对帧同步系统的性能要求出发,提出了一种采用FPGA实现帧同步系统的设计方案,重点介绍了同步保护电路的设计,并给出了FPGA设计的实验仿真,实验结果表明该电路

2010-08-06 16:46:59 24

24

24

24基于FPGA的新型高性能永磁同步电机驱动系统设计

为了研制高性能的全数字永磁同步电机驱动系统,本文提出了一种基于FPGA的单芯片驱动控制方案。它采用硬件模块化的现代EDA设计方法,使用VHDL硬件描述语言,实现了永磁同步电机

2010-10-15 09:43:46 35

35

35

35基于FPGA的光纤通信系统中帧同步头检测设计

为实现设备中存在的低速数据光纤通信的同步复接/ 分接,提出一种基于FPGA 的帧同步头信号提取检测方案,其中帧头由7 位巴克码1110010 组成,在数据的接收端首先从复接数据中

2010-10-26 16:56:54 46

46

46

46基于FPGA的多通道同步数据采集存储系统

设计一种基于FPGA的多通道同步数据采集存储系统,分为多通道同步数据采集模块和数据存储模块。系统设计采用多通道数据的同步实时采集以及坏块检测技术。多通道同步数据采集

2010-12-27 15:31:33 70

70

70

70基于FPGA的提取位同步时钟DPLL设计

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 2890

2890

2890

2890

一种高速帧同步和相位模糊估计的方法及其FPGA实现

一种高速帧同步和相位模糊估计的方法及其FPGA实现

摘要:提出仅依靠接收符号和本地同步码快速确定MPSK调制符号的帧同步,并同时估计其相位模糊值的计算方法,给

2010-01-27 09:38:17 1278

1278

1278

1278

基于802.16d的定时同步算法改进及FPGA实现

基于802.16d的定时同步算法改进及FPGA实现

0 引言

WiMAX ( Wordwide Interoperability for Mi-crowave Access)是代表空中接口满足IEEE 802.16标准的宽带无线通信系统。其

2010-02-22 09:38:31 844

844

844

844

利用FPGA的永磁同步电机控制器原理及设计

利用FPGA的永磁同步电机控制器原理及设计

概述:提出一种基于FPGA的永磁同步电机控制器的设计方案,该设计可应用于具有高动态性能要求的永磁同

2010-03-17 11:43:08 2951

2951

2951

2951

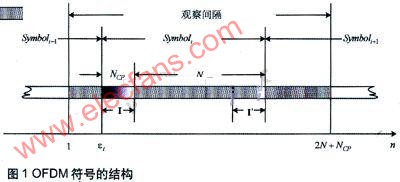

基于循环前缀的同步算法及FPGA实现

基于循环前缀的同步算法及FPGA实现

正交频分复用(OrthogonalFrequency Division Multiplexing,OFDM)技术已经成为第四代移动通信研究的热点,同时,OFDM同步又是OFDM的关键技

2010-03-23 09:27:48 1530

1530

1530

1530

FPGA上同步开关噪声的分析

FPGA上同步开关噪声的分析

概述

随着半导体技术的快速发展,近年来FPGA 的器件容量和输入输出的管脚数量都极大的增加了,例如StratixIV 器件,最大的

2010-04-12 15:09:35 2999

2999

2999

2999

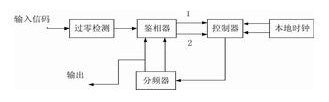

FPGA的时钟频率同步设计

FPGA的时钟频率同步设计

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速

2010-01-04 09:54:32 2762

2762

2762

2762

基于VHDL和FPGA的非对称同步FIFO设计实现

本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO,它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

2011-01-13 11:33:43 1744

1744

1744

1744光纤纵差保护同步接口的FPGA实现

摘要:同步接口是光纤纵差保护装置的重要组成部分,本文介绍了Cyclone II FPGA 在光纤纵差保护同步接口中的应 用,详细地阐述了FPGA 实现光纤纵差保护同步通信接口的原理。大规模可编

2011-04-06 16:42:11 40

40

40

40WCDMA主同步的FPGA实现

本文阐述了主同步搜索的改进型算法,并且针对这种算法提出了基于片上RAM 的实现方式,最大程度地节省了FPGA 的硬件资源,为WCDMA 同步的FPGA 实现提供了很好的解决方案。这种技术可

2011-05-14 16:45:53 30

30

30

30导频叠加OFDM同步方法的FPGA实现

导频叠加OFDM同步方法的FPGA实现,目前正交频分复用(OFDM)技术已经成为第四代移动通信研究的热点,同时OFDM同步又是OFDM的关键技术

2012-02-20 15:15:39 1765

1765

1765

1765

基于ARM和FPGA的时间同步仪控制单元设计

本文以时间同步仪的功能为出发点,设计了基于ARM和FPGA的控制系统,该系统以ARM芯片S3C2440A为控制核心,在FPGA芯片XCS30的辅助控制下,完成了时间同步仪的人机交互、参数设定、电文处

2012-05-25 14:33:54 41

41

41

41高阶QAM定时同步算法的MATLAB仿真及FPGA实现

本文针对128 QAM调制信号,设计了定时同步算法结构,并且用MATLAB做了仿真验证,最后在FPGA平台上实现了该算法。

2012-11-23 11:15:17 5895

5895

5895

5895基于ARM/FPGA的高速多通道同步数据采集解决方案(恒颐)

恒颐基于ARM+FPGA的高速同步数据采集方案,解决了数据采集的同步性问题,与以往的数据采集方案相比,具有高精度、高速率、多参数同步测量、实时处理、网络传输不受区域限制等特点

2012-11-27 10:51:24 1198

1198

1198

1198基于FPGA的跳频系统快速同步算法设计与实现

同步技术是跳频系统的核心。本文针对FPGA的跳频系统,设计了一种基于独立信道法,同步字头法和精准时钟相结合的快速同步方法,同时设计了基于双图案的改进型独立信道法,同步算

2013-05-06 14:09:20 22

22

22

22Altera全球同步推出10代FPGA和SoC

Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行发布的包括高端Stratix10和中端Arria10系列。目标是替代传统的ASSP和ASIC。

2013-06-13 14:26:14 2150

2150

2150

2150基于FPGA的同步器信号采集技术研究

针对航空测试中常用的同步器信号,提出一种基于嵌入式系统的双通道同步器信号采集系统。系统以同步器专用芯片对信号进行预处理,解析出数字量的角度和角速率,以FPGA为控制器进行数据处理,实现两路角度和角速率测量功能。经过仿真实验和系统调试,结果表明此系统能够稳定高效的采集和处理同步器信号。

2015-12-04 15:03:44 0

0

0

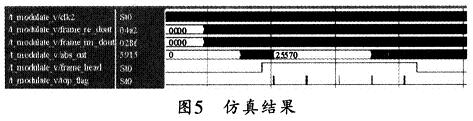

0采用FPGA实现同步、帧同步系统的设计

为了能在GPS接收端获取正确导航电文,研究了CJPS接收机位同步、帧同步的基本原理和实现方式。提出一种采用FPGA来实现位同步、帧同步系统的设计方案。使用Xilinx开发软件,通过Verilog代码

2017-11-07 17:13:39 10

10

10

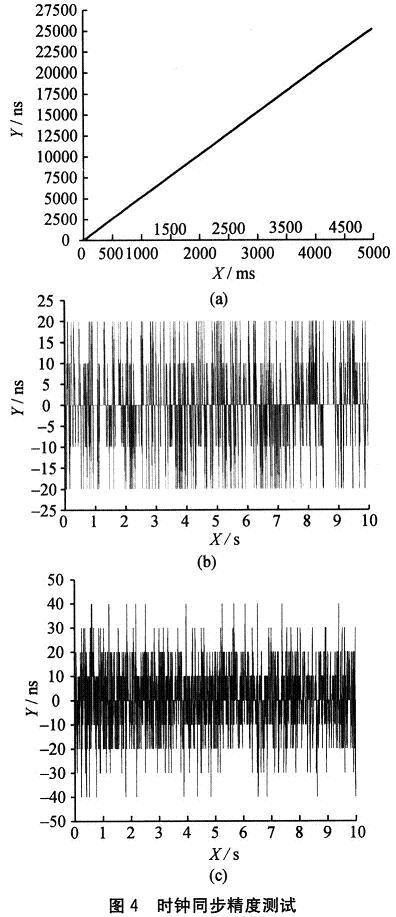

10基于FPGA的高精度同步时钟系统设计

介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在FPGA

2017-11-17 15:57:18 6196

6196

6196

6196

FPGA设计中的异步复位同步释放问题

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 1989

1989

1989

1989Xilinx FPGA的同步复位和异步复位

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091

6091

6091如何利用FPGA设计一个跨时钟域的同步策略?

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟

2018-09-01 08:29:21 5302

5302

5302

5302

基于FPGA实现电路的同步提取性能设计

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。本文给出了一种基于fpga的数字锁相环位同步提取电路。

2019-04-19 08:24:00 3113

3113

3113

3113

如何使用FPGA进行两路视频同步播放系统的设计

为了实现基于嵌入式系统的两路视频的同步播放控制,本文提出了根据图像内容检测达到两路视频同步播放控制的设计思想。根据该思想设计了基于FPGA 的实验电路,构建了完整的系统实验硬件平台。该系统平台的建立,证明了基于嵌入式电路的以图像内容检测为手段的两路图像同步播放控制的可行性。

2018-11-06 19:35:28 7

7

7

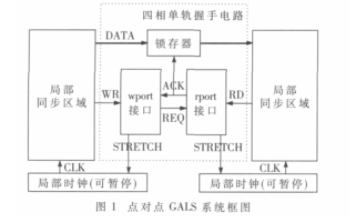

7关于FPGA的全局异步局部同步四相单轨握手协议实现

在常规FPGA中设计了基于LUT的异步状态保持单元,实现了全局异步局部同步系统的接口电路、时钟暂停电路,进一步完

2021-05-26 18:12:38 3436

3436

3436

3436

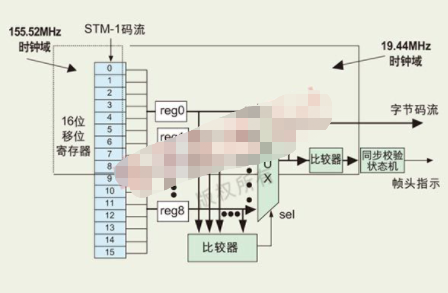

基于EP1C6T144C8 FPGA实现STM-1同步系统的应用方案

,首先要从同步数据流中提取帧同步信息,帧同步提取性能的优劣直接影响整个数据的处理质量与整个系统的性能。使用FPGA技术可以实现同步系统的模块化、小型化和芯片化,得到稳定可靠的帧同步器。

2021-06-23 15:44:00 2451

2451

2451

2451

ARM+FPGA的高速同步数据采集

着较高的要求,并且大多情况下要求多参数同步测量。飞旭公司在基于实际的工程项目成功的基础上,推出了基于ARM+FPGA的低功耗、高速率、高精度、多通道同步数据采集方案,可以通过监测者的要求完成多通道数据的同步采集并实现实时的网络传输。

2023-02-10 17:50:01 1091

1091

1091

1091fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试?

fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试? 在FPGA与DSP通讯时,同步时钟频率非常重要,因为不同的设备有不同的时钟频率,如果两者的时钟频率不同步,会导致通讯数据的错误

2023-10-18 15:28:13 1060

1060

1060

1060 电子发烧友App

电子发烧友App

评论