在UVM验证环境的项目中,经常需要使用内置的print()函数或sprint()函数打印

2023-12-20 10:14:35 951

951

ASIC1810 - ASIC1810 - List of Unclassifed Manufacturers

2022-11-04 17:22:44

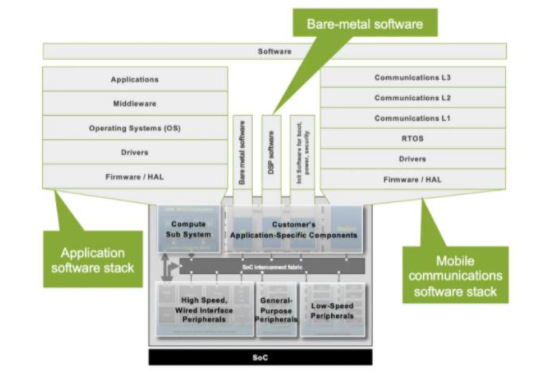

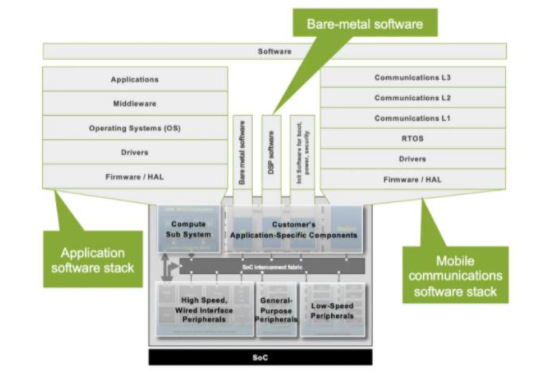

原型验证---用软件的方法来发现硬件的问题 在芯片tap-out之前,通常都会计算一下风险,例如存在一些的严重错误可能性。通常要某个人签字来确认是否去生产。这是一个艰难的决定。ASIC的产品NRE

2019-07-11 08:19:24

1ASIC 验证技术.................................................11.1 ASIC 设计流程

2015-09-18 15:26:25

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

1. 问题 假如用以下两种方式启动sequence,方法1用sequence的start()方法启动seq1,方法2用UVM的default_sequence机制启动seq2。那么seq1

2023-04-04 17:15:07

验证方法简介 设计验证是用于证明设计正确性的过程,要求和规格。 在数字设计流程中,验证可确保芯片按照设计意图正确运行,然后再将设计送去制造。 具体来说,验证方法是验证集成电路设计的标准化方法。 验证

2022-02-13 17:03:49

FPGA原型验证已是当前原型验证的主流且成熟的芯片验证方法——它通过将RTL移植到现场可编程门阵列(FPGA)来验证ASIC的功能,并在芯片的基本功能验证通过后就可以开始驱动的开发,一直到芯片

2020-08-21 05:00:12

有流水处理和响应迅速的特点。 芯片解密认为,FPGA一般来说比ASIC的速度要慢,无法完成复杂的设计,但是功耗较低。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价

2017-06-12 15:56:59

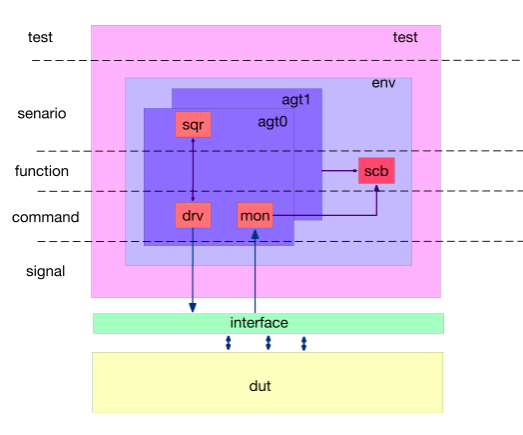

model)。一个简单的验证平台框图:在UVM中,引入了agent和sequence的概念,因此UVM中验证平台的典型框图长这样:通知:本章更新后在更新一篇《IC验证之UVM常用宏汇总(四)》将不

2020-12-02 15:21:34

加入factory机制 上一节《IC验证"一个简单的UVM验证平台"是如何搭建的(五)》给出了一个只有driver、使用UVM搭建的验证平台。严格来说这根本就不算是UVM验证

2020-12-08 12:07:21

本帖最后由 IC那些事儿 于 2020-12-4 15:50 编辑

上次更新完《IC验证"UVM验证平台"组成》后本打算不再更新......但有人反映要继续更新...继续

2020-12-04 15:48:19

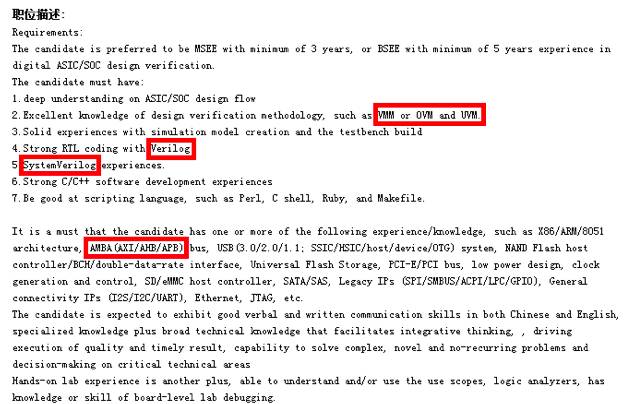

Synopsys在VMM中的寄存器解决方案RAL。同时,UVM还吸收了VMM中的 一些优秀的实现方式。可以说,UVM继承了VMM和OVM的优点,克服了各自的缺点,代表了验证方法学的发展方向。学了UVM之后能做

2020-12-01 15:09:14

: +define+MACRO 或者: +define+MACRO=100扩展寄存器模型中的数据位宽:`define UVM_REG_DATA_WIDTH 128扩展寄存器模型中的地址位宽:`define

2020-12-02 15:24:35

在上一节中,**《IC验证"UVM验证平台加入factory机制"(六)》**虽然输出了“main_phase is called”,但是“data is drived”并没有

2020-12-09 18:28:15

第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-11-01 06:28:47

设计验证方法 MyHDL - 基于 Python 的硬件描述语言,也具有验证功能 PyUVM – 使用 cocotb 的 UVM 的 Python 实现 UVM Python –UVM的 Python

2022-11-03 13:07:24

,本科5年数字芯片验证工程师岗位要求:1、熟悉systemverilog 语言,熟练掌握UVM/VMM/OVM验证方法学,独立完成过中等规模以上模块的验证开发2、熟悉数字芯片验证流程,三年以上相关工作经验3、硕士3年,本科5年联系方式:ucollide@163.com一八五八3907八零五

2018-03-13 09:27:17

【招聘】射频/模拟、ASIC设计/验证、系统、模拟设计等 射频集成电路工程师(TRX 方向)-BJ 射频/模拟集成电路工程师(RF/Analog IC Engineer)-BJ 射频IC工程师

2017-03-03 14:54:37

UVM Report机制概述

2020-12-21 06:55:05

uvm_reg_field是什么

2020-12-17 06:10:56

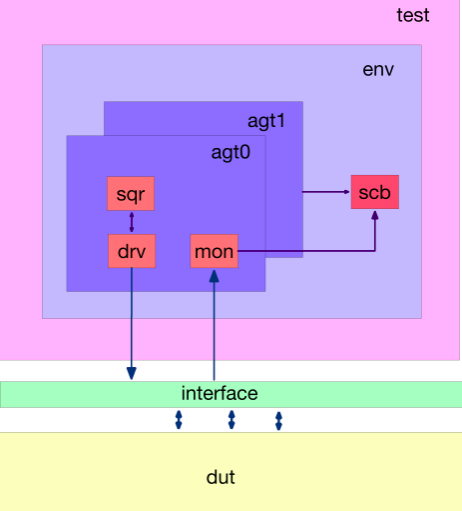

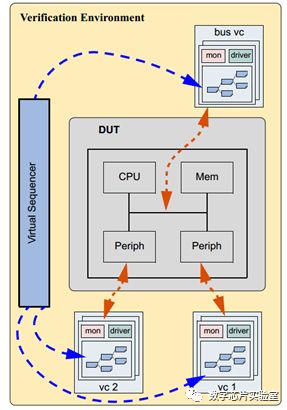

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们一个

2022-02-14 06:46:33

招聘岗位:芯片设计数字,验证工程师岗位要求:1.本科及以上学历,2年半以上工作经验2.精通verilog,SV等语言3.有端到端项目的交付经验4.精通VMM/UVM验证方法学5.具备团队合作意识,责任心强联系方式:***简历投递邮箱:lzdnewmail@163.com

2017-10-09 19:47:57

厦门asic岗位招聘。应届和社招均欢迎,本科硕士均欢迎。做手机芯片的,国内没几家,一搜就知道名字了。简历请发邮箱 shuli198349@163.com

2015-06-12 12:07:37

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-15 07:38:34

请教各位大佬,UVM是基于sv的验证方法学,如果采用systemc语言编程,如何实现?

2019-11-07 15:30:16

),通常也叫寄存器模型,顾名思义就是对寄存器这个部件的建模。本文要介绍的内容,包括对UVM寄存器模型的概述,如何构建寄存器模型,以及如何将寄存器模型集成到验证环境中。篇幅原因,将在下一篇文章再给出寄存器

2022-09-23 14:29:03

讲述两个内容,芯片验证以及验证计划。首先来看看芯片验证在芯片设计当中的地位。芯片验证是在一个芯片设计的过程当中,验证各个转化阶段是否正确的执行的过程,一个芯片的设计涉及到多个阶段的转化。首先,分析市场需求

2021-01-21 15:59:03

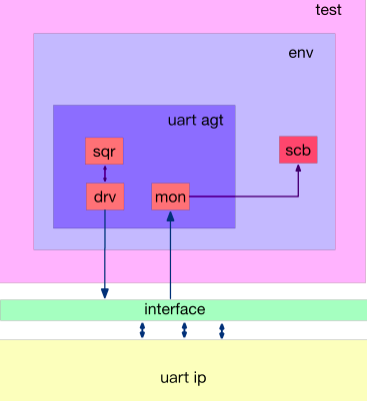

原文链接:https://zhuanlan.zhihu.com/p/345775995大家好,我是一哥,上章内容主要讲述两个内容,芯片验证以及验证计划。那本章我们主要讲述的内容有介绍什么是uvm

2021-01-21 16:00:16

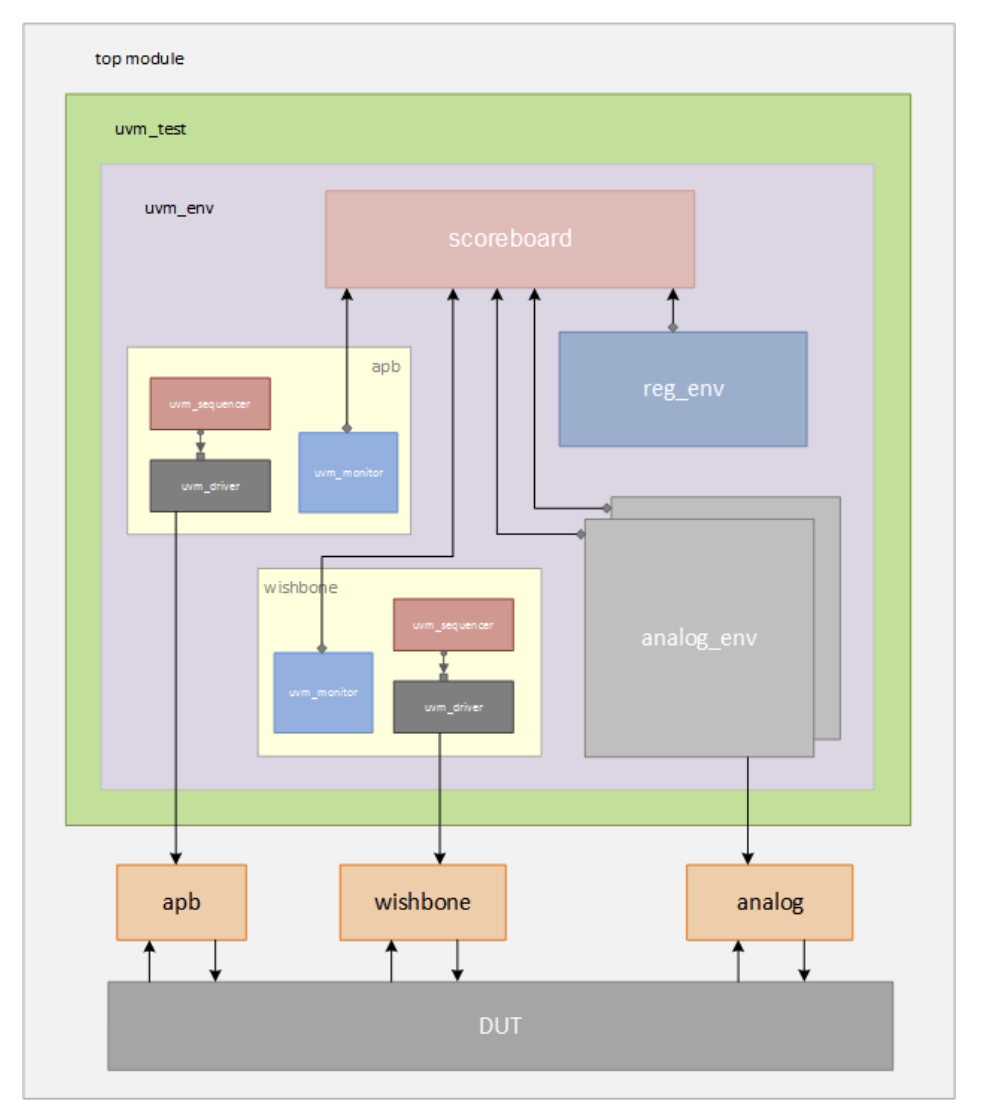

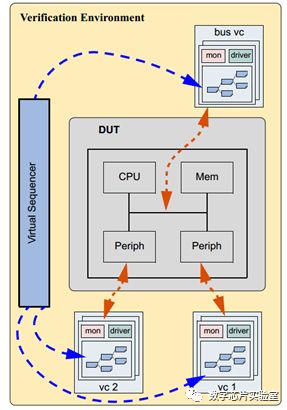

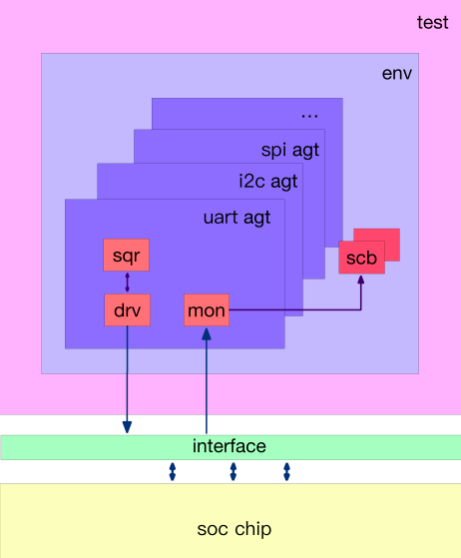

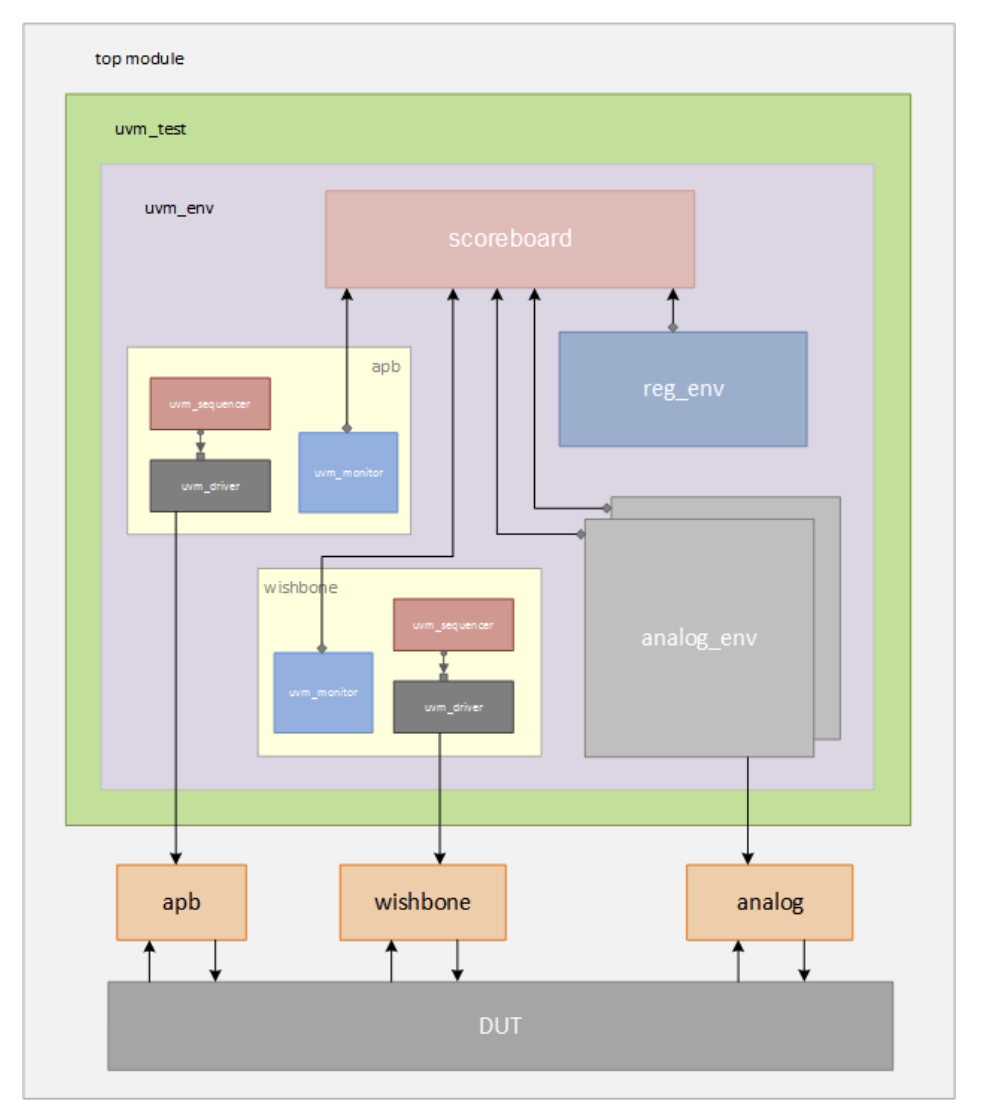

应用的过程中,将uvm的组件封装起来,可以将这些封装的组件呢作为一个整体进行重用,在进行芯片级或者是系统级验证的时候,往往会出现多个模块的验证。 此时,测试平台的结构会发生变化,图中的测试平台实现了

2021-01-22 15:32:04

的transaction,以及创建用于产生事物的事物发生器sequence。 在uvm验证平台中穿梭各个组件之间的基本信息单元是一个被称为transaction的数据对象,也就是我们前面所说的事物

2021-01-26 10:05:37

大家好,我是一哥,上章一个典型的uvm验证平台应该是什么样子的?从本章开始就正式进入uvm知识的学习。先一步一步搭建一个简单的可运行的测试平台。 本章首先来介绍一下构成uvm测试平台的主要组件

2021-01-22 15:33:26

新手学习SystemVerilog & UVM指南 从刚接触System Verilog以及后来的VMM,OVM,UVM已经有很多年了,随着电子工业的逐步发展,国内对验证人才的需求也会急剧

2015-03-11 16:24:35

`深圳单片机开发方案公司,专注电子产片领域单片机方案开发,提供优质的音频转接头单片机方案ASIC芯片。电子产品开发之苹果手机7/8/X小药丸音频转接头二合一单片机方案ASIC芯片完美实现苹果手机边

2018-10-23 14:49:24

形式验证方法论基于断言的验证进行“验证”的其他方法通用验证方法 (UVM) – Accellera/Cadence嵌入式UVMUVM测试开源 VHDL 验证方法 (OSVVM)UVVM:通用 VHDL

2022-11-26 20:43:20

猎头职位:IC验证工程师【北京】岗位职责:1.根据芯片架构文档和设计要点,制定验证方案,拟定验证计划;2.根据验证方案和计划,实施验证,包括编写参考模型、搭建仿真验证平台与迭代改进、编写完备的验证

2017-02-15 13:39:33

。往往我们在书写测试用例或者sequences的时候会有查询验证平台组件uvm_component的需求,比如env/driver/monitor。由于sequences不是测试平台层次结构的一部分,实现

2022-04-11 16:43:42

uvm_info宏的定义如下: `define uvm_info(ID,MSG,VERBOSITY) \ begin \ if (uvm_report_enabled(VERBOSITY

2023-03-17 16:41:28

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

ASIC 芯片全定制费用高、风险大、周期长,因此在全定制之前一般先用FPGA 或CPLD 等可编程逻辑器件做功能验证。但在一些空间极为有限、成本极低的应用场合,采用FPGA 或者CPLD 显然

2009-09-25 16:00:32 12

12 全球电子设计创新领先企业Cadence设计系统公司,今天宣布了业界最全面的用于系统级芯片(SoC)验证的通用验证方法学(UVM)开源参考流程。为了配合Cadence EDA360中SoC实现能力的策略,

2010-06-28 08:29:14 2240

2240 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。由于FPGA与ASIC在结构、性能上各不相同,ASIC是基于标准单元库,FPGA用的

2010-09-10 17:22:26 989

989 对ASIC设计进行FPGA原型验证时,由于物理结构不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。 现代集成电路设计中,芯片的规模和复杂度正呈指数增加。尤其在ASIC设计流程中

2011-03-25 15:16:20 108

108 本文描述ASIC验证方法和过程,有助于ASIC设计者对验证的认识。模拟是验证ASIC并产生测试矢量的唯一途径,设计者可以对ASIC芯片或者在ASIC应用系统中进行功能和时序模拟。

2012-05-24 09:32:47 23

23 本文描述ASIC验证方法和过程,有助于ASIC设计者对验证的认识。模拟是验证ASIC并产生测试矢量的唯一途径,设计者可以对ASIC芯片或者在ASIC应用系统中进行功能和时序模拟。

2012-05-24 09:32:47 27

27 俄勒冈州威尔逊维尔,2016 年 3 月 2 日– Mentor Graphics 公司(纳斯达克代码:MENT)今日宣布,推出首个完全原生的 UVM SystemVerilog 内存验证 IP 库,该内存验证 IP 库可用于所有常用内存设备、配置和接口。

2016-03-02 14:03:49 1027

1027 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 基于UVM的CAN模块自验证方法_熊涛

2017-01-08 14:47:53 3

3 一种基于UVM的混合信号验证环境_耿睿

2017-01-07 21:39:44 1

1 四轴电机伺服控制ASIC芯片_刘亚静

2017-01-07 15:17:12 4

4 UVM使得验证测试平台的结构得以标准化,各种复用策略及标准对于提高验证质量、缩短项目周期都非常有效。垂直重用是常见的复用策略之一,即同一项目测试平台复用于不同验证层次。验证中常将最底层的IP级验证平台向更高的集成层复用,而UVM寄存器模型则是验证平台复用的一个关键部分。

2017-09-15 11:49:08 15

15 的连接、驱动器、监视器、仿真序列以及功能覆盖率的建立。 本文呈现出了一种使用UVM验证方法学构建基于高可配置性的高级微处理器总线架构(AMBA)的IP验证环境,其中会使用到Synopsys公司的AMBA VIP和Ruby脚本。该验证环境可以支持通过使用AMBA设计参数进行自

2017-09-15 14:37:34 6

6 UVM已经成为了一种高效率的、从模块级到系统级完整验证环境开发标准,其中一个关键的原则是UVM可以开发出可重用的验证组件。获得重用动力的一个方面表现为标准的仿真器和硬件加速之间的验证组件和环境的复用

2017-09-15 17:08:11 14

14 毋庸置疑,UVM大大提高了我们开发验证平台的效率。但同时,熟练掌握UVM搭建验证平台也并不是一件容易的事情。同时由于不同验证工程师搭建环境的风格不太一致,所以在一个项目中常会出现不好管理,甚至前后

2017-09-15 17:18:01 22

22 联发科从6年就开始布局研发ASIC芯片,现在联发科基于16nm制程的ASIC芯片已经占据智能音箱市场超8成市占率。为了进一步扩充 ASIC产品阵线,联发科推出了业界第一个通过 7nm FinFET 硅验证(Silicon-Proven)的 56G PAM4 SerDes IP。

2018-04-25 21:23:12 34711

34711 近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下千万门级、甚至上亿门级的逻辑设计。现今,将整个验证设计分割到多个采用最新工艺大容量FPGA中,FPGA通过高速总线互联,成为大规模ASIC或SOC原型验证的极佳选择。

2018-07-02 08:20:00 1695

1695 采用fpga原型技术验证asic设计,首先需要把asic设计转化为fpga设计。但asic是基于标准单元库,fpga则是基于查找表,asic和fpga物理结构上的不同,决定了asic代码需要一定

2019-07-23 08:07:00 1923

1923

等级的度量:基于通用验证方法(UVM)的形式验证和随机约束测试增加了发现错误的可能性。有时我们为RTL验证创建一个完美有效的测试,但发现它不能在门级仿真期间重复使用,因为UVM监视器挂在内部SoC信号上,这些信号在实现阶段后可能会消失或改变。

2019-08-09 15:25:34 6862

6862

读者思考UVM为什么要引入这些机制,从而使读者知其然,更知其所以然。本书以一个完整的示例开篇,使得读者一开始就对如何使用UVM搭建验证平台有总体的概念。针对没有面向对象编程基础的用户,本书在附录中简要介绍了面向对象的概念及SystemVerilog中区别于其他编程语言的一些特殊语法。

2019-11-29 08:00:00 28

28 近几十年来,集成电路事业发展迅速,设计与工艺技术不断发展,更多和更复杂的功能被集成到一块芯片上。SoC的集成度和复杂度大大提高,在IC设计中就容易引入错误,所以验证工作将变得艰巨。随着IC设计规模

2020-01-27 17:21:00 6132

6132

Wilson Research Group 的一项最近研究发现,48% 的 FPGA 设计项目和 71% 的 ASIC设计项目依赖 UVM 进行设计验证。

2020-03-02 18:12:24 1019

1019 MathWorks宣布,HDLVerifier从现已上市的Release2019b开始提供对UniversalVerificationMethodology(UVM)的支持。

2020-03-07 14:29:17 815

815 本章第一节将大体介绍一下感性意义上的UVM,这里不会讲的很详细,因为关于UVM的历史在网上已经有太多的资料第二节讲述验证平台的组成,这里也只是介绍一个轮廓。第三节开始则会教我们一步一步搭建一个UVM

2020-07-01 08:00:00 69

69 根据威尔逊研究集团和西门子EDA的数据,即使在EDA工具的研发上花费了数十亿美元,在验证人工上又花费了数百亿美元,但只有30%到50%的ASIC设计是第一次正确的。 即便如此,这些设计仍然有bug

2021-02-27 11:01:44 1436

1436

本文是本人对xilinx XC7V系列FPGA用于ASIC前端验证遇到问题的总结,为自己记录并分享给大家,如果有歧义或错误请大家在评论里指出。

2021-01-12 17:31:44 9

9 尽管本指南提供了一组说明,以执行一个或多个特定的验证任务,但应 以教育,经验和专业判断为补充。 并非本指南的所有方面都可能 适用于所有情况。 《 UVM 1.1用户指南》不一定代表标准 必须谨慎判断给定的专业服务是否足够,也不应以此文件为依据 应用时无需考虑项目的独特方面。

2021-03-29 10:41:32 21

21 ASIC芯片设计开发流程说明。

2021-04-07 09:18:59 64

64 第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-10-25 12:36:01 22

22 大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们

2021-12-09 13:36:13 7

7 需要门级验证:FPGA 和 ASIC 一样需要设计级验证。但是,FPGA 在门级不是细粒度的,因此它们不需要门级验证。您将每个门都放置在 ASIC 设计中,因此您需要验证每个门。

2022-06-20 16:13:05 2184

2184

ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)今日发布FPGA-Go-ASIC验证平台。

2022-07-29 10:08:16 784

784 利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 5

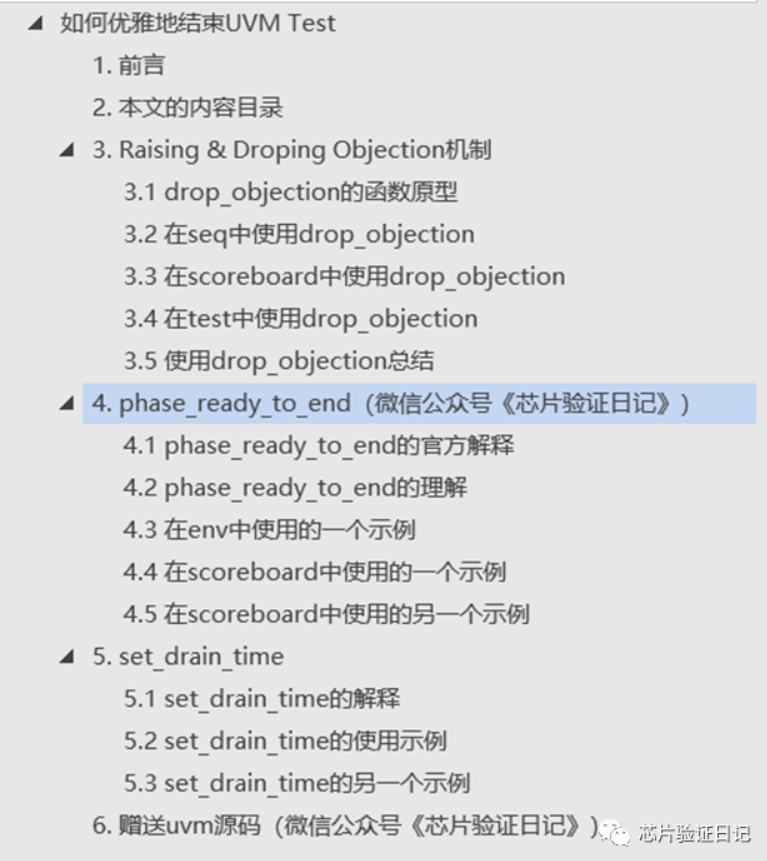

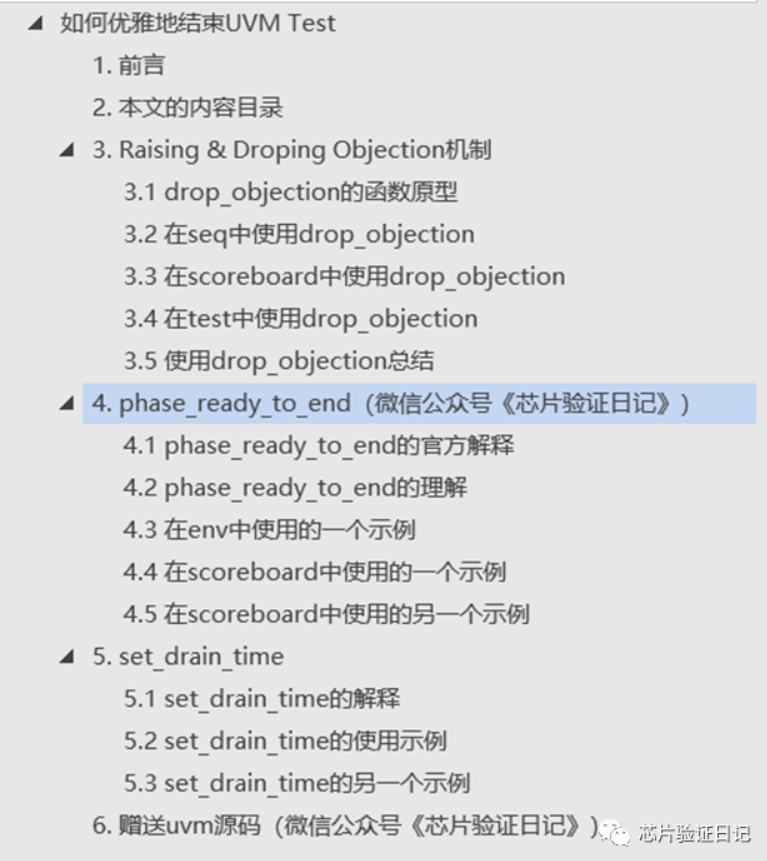

5 分享一下在UVM验证环境中,结束仿真的几种方式,不同结束仿真的方式适合不同的应用场景。

2022-12-17 11:23:54 1702

1702

因为DUT是一个静态的内容,所以testbench理应也是静态的,其作为uvm验证环境和DUT的全局根结点。

2023-03-21 11:33:02 982

982 UVM environment**包含多个可重用的验证组件,并根据test case的需求进行相应的配置。例如,UVM environment可能具有多个agent(对应不同的interface)、scoreboard、functional coverage collector和一些checker

2023-03-21 11:35:25 744

744

基于UVM搭建验证环境和构造验证激励,调试的工作总是绕不开的。实际上,对验证环境和激励的调试,往往伴随着验证阶段的前半程,并且会花掉验证工程师很多时间和精力。

2023-04-06 09:36:03 428

428 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 以前看到不少验证技术书籍都在说验证环境中随机怎么怎么好,然后为了随机,UVM,SV 提供了什么什么支持。

2023-04-10 11:21:03 375

375 话说螺蛳壳里做道场,UVM推出这么多年以来每年DVCon会议上总还是有人分享他们基于UVM package做的一些改动,使其能够更适合项目的要求。

2023-04-13 18:13:09 1207

1207 在UVM中,transaction 是一个类对象,它包含了建模两个验证组件之间的通信所需的任何信息。

2023-05-24 09:17:32 1165

1165

driver应该派生自uvm_driver,而uvm_driver派生自uvm_component。

2023-05-26 14:38:46 824

824

如下图所示,UVM中的TLM接口为组件之间Transaction的发送和接收提供了一套统一的通信方法。

2023-05-29 09:31:44 340

340

本文使用Easier UVM Code Generator生成包含多个agent和interface的uvm验证环境。

2023-06-06 09:13:02 584

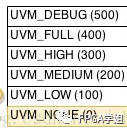

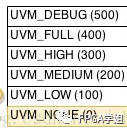

584 UVM预先定义了六个详细程度; UVM_NONE到UVM_DEBUG。这些级别只不过是整数枚举值

2023-06-06 12:33:26 2653

2653

uvm_do宏及其变体提供了创建、随机化和发送transaction items或者sequence的方法。

2023-06-09 09:36:49 2588

2588

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。

2023-06-20 17:28:01 724

724 UVM提供了实现 **覆盖驱动验证(coverage-driven verification ,CDV)** 的框架。 CDV结合了自动测试向量生成,自检查和覆盖率收集,显著地缩短了用于验证设计时间。

2023-06-25 11:38:58 861

861

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。

2023-06-29 16:57:01 579

579 本篇是对UVM设计模式 ( 二 ) 参数化类、静态变量/方法/类、单例模式、UVM_ROOT、工厂模式、UVM_FACTORY[1]中单例模式的补充,分析静态类的使用,UVM中资源池的实现,uvm_config_db的使用。

2023-08-06 10:38:41 825

825

FPGA验证和UVM验证在芯片设计和验证过程中都扮演着重要的角色,但它们之间存在明显的区别。

2024-03-15 15:00:41 94

94

电子发烧友App

电子发烧友App

评论