本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 15422

15422

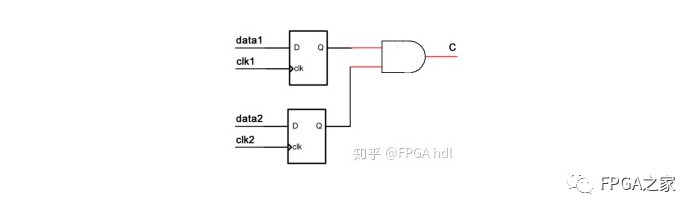

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 53525

53525

了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,

2020-12-25 14:39:28 4147

4147

数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-01-13 13:57:47 1830

1830

数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 476

476 芯片设计是现代电子设备的重要组成部分,其中组合逻辑和时序逻辑是芯片设计中非常重要的概念。组合逻辑和时序逻辑的设计对于构建复杂的电路系统至关重要。

2023-08-30 09:32:15 809

809 FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

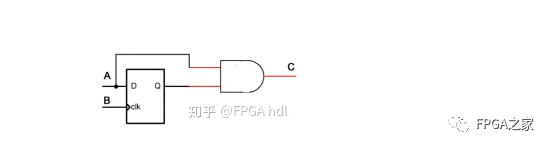

的神通广大。图3.15 D触发器模型符号数字电路按照逻辑功能一般可以分为组合逻辑和时序逻辑。组合逻辑不含有任何用于存储比特信号的电路,它的输出只和当前电路的输入有关,如前面(图3.12)所列举的加法器的电路

2015-01-22 21:46:14

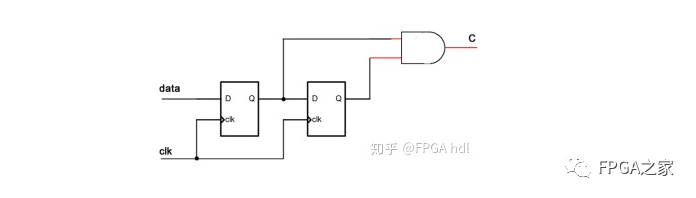

寄存器的代码编写。接下来我们要更进一步从深沉次来探讨基于寄存器的同步以及时钟的设计原则。(特权同学,版权所有)虽然在上一章已经对组合逻辑和时序逻辑的基本概念做过描述,但是这里还是要再额外唠叨几句组合逻辑

2015-06-29 09:31:03

消除组合逻辑的毛刺本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 在章节3.2的最后部分对于组合逻辑和时序

2015-07-08 10:38:02

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

时序逻辑电路设计6.1 基本D触发器的设计6.2 JK触发器6.3 带异步复位/置位端的使能T触发器6.4 基本计数器的设计6.5 同步清零的计数器6.6 同步清零的可逆计数器6.7 同步预置数的计数器

2009-03-20 10:04:53

你了解如何分析组合逻辑电路与时序逻辑电路吗?数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。逻辑电路的特点组合逻辑电路在

2021-11-18 06:30:00

约束,我观察到的信号是内部信号(由周期约束覆盖)。我的理解是,无论使用多少组合逻辑,只要时序报告中没有错误,建立/保持就可以满足要求。为什么我没有错误报告和错误结果(时间问题)?以上来自于谷歌翻译以下

2019-05-15 06:42:16

;nbsp; 在数字电路中,数字电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路:任何时刻的输出取决于这一

2009-09-16 16:05:29

组合逻辑电路实验实验三 组合逻辑电路一、 实验目的1、 掌握组合逻辑电路的功能测试2、 验证半加器和全加器的逻辑功能3、 学会

2009-03-20 18:11:09

逻辑电路中,输出始终取决于其输入的组合。因此,组合电路是无记忆的。 因此,如果其输入条件之一从0-1或1-0改变状态,则默认情况下,组合逻辑电路的结果输出也将在其设计中具有“无内存”,“时序”或“反馈回路

2020-12-31 17:01:17

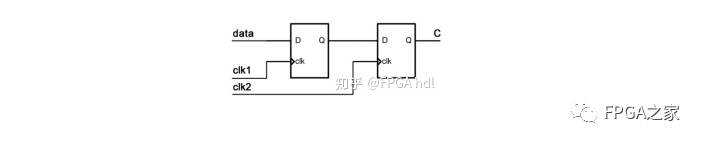

时序逻辑电路中,输人和内部状态的变化由时钟信号控制同步进行,而异步时序逻辑电路则不需要时钟信号。由于FPGA电路设计一般使用同步时序逻辑电路,所以这里我们不对异步时序逻辑电路进行过多讨论,而我们常用

2020-12-23 17:25:49

偏硬件:接口电路中的门组合电路;偏软件:算法、接口控制器实现中的状态机群或时序电路。随着逻辑设计的深入,复杂功能设计一般基于同步时序电路方式。此时,逻辑设计基本上就是在设计状态机群或计数器等时序

2021-11-10 06:39:25

逻辑门及组合逻辑电路实验实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法。4.

2008-09-25 17:28:34

根据逻辑电路的不同特点,数字电路分为组合逻辑和时序逻辑,明德扬粉丝里的同学提出,无法正确区分,今天让我跟一起来学习一下两种逻辑的区别以及使用环境。·时序逻辑和组合逻辑的区别关于组合逻辑和时序逻辑

2020-03-01 19:50:27

)来实现组合逻辑,每个查找表连接到一 个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用 金属连线互相连接或

2019-08-11 04:30:00

时序逻辑电路应用很广泛,根据所要求的逻辑功能不同进行划分,它的种类也比较繁多。在具体的授课环节中,主要选取了应用较广、具有典型时序逻辑电路特征的三种逻辑器件进行比较详细地介绍 。1.计数器一般来说

2016-10-25 23:03:31

。可分为同步时序逻辑电路和异步时序逻辑电路 (FPGA一般使用的同步时序逻辑电路)。 本人对异步和同步的理解也就是有无时钟信号的控制,像异步没有时钟线的我们学过的串口、单总线协议等;同步的有时钟线的有

2019-12-10 20:32:03

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

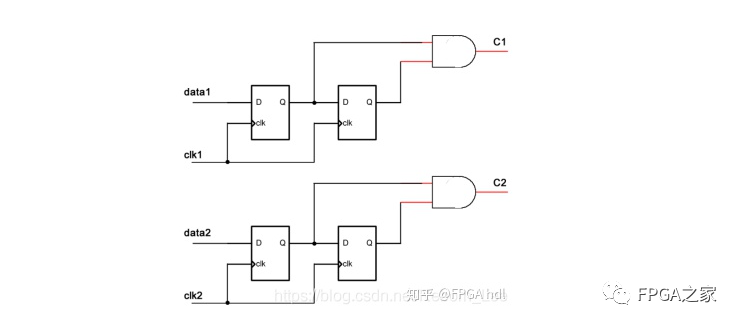

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?时序设计的实质是什么?

2021-09-29 07:33:38

什么是同步逻辑和异步逻辑,同步电路和异步电路的区别是什么?

2021-06-18 08:52:44

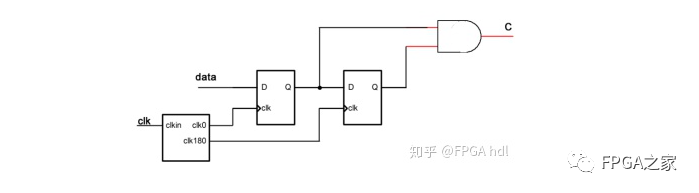

本文来自芯社区,谢谢。1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统

2021-07-26 08:26:57

转自知乎答主ictown_数字IC设计工程师笔试面试经典100题-有答案-陈恩1:什么是同步逻辑和异步逻辑?(汉王)同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。同步

2021-11-11 06:13:35

什么是时序逻辑?时序逻辑由哪几部分构成?

2021-09-17 07:43:37

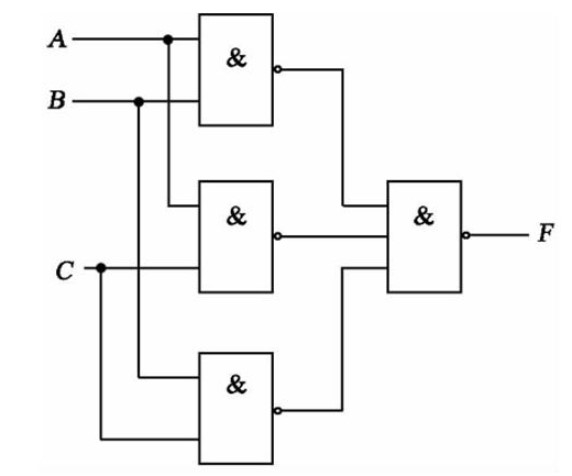

走近FPGA。数字逻辑电路分为组合逻辑电路和时序逻辑电路,组合逻辑电路的输出仅取决于当前的输入,其逻辑功能的实现不需要时钟的参与,因此弄清楚组合逻辑电路的输入输出关系尤为重要。这次的文章将通过几个基础的实例介绍

2022-07-21 15:38:45

```勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 数字电路按照逻辑

2017-11-17 18:47:44

基本时序逻辑电路9. 建立时间和保持时间10. 同步时序电路11. 组合逻辑和时序逻辑判断13. 基本总线的理解14.加法器15.FPGA开发工具1. 进制转换1、十进制46.25对应的二进制表达式为( )。A 101110.11...

2021-07-26 07:14:31

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

涉及时序逻辑电路的实例,希望能够帮助大家理解在FPGA中实现时序逻辑电路。与组合逻辑电路相比,时序逻辑电路需要时钟的参与,电路中会有存储器件的参与,时序逻辑电路的输出不仅取决于这一时刻的输入,也受此

2022-07-22 15:25:03

Verilog程序模块的结构是由哪些部分组成的?如何去实现时序逻辑电路和组合逻辑电路的设计呢?

2021-11-03 06:35:57

0-1或1-0改变状态,则默认情况下,组合逻辑电路的结果输出也将在其设计中具有“无内存”,“时序”或“反馈环路”。组合逻辑组合逻辑电路由“组合”或连接在一起以产生更复杂的开关电路的基本逻辑“与非”门

2021-01-19 09:29:30

组合逻辑电路的基本模块是什么?时序逻辑电路怎样进行工作的?

2021-09-18 09:19:42

集成逻辑电路、组合逻辑电路实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法

2008-12-11 23:36:32

组合逻辑电路(简称组合电路)任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关时序逻辑电路(简称时序电路)任意时刻的输出信号不仅取决

2009-07-15 18:45:58 0

0 组合逻辑电路电子教案:数字逻辑电路可分为两大类: 一类叫组合逻辑电路;另一类叫时序逻辑电路。本章首先介绍组合逻辑电路的共同特点和描述方法,然后重点介绍组合逻辑电

2009-09-01 08:58:29 0

0 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 中规模集成时序逻辑设计:计数器:在数字逻辑系统中,使用最多的时序电路要算计数器了。它是一种对输入脉冲信号进行计数的时序逻辑部件。9.1.1 计数器的分类1.按数制

2009-09-01 09:09:09 13

13 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实

2010-08-18 14:50:44 0

0 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 基本组合逻辑电路

一、 实验目的?⒈ 掌握一般组合逻辑电路的分析和设计方法。?⒉ 熟悉集成优先编码器的逻辑功能及简单应用。

2008-09-24 22:14:03 2504

2504 实验十六 时序逻辑电路? 实验(1) 计数器?一、实验目的?⒈ 熟悉计数器的设计方法及工作原理。?⒉ 了解同步计数器与异步计数器的区别。?⒊ 应用

2008-09-24 22:17:08 3210

3210

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 3438

3438

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 8146

8146

详细介绍了组合逻辑电路的分析方法,包括加法器、译码器、编码器、分配器、选择器等组合逻辑电路的分析方法

2017-01-22 13:13:01 3

3 一种设计同步时序逻辑电路的新方法

2017-02-07 15:05:00 29

29 逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。

2017-05-22 15:15:59 70760

70760

由于同步动态随机存储器SDRAM内部结构原因导致其控制逻辑比较复杂。现场可编程逻辑门阵列FPGA作为一种半定制电路具有速度快、内部资源丰富、可重构等优点。本文设计了一种基于FPGA的SDRAM

2017-11-18 12:42:03 2054

2054

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 8630

8630 异步电路:主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,但它同时也用在时序电路中,此时它没有统一的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态

2017-11-30 09:35:40 30869

30869

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

2018-01-30 16:24:25 38002

38002

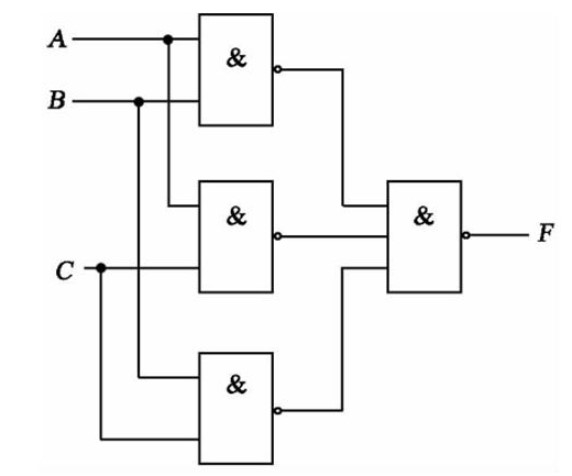

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。单一的与门、或门、与非门、或非门、非门等逻辑门不足以完成复杂的数字系统设计要求。组合逻辑电路是采用两个或两个以上基本逻辑门来实现更实用、复杂的逻辑功能。

2018-01-30 17:05:44 62959

62959

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 91327

91327

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 123040

123040

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 106881

106881

模块的模板包括了输入输出信号列表、信号定义,组合逻辑和时序逻辑等,这是一个模块常用的组件。学员只需要理解各个部分的意义,按要求来填空就可以,完全没有必要去记住。我看很多学员刚开始学习时,花费大量的时间去记住、背熟模块,这是没有意义的。

2018-04-20 15:40:00 1643

1643

根据逻辑功能的不同,可把数字电路分为组合逻辑电路(Combinational Logic Circuit)和 时序逻辑电路(Sequential Logic Circuit)两大类。

2018-07-20 08:00:00 0

0 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 30485

30485 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 49628

49628 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 62616

62616 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 7636

7636

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:04:00 2191

2191

组合逻辑电路是无记忆数字逻辑电路,其任何时刻的输出仅取决于其输入的组合.

2019-06-22 10:53:20 46654

46654

本文档的主要内容详细介绍的是组合逻辑电路和时序逻辑电路的学习课件免费下载包括了:任务一 组合逻辑电路,任务二 编码器,任务三 译码器,任务四 集成触发器,任务五 寄存器,任务六 计数器。

2020-10-27 15:58:24 31

31 组合逻辑电路是指在任何时刻,输出状态只决定于同一时刻各组合逻辑电路输入状态的组合,而与电路以前状态无关而与其他时间的状态无关。如:加法器、编码器、译码器、选择器等

2020-12-09 14:49:02 12

12 同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。

2021-01-04 10:53:37 14215

14215 所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,求出电路的逻辑功能。

2022-08-12 17:19:26 11080

11080

组合逻辑电路的特点是输入的变化直接反映了输出的变化,其输出的状态仅取决于输入的当前状态,与输入、输出的原始状态无关。如果从电路结构上来讲,组合逻辑电路是没有触发器组件的电路。

2022-10-24 16:02:32 965

965 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2022-12-21 09:18:32 606

606 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-02-12 10:28:36 771

771 使用always_ff和在灵敏度列表中指定一个时钟边沿并不意味着过程中的所有逻辑都是时序逻辑。综合编译器将推断出每个被非阻塞赋值的变量的触发器。阻塞赋值也可能推断出触发器,这取决于赋值语句相对于程序中其他赋值和操作的顺序和上下文。

2023-02-20 10:38:06 442

442 所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,求出电路的逻辑功能。

2023-03-06 14:37:26 1843

1843 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 4816

4816

时序逻辑的代码一般有两种: 同步复位的时序逻辑和异步复位的时序逻辑。在同步复位的时序逻辑中复位不是立即有效,而在时钟上升沿时复位才有效。 其代码结构如下:

2023-03-21 10:47:07 400

400 时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 1882

1882

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 1983

1983

电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0 时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 2539

2539

今天让我跟一起来学习一下两种逻辑的区别以及使用环境。

2023-07-07 14:15:12 1968

1968

在一个统一的时钟信号的驱动下进行操作,而异步逻辑是指电路中的各个组件根据输入信号的条件自主进行操作,不受统一的时钟信号控制。 同步逻辑和异步逻辑的区别主要体现在以下几个方面: 1. 时序性:同步逻辑是按照固定的时钟信号进

2023-11-17 14:16:03 1007

1007 当逻辑电路由多个逻辑门组成且不含存储电路,对于给定的输入变量组合将产生确定的输出,则这种逻辑电路称为组合逻辑电路。

2024-02-04 11:46:36 320

320

组合逻辑电路和时序逻辑电路是数字电路中两种重要的逻辑电路类型,它们主要区别在于其输出信号的依赖关系和对时间的敏感性。

2024-02-04 16:00:27 449

449 时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 499

499

电子发烧友App

电子发烧友App

评论