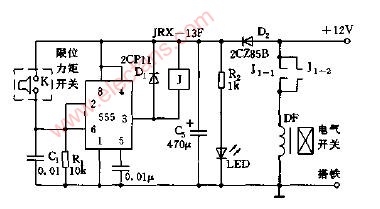

误踩汽车油门控制器电路图

2009-05-26 15:26:48 1635

1635

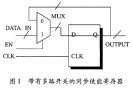

门控管(IGBT)是由场效应管作为推动管。

大功率管作为输出管的有机组合。应用于电磁灶等的大电流、高电平电器中

2010-10-13 12:02:38 4188

4188 门控及逻辑控制电路

2010-11-06 12:00:48 5291

5291

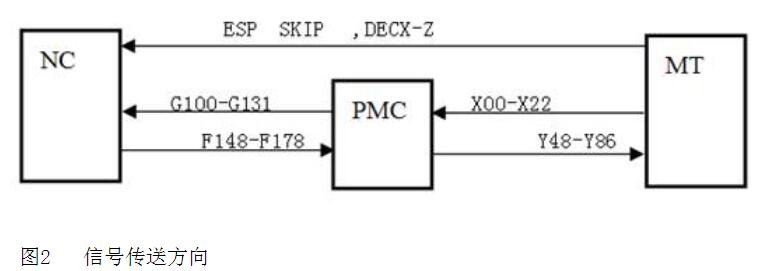

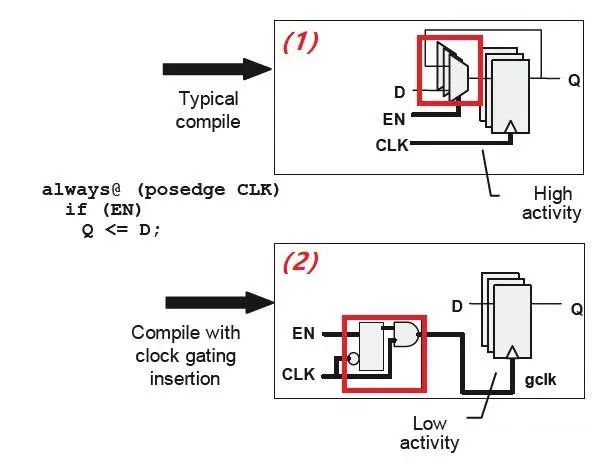

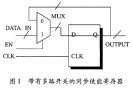

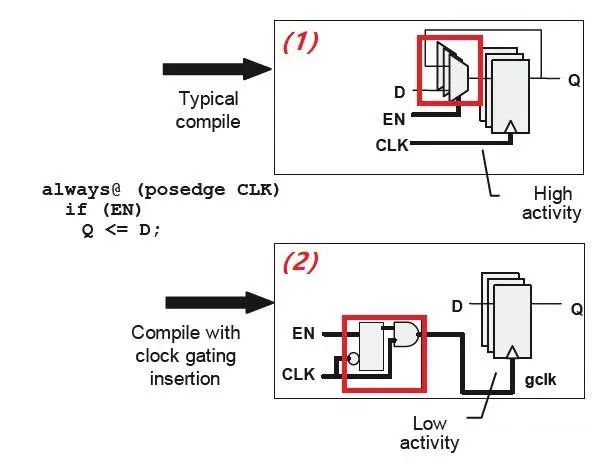

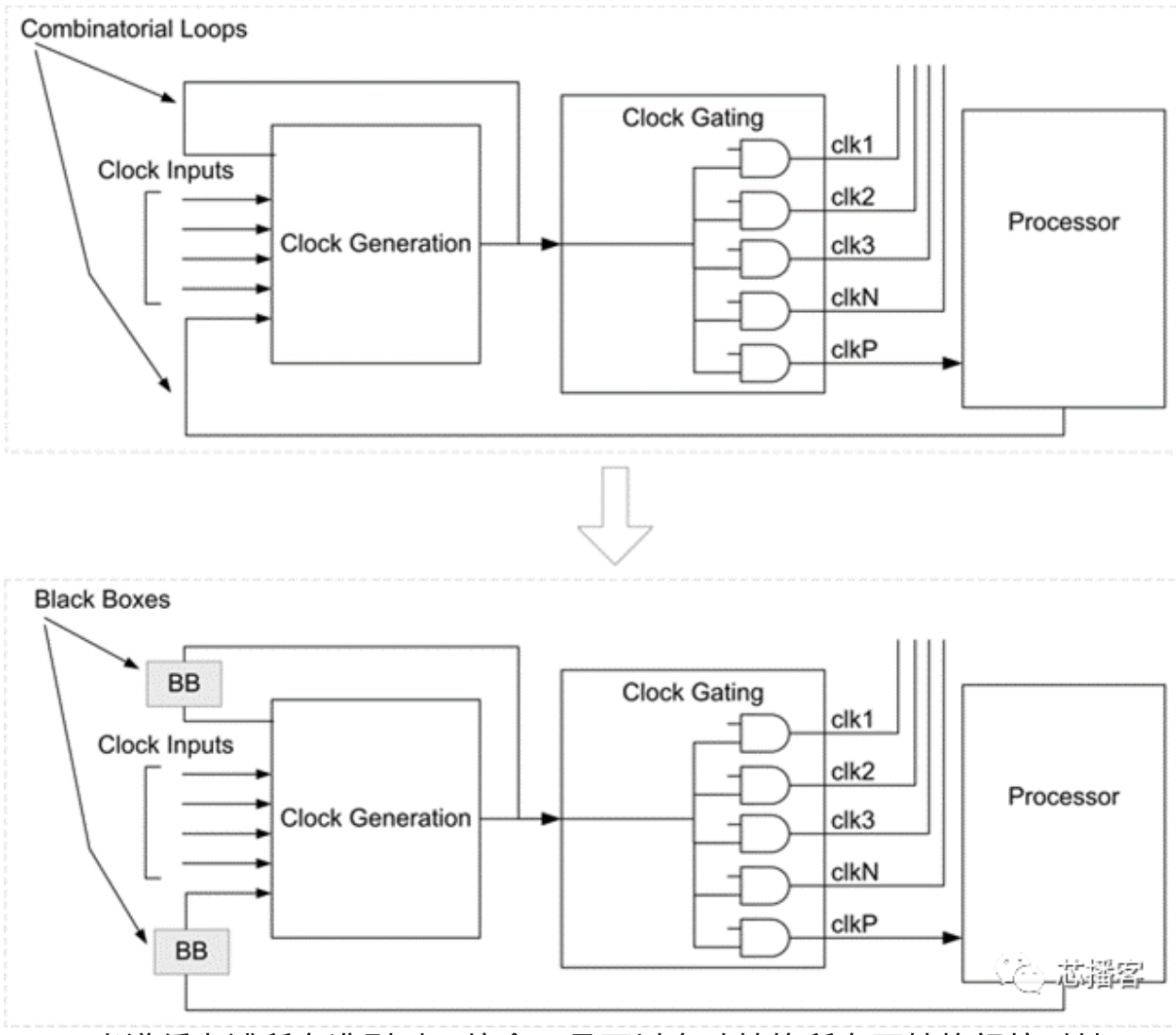

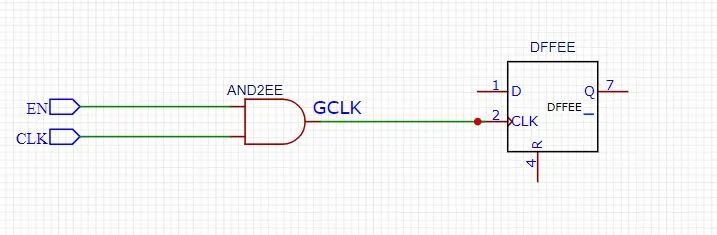

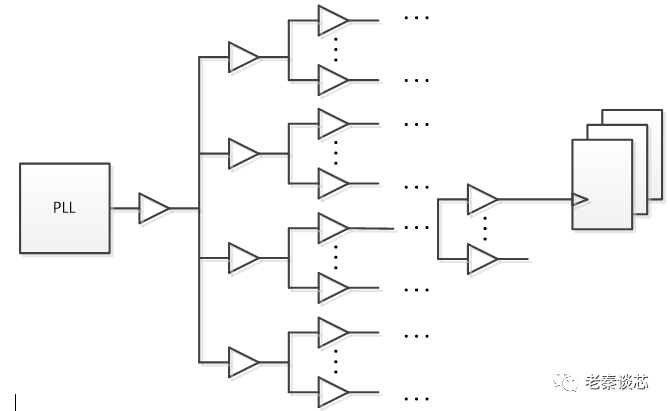

TypeC协议的UHF RFID标签基带处理器的的优化和实现。##降低功耗主要方法##RTL阶段手工加时钟门控##综合阶段工具插于集成门控单元##时钟树综合阶段优化功耗及结论

2014-03-24 14:36:30 3743

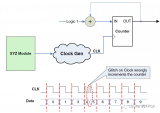

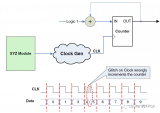

3743 时钟XOR自门控(Self Gating)基本思路和时钟门控类似,都是当寄存器中的数据保持不变时,通过关闭某些寄存器的时钟信号来降低设计的动态功耗。不过XOR 自门控是利用异或门(XOR)将存储在寄存器中的数据与到达寄存器的数据引脚的数据进行比较,输出门控时钟使能信号。

2024-01-02 11:34:36 433

433

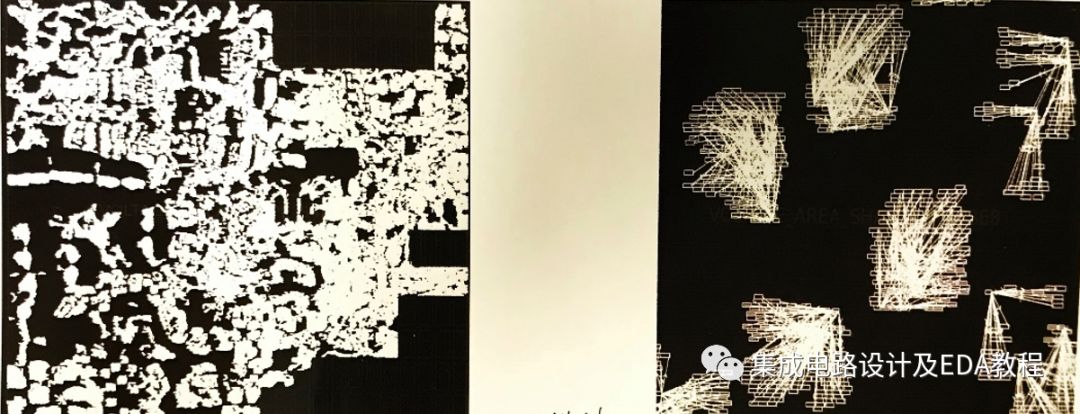

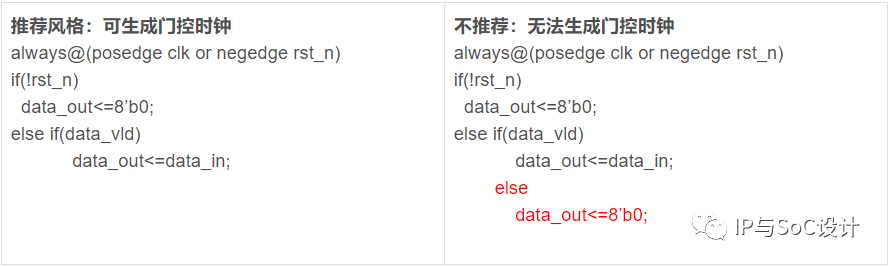

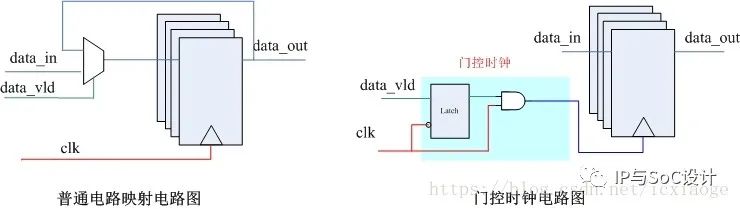

FPGA设计中,经常会出现由于设计不合理产生的布线问题,较为突出的一点就是门控时钟和多扇出问题。门控时钟指的是不用FPGA内部的全局时钟资源BUFG来控制触发器的时钟沿输入端而是采用组合逻辑和其它

2012-01-12 10:40:20

门控开关中元器件封装

2015-04-19 12:42:59

门控开关原理图优化2

2015-04-16 20:59:00

AT32F4xx TMR挂起模式演示AT32F系列 TMR门控模式的使用方法。

2023-10-27 06:21:33

喜我对时钟门控有一些疑问。从我所读到/学到的东西 - 时钟门控可用于低功率fpga设计(关闭时钟以防止元件切换以节省功率)。但是,我还读到时钟门控很糟糕,因为它可能会引起系统故障。我想我已经看到了

2019-02-21 10:21:41

HC32F460时钟系统简介Stark-2021-05概述目前只是调试了 GPIO 和 UART,感觉很有必要把时钟这部分补充说明一下,之前的文章中提到 GPIO 口没有时钟的门控时钟,之前大学玩 ST 单片机时候,那个 GPIO 的端口初始化是需要使能 GPIO_PORT ...

2021-12-06 06:43:30

什么是LIN总线技术?LIN总线技术在门控系统中有哪些应用实例?

2021-05-19 06:29:48

TIM1的门控部分还是有点理解难度的。看了两个多小时的数据手册,最后总结出来其实TIM1的门控就是硬件三态门,只是在简单的三态门逻辑基础上有提升。控制TIM1计数的门控源有4个,分别如下图所示一般

2021-11-25 08:42:02

很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。1.全局时钟对于一个设计项目

2012-12-14 16:02:37

我在一个图像项目里用来很多的门控时钟来产生需要的时序波形,这样程序很不稳定,图像晃动很大,我猜想是不是因为门控时钟太多,程序不稳定,但是又没有方法替代门控时钟(使能时钟不行),有没有关于门控时钟的建议???????????就是门控时钟的代替方法或者怎样减少对程序的危害。

2012-10-28 22:39:00

原语只用用全局时钟处理,不能作为接口使用。也不知道有什么办法可以解决??(2)在用计数器分频后的信号做为下级的时钟信号时间好像也会有警告 生成了 门控时钟,这个问题好像在与计数器分频后的信号不能在做分支同时给于下面几级做时钟信号,这样可能会在级点上产生逻辑门电路吧。

2015-06-16 19:34:01

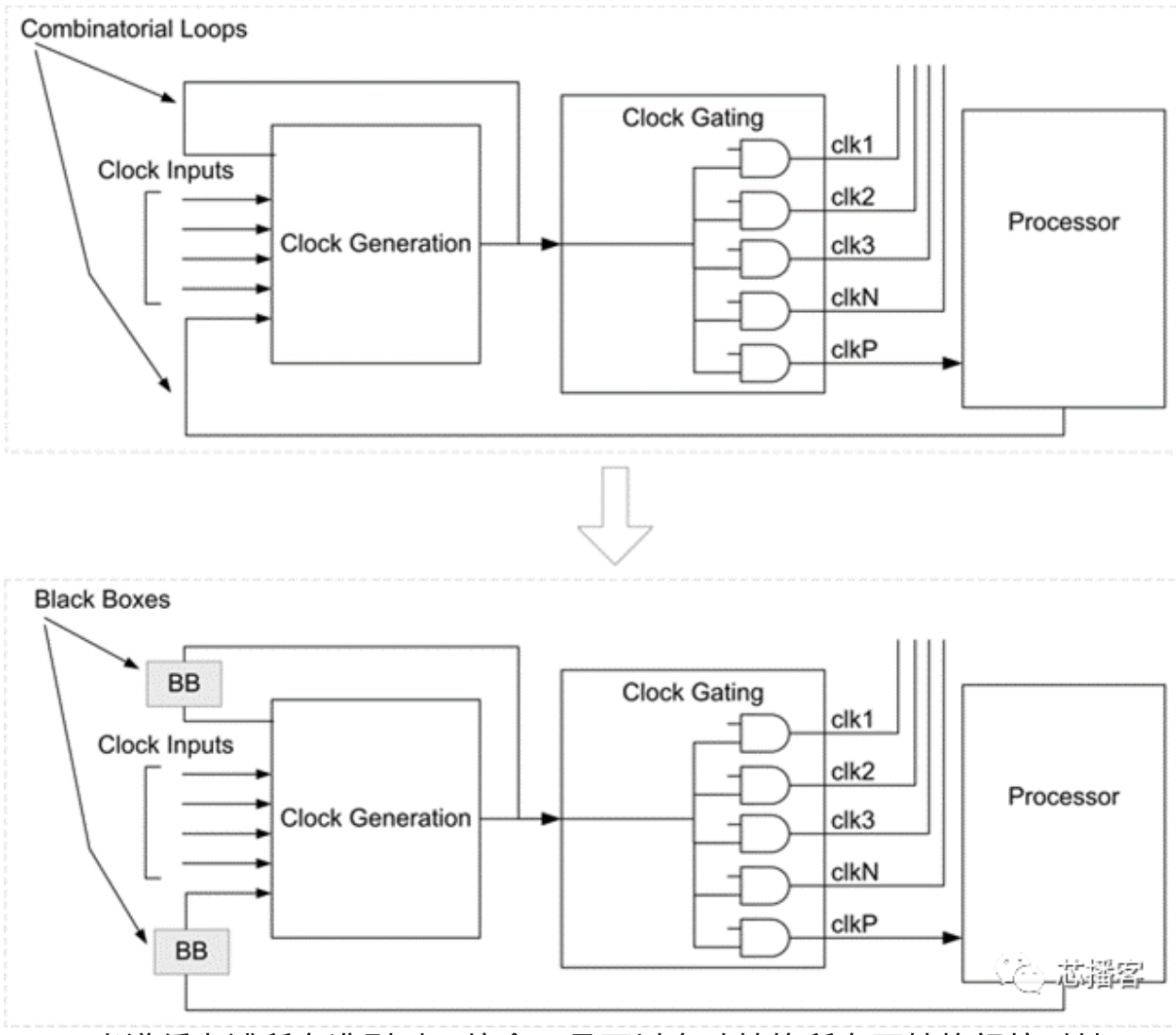

的情况。如果提供了精确的时钟图以及带有时钟原理相关信息的网表交递,就能够更快地弄清导致此状况的问题。 总体图或是代表设计中所有时钟(含门控逻辑)的图非常有用。这要么是采用画图软件,要么是使用电路图捕获工具

2017-06-08 10:22:51

什么是时钟门控?有几个因素会影响电路的功耗。逻辑门具有静态或泄漏功率,只要对其施加电压,该功率大致恒定,并且它们具有由切换电线产生的动态或开关功率。Flip-flop触发器非常耗电,大约占总功率

2022-12-19 17:09:05

什么是门控时钟?

2021-11-05 07:26:10

1、什么是门控时钟?在解释何为门控时钟之前,有必要了解为什么需要门控时钟。集成电路工艺节点的提升带来了芯片集成度的极大提高,集成电路工艺节点的提升带来了芯片集成度的极大提高。SoC设计的功耗包含

2021-07-30 06:11:00

的竞争,因此将电路分成多个电源域并根据要求关闭它们,并且在设计每个时序电路的同时节省功耗,这两点至关重要。时序电路(如计数器和寄存器)在现代设计中无处不在。本文以约翰逊计数器为例介绍了如何采用有效门控时钟

2018-09-30 16:00:50

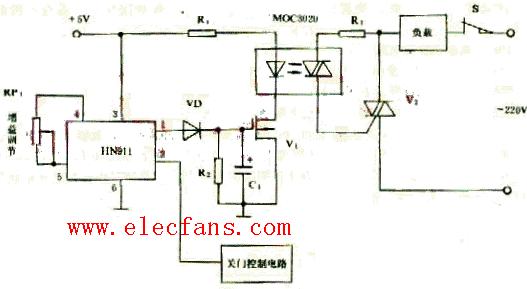

基于GSM模块TC35的智能门控安防系统硬件设计基于GSM模块TC35的智能门控安防系统软件设计

2021-06-01 06:29:04

大家看看这个阀门控制电路有问题吗?FA是阀门线圈

2013-05-31 10:51:01

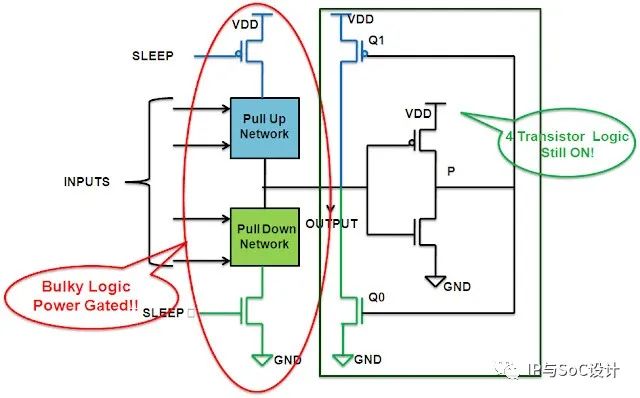

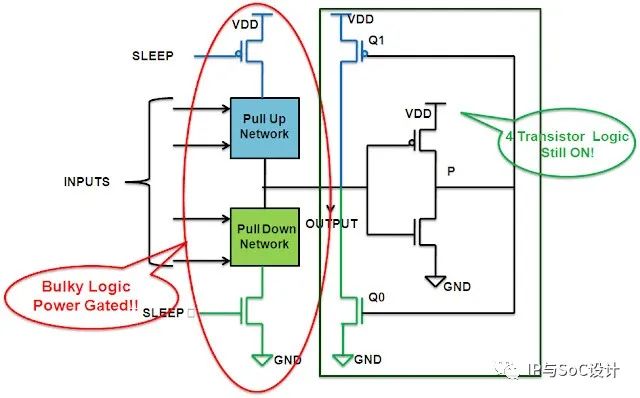

第五章 电源门控设计part1由于第五章内容太多,且这一个章节将的内容都是全书的重点,所以我将其拆分成几个部分来写,这是第一部分。5 电源门控设计这一章把电源门控的每一个组成部分从前端、RTL的视角

2021-12-31 06:49:25

嗨,PSOC4的一个局限性是,它不可能使用时钟信号来实现时钟以外的任何其他目的。我需要一个门控时钟输出为我的组件。我知道通常的方法是使用一个比需要快两倍的时钟,但我怀疑是否可以用另一种方式。我试图在

2019-07-19 11:10:25

大家好,我喜欢BUFGCTRL和BUFHCTRL用于XC7V2000T中的时钟门控。 BUFGCTRL耗尽,但仍有一些模块,时钟门控无法映射到一个时钟区域,BUFMRCTRL无法在我的设计中使用。当

2020-07-27 14:26:34

你好, 我需要创建一个需要通过一些启用进行门控的Diffenertial时钟。我怎样才能做到这一点? 我能做那样的事吗?CLK_i0:OBUFDSport map(I => CLK100MHZ

2019-04-11 11:57:23

利用业余时间,在半年时间内完成智能门控产品

2013-10-18 10:45:38

由于快毕业了,不知道该怎么写论文,毕设是做基于蓝牙的智能家居门控系统的设计,怕论文查重,所以求一个冷门的单片机型号,能够基本满足智能家居门控系统(EEPROM密码保存、能接液晶显示、接时钟模块、接继电器、接蜂鸣报警器、接矩阵键盘)的那种

2018-05-03 12:02:41

作为用于控制阀门的制动系统新项目的一部分。

我们正在寻找一个多通道阀门控制器,控制器封装集成功率部分(MOSFET),通过SPI(串行外设接口)与MCU通信,目标是:

在电流调节中控制 8 个阀门

2023-05-24 08:05:31

我用到了TIM4和TIM2,TIM4输出一个PWM波,TIM2采用门控模式,当TIM4为低电平的时候,TIM2开始对外部脉冲进行计数,高电平时即停止计数。目前我在网上看到的,都是主定时器输出高电平

2019-01-10 09:25:03

滚动码车库门控制系统系统采用PIC16F72作为控制芯片,程序包括滚动码接收,解码,学习子程序、24C02读写子程序、AD转换子程序、开关车库门子程序。系统能够使用15个遥控器,关门过程具有遇阻反弹功能。

2013-01-28 09:08:01

DN2- 用于数字滤波和门控测量的信号采样

2019-06-20 14:04:49

电房门控开关,你真的了解吗?!以上具体视频的链接地址: 免费的 ,http://pan.baidu.com/s/1o681lVk,不妨看看挺有用的

2015-04-12 12:26:42

电源门控可以降低泄漏功耗吗?有哪几种情况采用PG能显著减小泄漏功耗呢?

2022-02-11 06:34:36

《Low Power Methodology Manual For System-on-Chip Design》读书笔记4 电源门控概述4.1 动态和泄漏功耗曲线电源门控最基本的思想是为电路提供两种

2021-12-31 08:14:58

和发送数据,处理异步信号,以及为带门控时钟的低功耗ASIC进行原型验证。 这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步单元(触发器、同步RAM块以及流水乘法器等)都使用同一个网络

2022-10-14 15:43:00

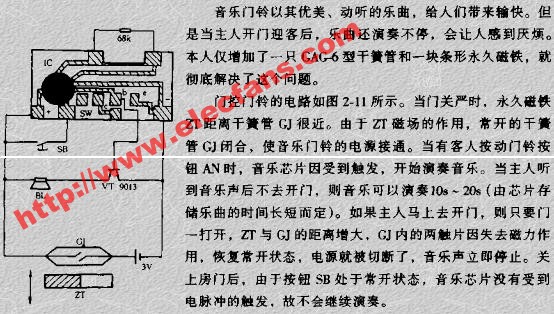

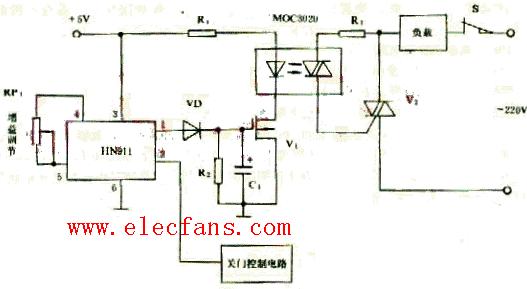

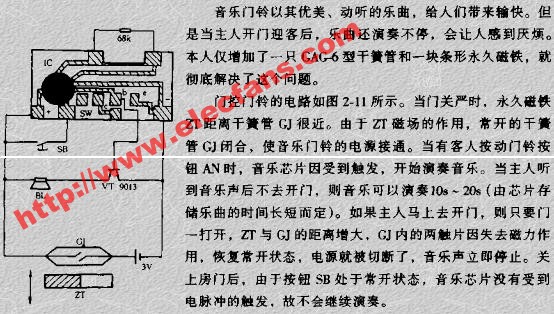

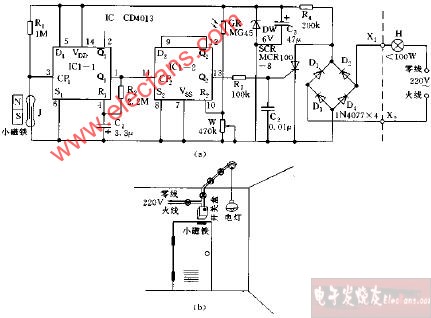

门控音乐门铃电路图

2009-05-19 11:59:10 17

17 随着深亚微米技术的发展,功耗已经成为现代超大规模集成电路设计中的一个主要设计约束.本文在设计多点控制协议MPCP模块中,采用插入门控时钟这一技术以降低芯片功耗.针对

2009-08-13 09:30:57 21

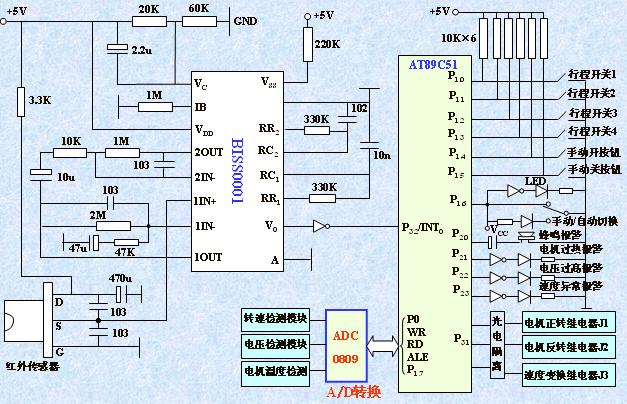

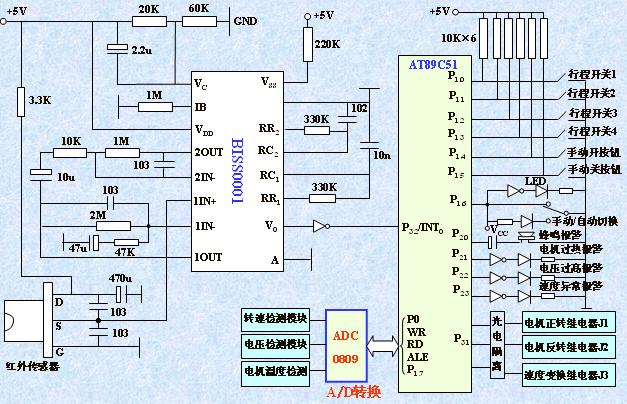

21 基于ARM9+Linux轨道交通门控器测试设备的研制:日前轨道交通门控器定期检修维护尚无相应现场检测仪,现场手工测试效率低、准确性不高,并且要求对门控器设计原理很熟悉。该文在

2009-09-29 11:26:39 29

29 阐述了如何运用门控时钟来进行CMOS电路的低功耗设计。分析了门控时钟的实现方式,如何借助EDA工具在设计中使用门控时钟,并且附有部分脚本程序,以一个watchdog timer模块为例,给出

2009-11-19 11:49:37 22

22 自动门控制器电路图

2008-04-25 11:02:48 23059

23059

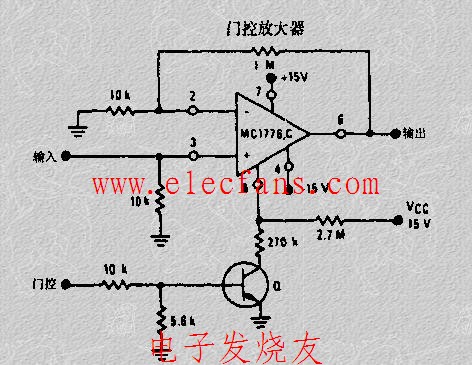

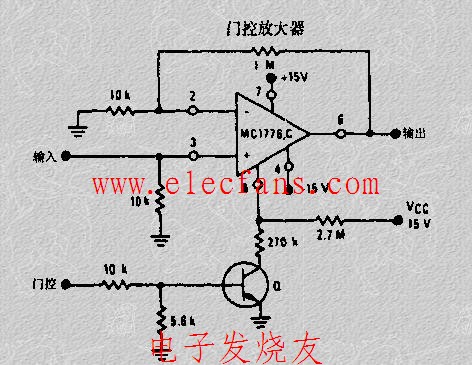

门控放大器电路

2008-06-12 23:24:51 1201

1201

门控音乐门铃

2008-08-27 15:16:09 503

503

可关断晶闸管(GTO-门控晶闸管)

可关断晶闸管GTO(Gate Turn-Off Thyristor)亦称门控晶闸管。其主要特点为,当门极加负向触发信号时晶闸管能自行关断。

前已述及,普

2009-04-26 11:39:46 2570

2570

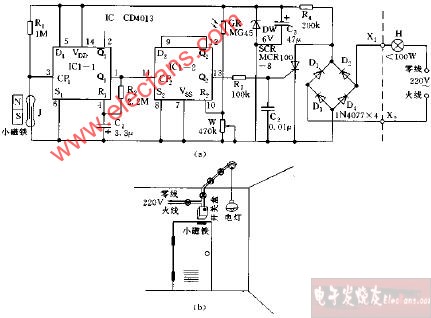

家庭卫生间门控灯电路图

2009-06-12 10:51:32 5096

5096

红外线自动门控制系统原理图

2009-10-25 11:29:14 7026

7026

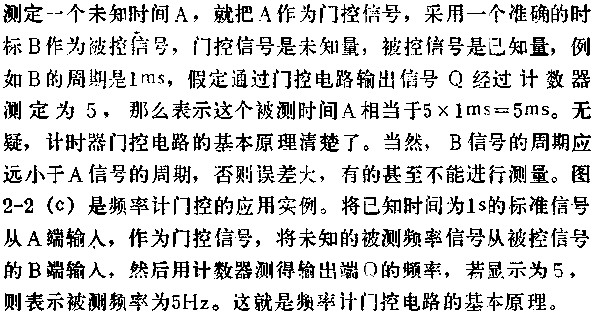

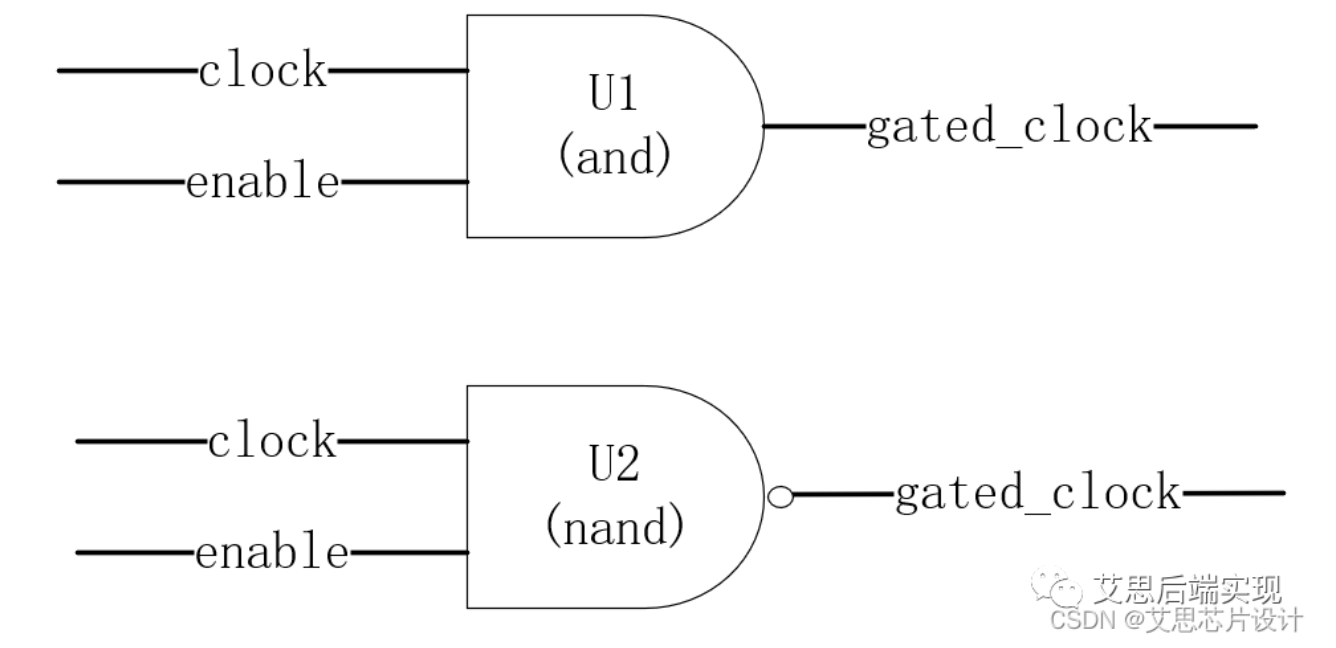

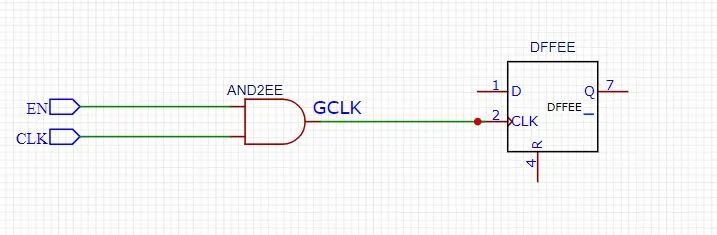

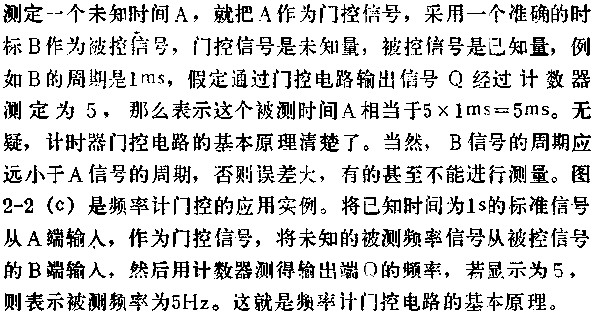

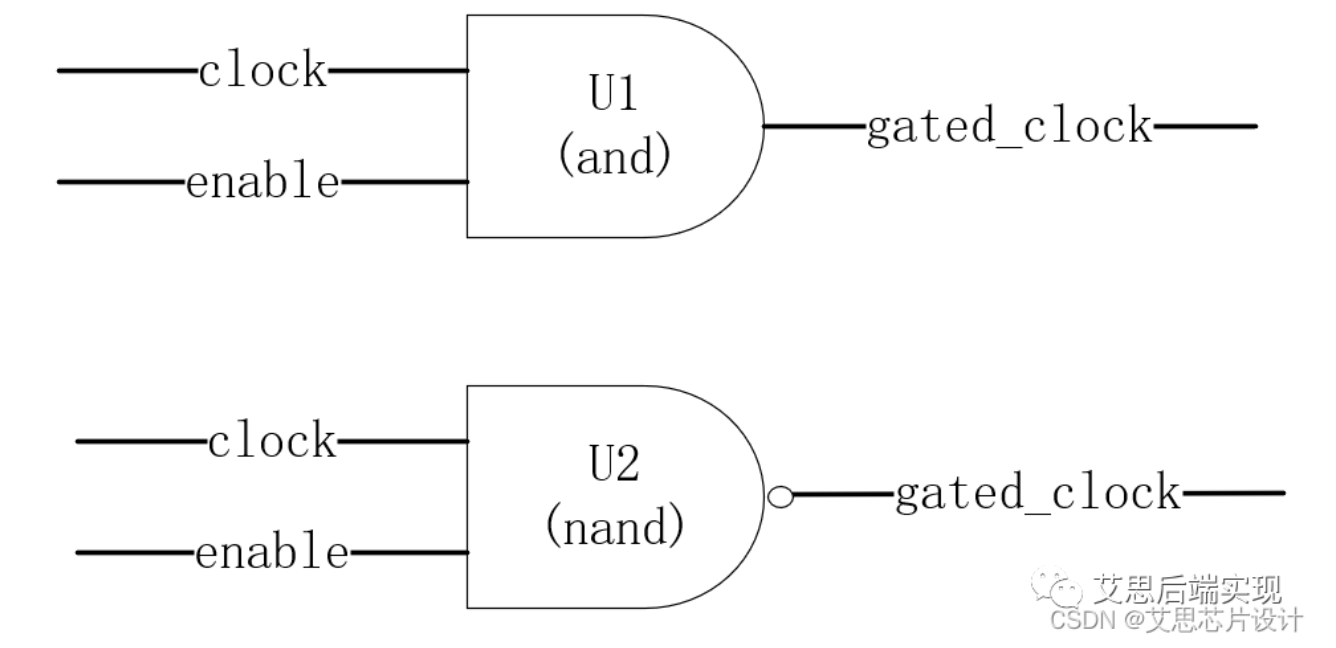

图2-2是采用与门组成的门控电路,门控电路被广泛应用于数字仪表中,例如当需要用某一个信号去控制另一个信

2010-09-12 22:00:53 3490

3490

在众多低功耗技术中,门控时钟对翻转功耗和内部功耗的抑制作用最强。本文主要讲述门控时钟技术的具体实现。另外,基于高阈值单元具有较低的功耗,设计采用高阈值单元库。

2011-02-21 09:31:57 3183

3183

摘要:门控时钟技术一直以来是降低芯片动态功耗的有效方法,文章结合片上系统(SOC)的结构特性和设计特点,分析已有的各种门控时钟技术的优缺点,指出这些缺点是SOC设计中严重障碍,随后抽象出IP核工作模型,提出了仅用非常简单的逻辑就可以方便应用于IP核

2011-02-23 13:53:11 36

36 传统的距离门控电路多采用分立元器件,工作频率和控制精度均十分有限,难于满足重复频率高的测距需求.通过分析高重复率距离门控的时序,提出并实现了一种基于FPGA的高重复率距离门控电路方法.该方法充分发挥了FPGA在运算、存储、时钟管理等方面的优势:采

2011-03-15 15:05:00 24

24 所谓门控时钟就是指连接到触发器时钟端的时钟来自于组合逻辑;凡是组合逻辑在布局布线之后肯定会产生毛刺,而如果采用这种有毛刺的信号来作为时钟使用的话将会出现功能上的错

2011-09-07 16:11:32 34

34 在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

赛灵思推出业界首款自动化精细粒度时钟门控解决方案,该解决方案可将 Virtex-6 和 Spartan-6 FPGA 设计方案的动态功耗降低高达 30%。赛灵思智能时钟门控优化可自动应用于整个设计,既无

2012-01-17 15:34:58 34

34 低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析

2015-11-19 14:50:20 0

0 门控时钟的资料,关于FPGA方面的资料。有需要的可以看看

2016-05-10 16:31:07 11

11 基于CPLD的高精度门控电路的设计,下来看看。

2017-01-13 13:46:17 7

7 可变延迟高压门控开关电路

2017-01-22 20:29:21 7

7 本文中,我们介绍了一款节能设计,即用带有门控时钟的多级可编程约翰逊计数器系统来取代多个时钟分频器,该计数器可提供8至任何偶数值(在本文中为38)的时钟分频因子。下面,我们将探讨实施细节和该技术的优劣。

2017-09-15 15:40:12 10

10 ,因此将电路分成多个电源域并根据要求关闭它们,并且在设计每个时序电路的同时节省功耗,这两点至关重要。时序电路(如计数器和寄存器) 在现代设计中无处不在。本文以约翰逊计数器为例介绍了如何采用有效门控时钟来设计高能

2017-10-25 15:41:59 25

25 ,因此将电路分成多个电源域并根据要求关闭它们,并且在设计每个时序电路的同时节省功耗,这两点至关重要。时序电路(如计数器和寄存器)在现代设计中无处不在。本文以约翰逊计数器为例介绍了如何采用有效门控时钟来设计高能效

2017-11-15 15:40:13 12

12 很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

2017-11-25 09:16:01 3907

3907

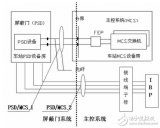

屏蔽门控制系统主要由中央接口盘(PSC)、就地控制盘(PSL)、门控单元(DCU)、通讯介质及通讯接口及外围设备等组成。中央接口盘(PSC)又由主监视系统(MMS)、两个单元控制器(PEDC)、接线

2018-07-20 09:55:00 19189

19189

不建议使用组合逻辑时钟或门控时钟。组合逻辑和门控时钟很容易产生毛刺,用组合逻辑的输出作为时钟很容易使系统产生误动作。

2020-03-25 11:26:58 1448

1448 门控时钟的应用,在fpga中使用门控时钟是非常不推荐的一件事情。asic中虽然也不赞成使用,但是也没什么大关系。

2020-06-04 14:56:53 8007

8007

。 不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。 FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须

2020-12-11 10:26:44 1482

1482 组合逻辑生成的时钟,在FPGA设计中应该避免,尤其是该时钟扇出很大或者时钟频率较高,即便是该时钟通过BUFG进入全局时钟网络。

2020-10-10 10:28:32 3639

3639

时钟门控(Clock Gating)是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。 为什么需要时钟门控:大多数SoC都是power

2021-06-13 16:48:00 2289

2289 门控开关电路免费下载。

2021-06-21 10:55:26 27

27 门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分析门控时钟。 一、什么是门控时钟 门控时钟技术(gating

2021-09-23 16:44:47 12192

12192

1 CRG的SPEC参考1.1 时钟设计需求 (1)生成AHB时钟,APB时钟,RTC时钟;(2)AHB最高时钟频率为98MHz;(3)APB时钟为AHB同步时钟,且可以配置AHB时钟的1/2,1

2021-11-05 17:35:59 8

8 TIM1的门控部分还是有点理解难度的。看了两个多小时的数据手册,最后总结出来其实TIM1的门控就是硬件三态门,只是在简单的三态门逻辑基础上有提升。控制TIM1计数的门控源有4个,分别如下图所示一般

2021-11-16 19:21:01 7

7 HC32F460时钟系统简介 Stark-2021-05概述目前只是调试了 GPIO 和 UART,感觉很有必要把时钟这部分补充说明一下,之前的文章中提到 GPIO 口没有时钟的门控时钟,之前大学玩 ST 单片机时候,那个 GPIO 的端口初始化是需要使能 GPIO_PORT ...

2021-11-23 18:06:44 7

7 的目的是为了省电,使用了所谓时钟门控的技术。寄存器是基于什么的?当然是触发器!!!准确地说应该是D触发器触发器的赋值是一定需要时钟的, 而寄存器的时钟是由总线时钟提供的,就是说没有总线时钟的话,你给寄存器值它是不会读入的。换句话说

2021-12-04 11:36:13 7

7 第五章 电源门控设计part1由于第五章内容太多,且这一个章节将的内容都是全书的重点,所以我将其拆分成几个部分来写,这是第一部分。5 电源门控设计这一章把电源门控的每一个组成部分从前端、RTL的视角

2022-01-11 13:19:00 0

0 只有当FPGA工程需要大量降低功耗时才有必要引入门控时钟,若必须引入门控时钟,则推荐使用基于寄存器的门控时钟设计。

2022-07-03 15:32:17 1617

1617 电子发烧友网站提供《WiFi门控板Rev开源分享.zip》资料免费下载

2022-08-03 09:20:18 8

8 的可能更多,可能约为 40%!全局时钟无处不在,而且每个周期都会切换两次。正如我们将看到的,时钟门控避免了在不需要时钟脉冲时切换时钟。这减少了时钟分配和触发器的功耗,甚至可以减少逻辑门的动态功耗。

2022-12-12 11:06:44 508

508 作为使用PAL、GAL或CPLD器件实现非易失性门控功能的替代方案,这些电路使用串行接口控制的数字电位器(MAX5427或MAX5527)存储门控信号(模块或发送)。

2023-01-12 11:30:52 655

655

: ·同步电路与异步电路; ·时钟/时钟树的属性:偏移(skew)与时钟的抖动(jitter)、延时(latency)、转换(transition)时间; ·内部时钟; ·多路复用时钟; ·门控时钟

2023-01-28 07:53:00 2107

2107

当寄存器组的输出端没有驱动或没有变化时,可以关掉寄存器组的时钟来减少动态功耗,此谓门控时钟 (Clock Gating, CG) 技术。

2023-03-29 11:37:16 5635

5635

门控时钟是一种在系统不需要动作时,关闭特定块的时钟的方法,目前很多低功耗SoC设计都将其用作节省动态功率的有效技术。

2023-04-20 09:15:13 764

764 现代FPGA综合工具会自动执行门控时钟转换,而无需更改RTL代码中的设计,然而,我们可能需要适当地手动指导综合工具执行门控时钟变换。

2023-05-23 17:38:19 1009

1009

通过门控方式不同,一个门控时钟通常可以分为下面基类,

2023-06-19 16:49:02 1589

1589

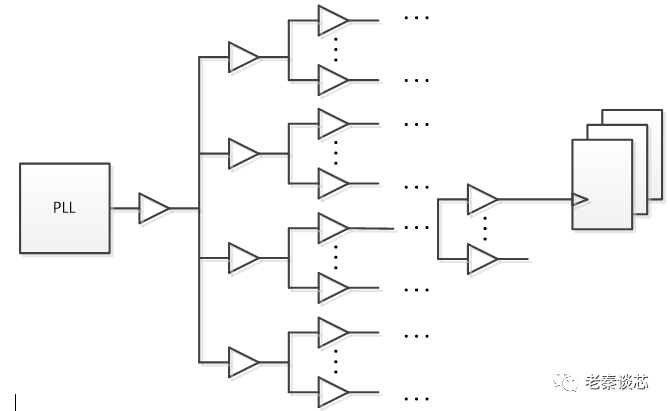

芯片功耗组成中,有高达40%甚至更多是由时钟树消耗掉的。这个结果的原因也很直观,因为这些时钟树在系统中具有最高的切换频率,而且有很多时钟buffer,而且为了最小化时钟延时,它们通常具有很高的驱动强度。

2023-06-29 15:33:18 1515

1515

开始之前,我们首先来看一下什么是时钟门控(clock gating)技术,顾名思义就是利用逻辑门技术控制时钟的通断。

2023-06-29 15:38:30 1241

1241

时钟门控(Clock Gating)** 是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。

2023-06-29 15:58:13 1018

1018

门控时钟技术可以用来降低电路的动态功耗,且在一定程度上能减小电路的面积。

2023-06-29 16:45:08 652

652

什么是时钟电路?什么是脉冲?时钟电路是如何生成脉冲的? 时钟电路是一种电路,它产生的周期性的信号被用作计算机系统的基准。时钟电路产生的信号被称为时钟脉冲或时钟信号。在计算机系统中,时钟信号用于同步

2023-10-25 15:14:17 795

795 标题为“电源门控”的文章演示了电源门控单元的实现以及它如何帮助最大限度地减少 SoC 的泄漏功耗。其基本原理是切断从电池(VDD)到接地(GND)的直接路径。虽然有效地节省泄漏功率,实施讨论遭受

2024-01-08 12:27:12 182

182

之前我的一个设计实例“该怎么让门控555非稳态多谐振荡器顺利得到使用?”解决了传统拓扑的555非稳态电路在启动时由RESET引脚门控从振荡关闭到振荡开启时产生的第一个脉冲过长的问题。

2024-02-15 09:00:00 344

344

电子发烧友App

电子发烧友App

评论