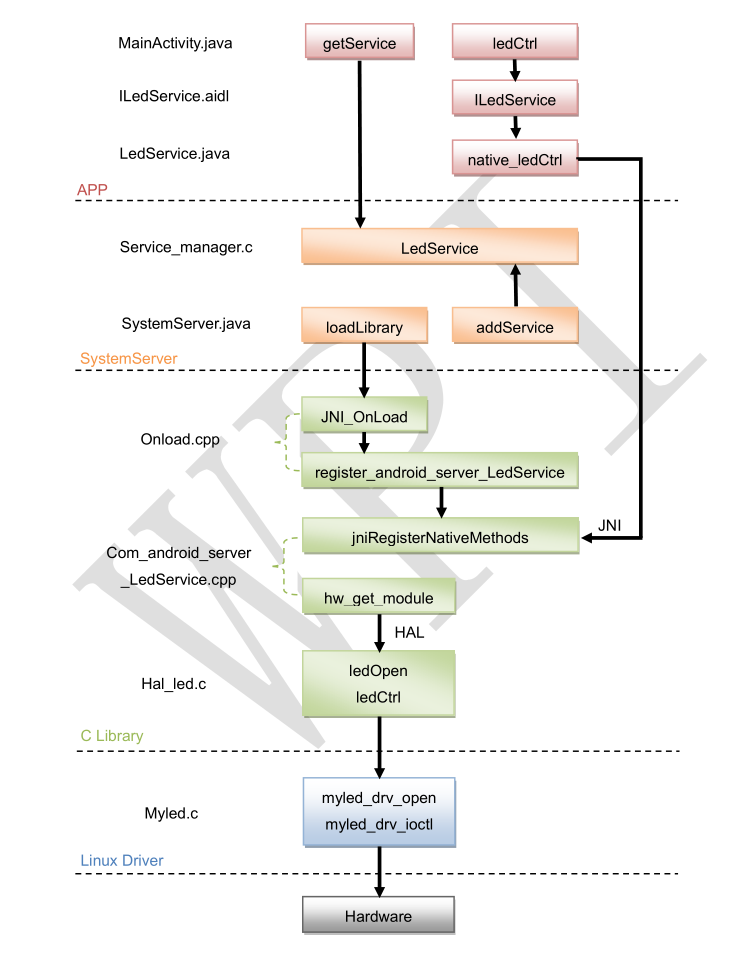

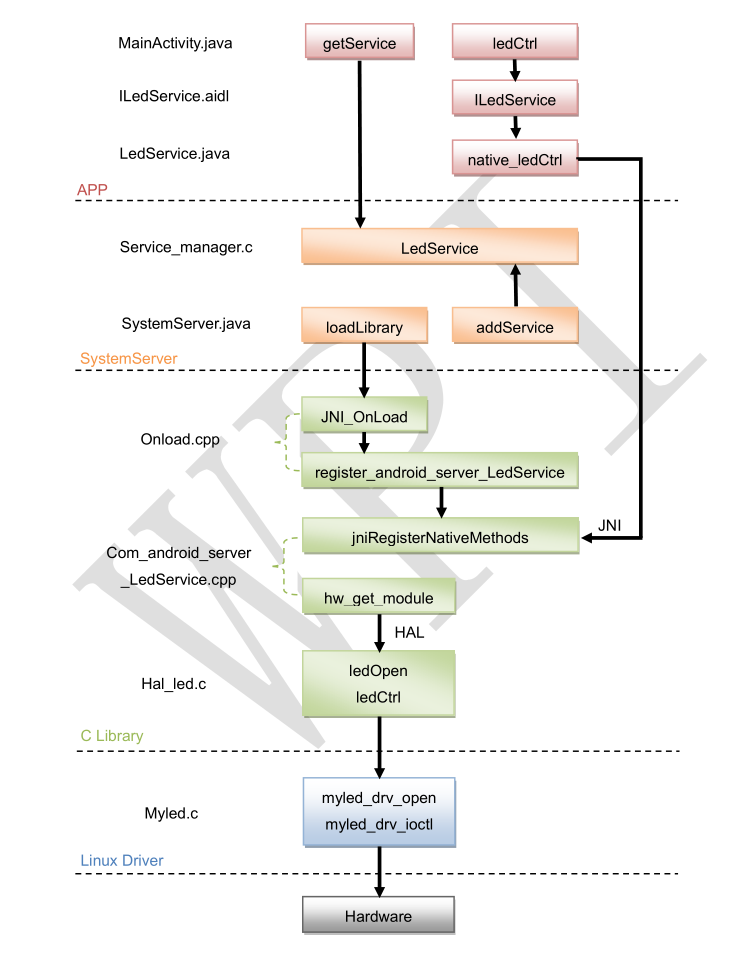

本文我们要讲的是在用 i.MX8 平台开发时,Android APP 如何进行访问硬件驱动。

2023-12-04 13:50:10 379

379

FPGA 如何进行浮点运算

2015-09-26 09:31:37

的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就

2012-08-11 10:27:54

制作成功,所以修改引脚分配是木有用的,这才是欲哭无泪的地方啊!!!!针对于这种情况,有没有其他解决方案,而不是从新设计硬件PCB板的,求助!!!!!

2012-06-19 10:26:30

FPGA在Verilog程序写完后,针对实物芯片,如何分配引脚?!在QtsII软件中仿真后有引脚分配,但感觉和实际的引脚应该有区别吧?问,该如何区分?!

2013-04-03 13:14:13

分配引脚的四种方法:(Quartus II 13.0sp1(64-bit)) 1、常规方法,利用PinPlanner命令,适用于引脚使用比较少的工程,简洁方便; 2、使用.csv文件进行引脚分配

2018-07-03 07:22:06

在FPGA芯片手册中如何查询芯片引脚分配在写完硬件设计语言后进行I/O分配时,无法与芯片取得联系

2018-10-04 08:28:39

FPGA如何对引脚进行分块?是由VCC的电压不同进行自行设计分块?还是每个块的引脚都是固定的?在进行DDR3与FPGA的硬件连接时,由FPGA的芯片手册得采用SSTL_15电压标准,即VDDQ

2021-11-29 16:10:48

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-06-17 08:55:43

访问。图3 - 双QSPI配置接口(11个引脚)允许配置位流在两个QSPI器件之间进行分区,从而有效地将读取数据传输速率提升一倍。当大型FPGA器件需要以最快的方式传输大配置(即高密度)配置比特流

2021-09-03 07:00:00

FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑

2024-01-10 22:40:14

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-03-25 18:46:25

的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就

2012-08-11 11:34:24

用tcl文件配置引脚后 点击 Run 后就退出到代码界面,然后查看了引脚是否分配成功发现没有分配,这是怎么回事呢?要怎么解决?

2013-09-25 20:00:30

我是fpga开发板的新手,我想知道如何开始使用引脚分配,特别是u*** / serial引脚连接。任何其他pin信息都会有所帮助谢谢

2020-07-19 11:47:31

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

Arduino Nano是什么?Arduino Nano有哪些引脚?Arduino Nano的引脚是怎样进行分配的?

2021-10-19 07:59:21

有哪位大侠,能讲解一下DMK如何进行硬件调试???(不是软件设计,而是打开一个程序,要看看它运行到哪里了?该如何做?先前51单片机用的少,我查了一些资料,网上也搜了一下,都不是很具体。)

2014-05-03 16:06:59

EtherCAT总线运动控制器硬件是如何进行接线的?EtherCAT总线运动控制器有哪些参数设置?

2021-07-15 13:02:24

唯一一个由FPGA驱动到CPU的逻辑电路。我的推论是,由于该FPGA工程没有对CPU相关的输入输出引脚进行时序约束,两次编译会导致双向数据总线的输出使能信号的响应差异,这一差异进一步影响了FPGA驱动

2012-02-24 10:49:28

USB OTG的工作原理是什么?IP设计原理是什么?如何进行IP模块设计?USB OTG IP核有什么特性?如何对USB OTG IP核进行FPGA验证?

2021-04-27 06:44:33

Intel 8253有哪些引脚?Intel 8253的工作模式是什么?Intel 8253与CPU是如何进行连接的?

2021-08-06 08:06:26

单片机和PLC的应用分别有哪些?PLC与单片机硬件通信的原理是什么?PLC与单片机硬件是如何进行通信的?

2021-08-12 07:34:23

在网上看到一个管脚分配的帖子,正好调自己的板子要用,方法够简单,共同学习,在编写自己的管脚扽陪内容时候可以在AD中导出netlist,对应里面的内容进行简单的编辑就可以做好自己的板子的TCL了。一

2018-07-03 12:56:11

STM32F407ZGT6的引脚是如何进行接线的?如何去实现STM32F407ZGT6串行通信的代码?

2021-10-21 06:00:51

`Xilinx FPGA入门连载12:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植复制

2015-10-14 12:23:31

gpio这个接口复用功能是在硬件设计时分配的吗?比如uart两个接口是对应了gpio0 gpio1 是在哪分配的?有io mux在哪?改变复用逻辑。

2023-08-11 07:06:42

、Starter开发板,使用时请根据具体使用的FPGA硬件平台,先在引脚分配界面中删除所有引脚分配位置后,再在Quartus软件中运行对应板卡和对应显示设备的tcl脚本文件以完成引脚分配。每个板卡提供了

2020-02-04 19:42:43

管脚分配有两种,一种就是手动,一个管脚 一个管脚的分配,还有一种就是使用脚本进行分配。一、手动引脚分配。菜单栏中:AssignmentsàPinPlanner出现如下的界面:在最下面,可以看到

2016-09-03 09:26:03

怎样去编写SimpleFOC硬件端程序呢?上位机与SimpleFOC是如何进行连接的?

2021-12-21 06:44:57

主存中存储单元地址是如何进行分配的?存储芯片的容量有多大?

2021-10-19 08:25:52

本文旨在以具体案例探讨企业如何进行IPv6地址规划与分配,从而合理和有效地使用IPv6地址资源。

2020-12-28 07:14:11

是基于什么?拍拍脑袋,随心所欲?非也,引脚的分配一定是有理有据,那就是我们已经设计好的硬件原理图。如图3.21所示,这里FPGA所使用的时钟信号ext_clk对应原理图上的网络名CLK_25M,它的FPGA引脚号是E15,那么我们就给它分配E15。 图3.21 时钟信号的引脚连接原理图 `

2016-09-14 16:59:04

`例说FPGA连载33:PLL例化配置与LED之使用Tcl Console进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-17 17:50:15

`例说FPGA连载34:PLL例化配置与LED之使用TCL Scripts进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-23 09:34:42

刚开始学习fpga,对引脚分配的问题不是很理解,求高手给予帮助 例如fpga的线路板上23引脚接clk ,28引脚是空余的 ,那么在编程的时候我可以用 28引脚接clk 吗?

2013-01-06 15:24:21

①蜂鸟FPGA约束文件是适用于MCU200T板子吗?

②如果适用,那么在FPGA约束文件中的引脚约束是怎么对应到MCU 200T板子中?

eg:

比如这几条约束是怎么对应到MCU 200T板子中的引脚呢?

2023-08-16 06:58:04

嵌入式LINUX驱动学习之12内核内存分配一、头文件、函数及说明:一、头文件、函数及说明://头文件位置 : include/linux/slab.h/*申请内存函数:kmalloc()实现方式一般

2021-12-17 06:44:48

实际上输出还是3.3V,我们不去设置它也行。图7.6 引脚分配 查看SF-CY4开发板的原理图,如图7.7和图7.8所示,这里BEEP对应FPGA引脚号是38,那么前面我们就在Location列输入

2018-02-27 21:50:07

单片机存储是如何进行分配的?stm32的启动大致流程是怎样的?有什么办法来解决这个无效区域以缩小我们的固件大小呢?

2022-02-25 06:09:37

大家好,我刚开始学习FPGA并试图弄清楚哪些FPGA引脚可以分配我的数据信号。我正在使用FPGA Spartan 6封装TQG114器件LX9。查看产品规格,有102个可用的用户I / O.这是

2019-04-23 06:55:23

在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是

2015-01-06 17:38:22

生成器进行计数,以实现完成短脉冲时钟。任何人都可以指导我找正确的文章进行引脚分配然后将程序下载到主板上让我做一些测试吗?我是xilinx软件的新手。我感谢你的帮助。谢谢

2019-10-29 10:09:50

文件为txt文件中共有10000个数据点,每个数据点由6个元素组成,分别对应6路信号即6条曲线,每个波形由200个数据点组成,每个文件中共有50个波形如图后面那个 读后标记 如何进行下次数据的读取求解

2017-05-24 22:07:49

如何克服FPGA I/O引脚分配挑战?

2021-05-06 08:57:22

我使用LX30T FF665-1 FPGA,我想使用GTP。当我在ISE 9.1.3中打开“assign package pins”时,我发现我无法为GTP分配端口的封装引脚。我打开了“编辑约束

2020-05-29 14:39:22

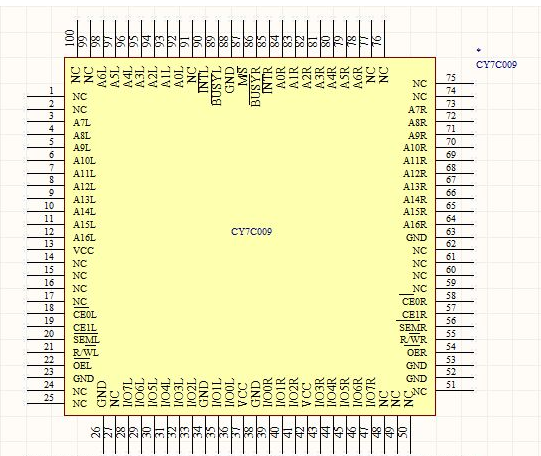

引脚都将转到fpga。我想将板作为第一步,以节省原型零件的费用,所以我试图找出在不使用ISE YET的情况下为地址线,数据总线等分配引脚的最佳方法。不会使用RAM。谢谢!以上来自于谷歌翻译以下为原文I

2019-01-21 06:02:55

计算机图形系统的主要硬件是什么?软件是如何进行配置的?

2021-10-11 09:35:59

在进行引脚分配时,看到如下图,不知道P、n、L、D、Q、C、三角形、五边形都代表什么意思,求大神解答,非常感谢

2019-03-20 06:35:15

想问问各位大神,在做FPGA的外围电路时,除了专用引脚,每一个功能模块对应的引脚是固定的吗?还是说用户I/O可以随意分配引脚给外围电路?

2019-04-08 08:43:16

我看第一个历程就没有讲解对应的引脚分配实现,就是assignments-Pin Planner,难道是在其他的地方,我没有找到吗

2019-05-15 06:35:30

请问哈FPGA的输入输出信号跟端口引脚一定是一一对应的吧?

2019-04-16 04:46:22

、PF3对应三个LED灯,但我看板子上PF1、PF2、PF3对应的是三个引脚针,引脚到底怎么分配的?有文档吗?

2018-08-14 06:16:41

集成在一块板子上的fpga和arm如何进行通信呢?

2022-11-07 15:31:04

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚信号指配的指导方针有

2010-11-08 18:23:52 868

868 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证

2011-01-25 18:19:39 163

163 现在的FPGA向引脚分配信号的任务曾经很简单,现在也变得相当繁复。

2016-07-27 20:24:00 6740

6740 引脚和区域约束也就是LOC约束(location)。定义了模块端口和FPGA上的引脚的对应关系。 那么我们应该怎么写呢?

2018-07-14 02:49:00 10273

10273 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2017-05-18 10:51:54 29124

29124

用户的指定、基于接口的连接(设计目标)、FPGA的引脚分配规则(FPGA规则)和FPGA在PCB板上的实际位置(相对位置)来进行自动综合的。自动引脚分配综合避免了用户在手动操作过程当中容易出现的错误

2017-11-17 20:36:09 5453

5453

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

2017-11-28 14:41:06 14538

14538

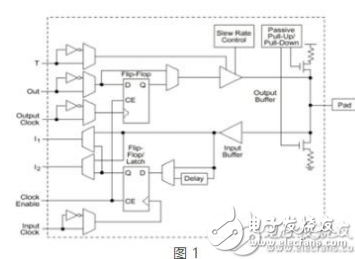

首先说IO standard:这个是用于支持对应不同的电平标准。FPGA IO口的电压由IO bank上的VCC引入。一个bank上引入3.3V TTL电平,那么此时整个bank上输出3.3V

2018-04-18 11:34:00 66543

66543

本文档内容介绍了MagicSOPC主板FPGA-IO引脚分配表,供参阅

2018-03-15 15:50:59 6

6 对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O引脚分配是必须面对的众多挑战之一。 由于众多原因,许多设计人员发表为大型FPGA器件和高级BGA封装确定I/O引脚配置或布局方案越来越困难。 但是组合运用多种智能I/O规划工具,能够使引脚分配过程变得更轻松。

2019-06-03 08:06:00 2312

2312 启动马达吧!快速,简单,有趣!本视频将向用户展示如何进行硬件连接,启动GUI并运行马达。

2018-11-28 06:04:00 2794

2794 在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

2020-09-02 09:20:21 12353

12353

介绍IO口与FPGA管脚对应关系表。

2021-03-18 10:02:26 12

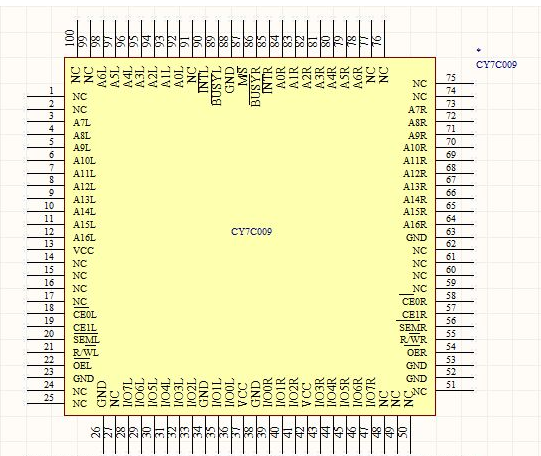

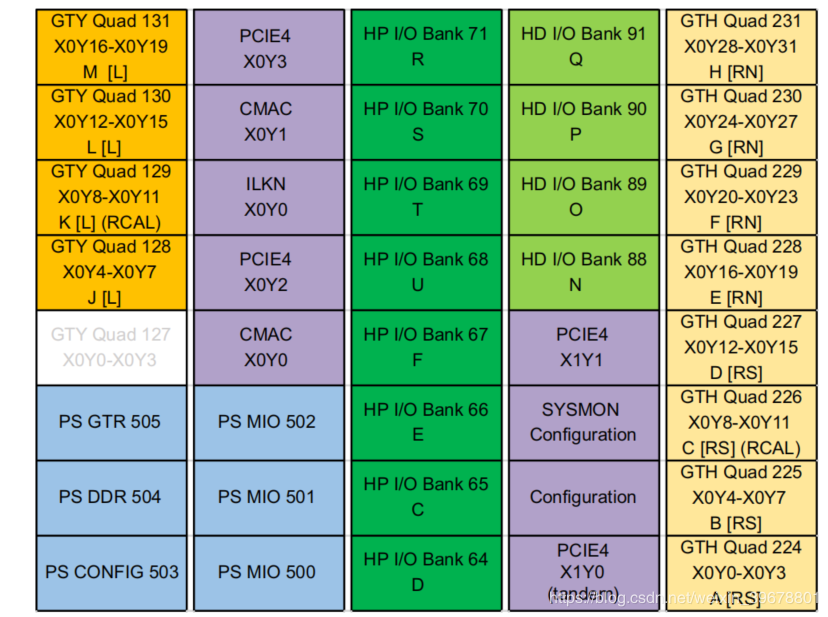

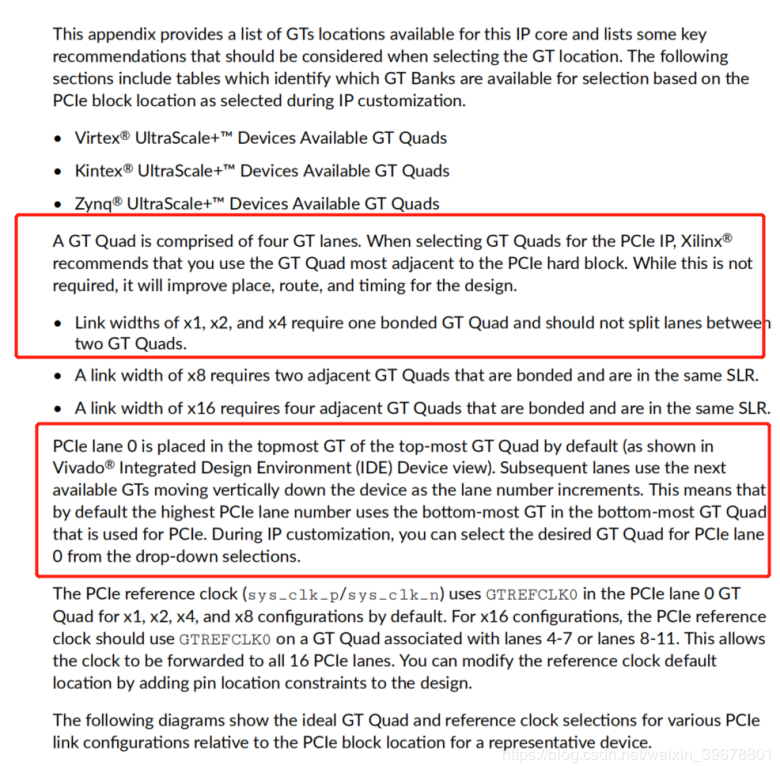

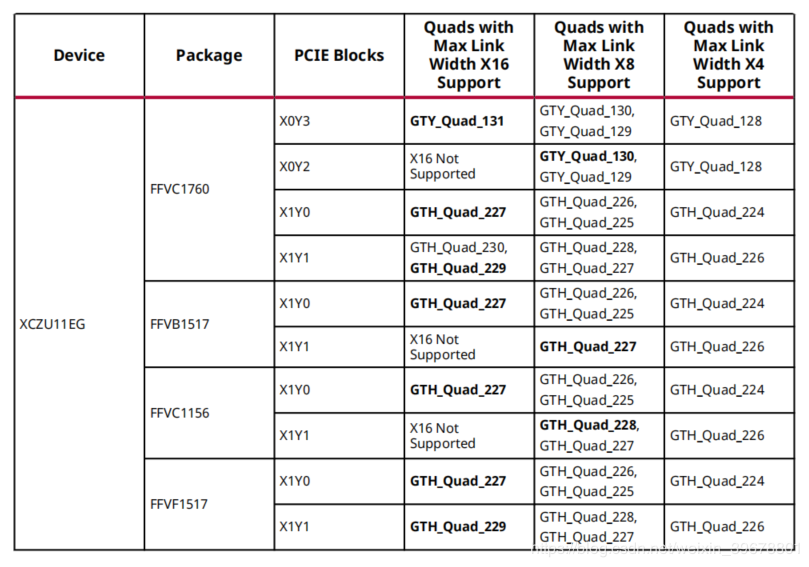

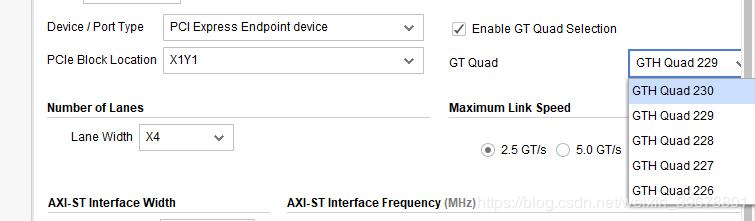

12 随着FPGA的不断发展,FPGA本身自带的PCIE硬核的数量越来越多,本文以ZU11EG为例介绍,如何进行对应的硬件引脚分配。 设计目标:ZU11EG FFVC1760封装,挂载4组NVME,接口

2021-06-27 11:20:53 5951

5951

如何进行OPCDCOM配置(四会理士电源技术有限公司招聘)-如何进行OPCDCOM配置

2021-09-18 14:23:09 11

11 而且现在的LUT都是4输入或者6输入,可以做成逻辑门的组合,跟普通的逻辑门个数肯定不会是一对一关系。今天我们来看下这个关系如果对应。

2022-11-01 09:11:29 643

643 如何进行电源设计 - 第1部分

2022-11-02 08:16:07 1

1 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密。

2023-02-16 09:26:57 11450

11450 在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发

2023-02-22 17:45:02 4537

4537 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38:53 597

597 随着 FPGA 的不断发展,FPGA本身自带的PCIE硬核的数量越来越多,本文以ZU11EG为例介绍,如何进行对应的 硬件 引脚分配。 设计目标:ZU11EG FFVC1760封装,挂载4组NVME

2023-12-14 15:45:01 194

194

电子发烧友App

电子发烧友App

评论