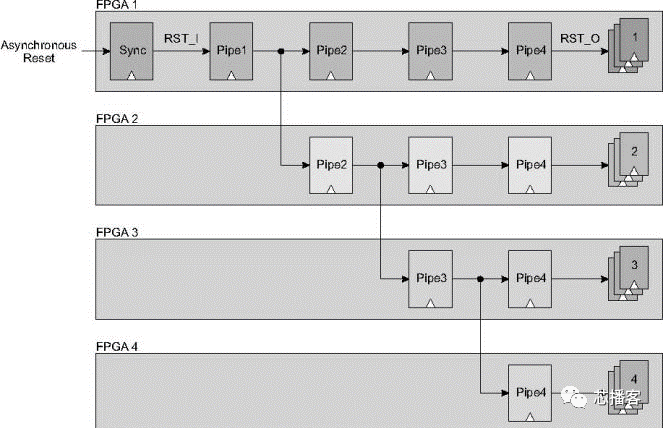

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

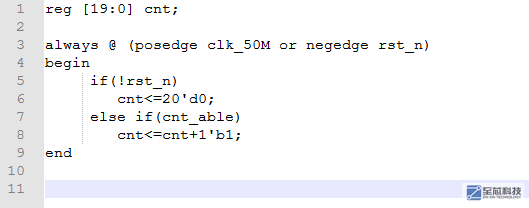

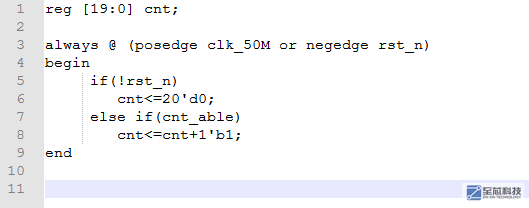

8153 可以看到以下形式的进程: 信号rst_n用来对进程中所用变量的初始化,这个复位信号是十分重要的,如果没有复位,会导致一些寄存器的初始值变得未知,如果此时FPGA就开始工作的话,极易导致错误。 那么,这个复位信号来自何处?难道我们做好的系统,每次

2018-06-18 19:24:11 19894

19894

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 1461

1461

作者:NingHeChuan Get Smart About Reset: Think Local, Not Global。 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间

2020-12-25 12:08:10 2303

2303

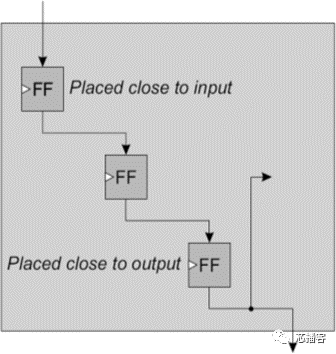

对于从FPGA外部进来的信号,我们通常采用“异步复位同步释放的策略”,具体电路如下图所示。

2023-07-20 09:04:21 1219

1219

复位信号几乎是除了时钟信号外最常用的信号了,几乎所有数字系统在上电的时候都会进行复位,这样才能保持设计者确定该系统的系统模式的状态,以便于更好的进行电子设计,并且在任意时刻,确保使用者总能对电路系统进行复位,使电路从初始的状态开始工作。

2023-07-27 09:48:30 4638

4638

没有复位信号必须在整个器件中分配。我通过具有锁定输出的内部PLL生成系统时钟。在先前的设计中,这可以用于同步复位设计。现在我担心将PLL clk输出直接用作系统时钟。我想在锁定输出上升之前,输出将不

2020-07-30 09:53:11

假设现在FPGA内部有两个高速信号完全相同,有一个很小的相位差,该如何获得一个如c信号(拓宽也行)的输出信号?直接相与或者其他逻辑操作是不是lut无法满足这么高的精度,如果不行,有其他什么办法吗?

2019-10-15 11:12:31

时获取可重复结果。在模块级应用实现属性,可令代码简单并具可扩展性,该属性可传播该模块中声明的所有信号。良好的时钟管理和时钟分配方法至关重要。尽可能减少独立主时钟数量。将时钟元件放在设计层次结构的顶层

2017-02-10 17:10:32

布线带来很大的困难,甚至走不通,或者是即便是布线走通了,也有可能由于外部的延时过大而不满足时序方面的要求。所以在管脚分配前对FPGA 工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚

2012-08-11 10:27:54

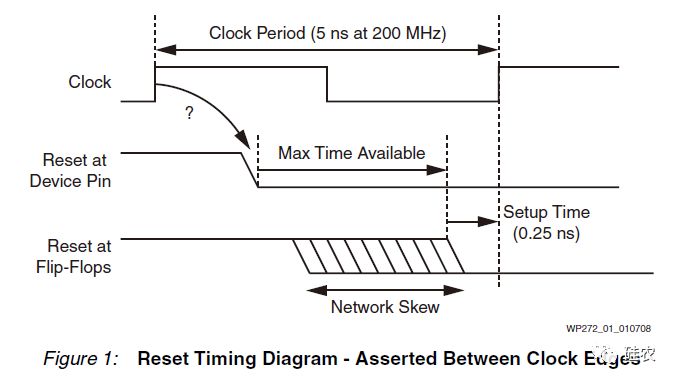

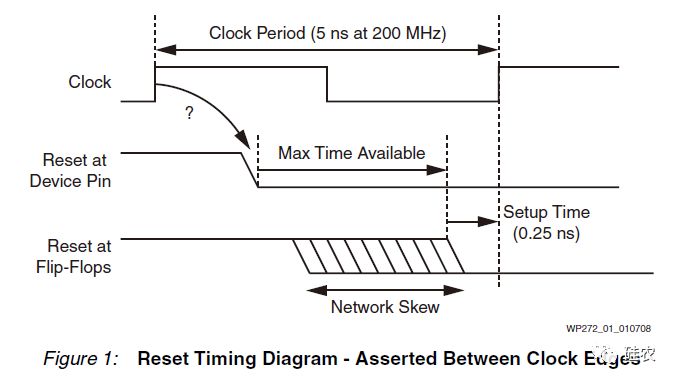

在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器

2020-10-22 11:42:16

就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们也

2019-04-12 06:35:31

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束

2019-05-17 08:00:00

采用异步双口RAM。假设我们现在有一个信号采集平台,ADC芯片提供源同步时钟60MHz,ADC芯片输出的数据在60MHz的时钟上升沿变化,而FPGA内部需要使用100MHz的时钟来处理ADC采集到

2021-03-04 09:22:51

信号上没有上拉电阻,容易受到干扰而产生毛刺,这对异步复位是相当有害的。其次,我在FPGA内部对复位的处理过于简单。 今天在网上看了一些资料,很多是关于同步和异步复位的优缺点比较。由于我在FPGA内部用

2011-11-04 14:26:17

就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们

2015-04-10 13:59:23

一个信号,要通过FPGA的不同引脚输出到不同的地方,该信号能够直接锁定到多个引脚吗?还是要在程序里定义多个信号,把该信号赋值给这多个信号,然后每个信号分别锁定一个引脚?

2017-04-05 19:27:59

方面的要求。所以在管脚分配前对 FPGA工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的 BANK 中。2、 掌握

2024-01-10 22:40:14

FPGA管脚分配需要考虑的因素 FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 11:34:24

。 FPGA 内部 BANK 的分配情况和每个 BANK 中所支持的 I/O标准。根据 FPGA中内部 BANK 的分配的情况,同时结合图 1 中信号的流向也就可以大体固定FPGA在单板中的方向,同时按照

2017-03-25 18:46:25

在处理器+FPGA的系统中,处理器可以通过FPGA来访问一些外设,需要给这些外设分配一些地址,这涉及到什么逻辑地址到物理地址的转换。不知道有木有人可以回答一下下面几个问题:1、给外设分配地址是具体

2013-08-15 21:59:39

在处理器+FPGA的系统中,处理器可以通过FPGA来访问一些外设,需要给这些外设分配一些地址,这涉及到什么逻辑地址到物理地址的转换。不知道有木有人可以回答一下下面几个问题:1、给外设分配地址是具体

2013-08-15 22:04:45

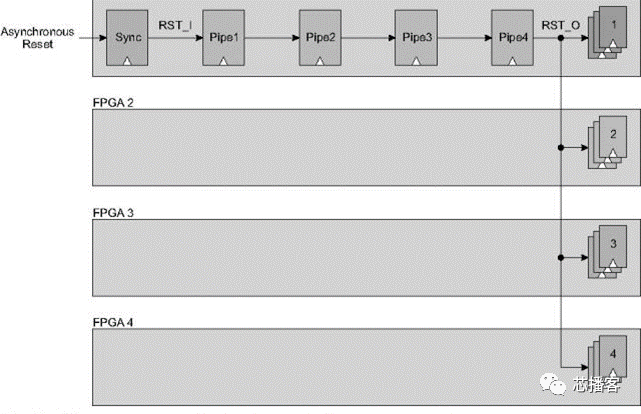

下面对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用

2021-06-30 07:00:00

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

/O信号分配 可提供最多的多功能引脚、I/O标准、端接方案和差分对的FPGA在信号分配方面也具有最复杂的设计指导原则。尽管Altera的FPGA器件没有设计指导原则(因为它实现起来比较容易),但赛灵思

2020-09-07 11:01:46

隔离•可将输入信号分为两路信号输出,分别传送到PLC和调速器•螺丝接线端子 应用:信号分配器专为准确无误地将编码器输出信号分配到多个目标单元而设计。本产品可以在TTL/RS422电平信号和HTL

2016-04-06 11:32:44

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。在FPGA中,同步信号、异步信号和亚稳态的理解PGA(Field-Programmable Gate Array),即现场

2023-02-28 16:38:14

亚稳态概述01 亚稳态发生原因在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足

2020-10-19 10:03:17

在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应如何分配?

2009-09-06 08:39:35

在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?

2021-10-26 06:59:21

在高速设计中,如何解决信号的完整性问题?

2009-09-06 08:42:10

高速信号仿真在定位接收机设计中的应用是什么?

2021-05-25 06:09:26

高速ADDA模块开箱,FPGA专用,高速信号输出,数模信号转换,8Bit高速低功耗DA转换,DA速率高达125MSPS,10BitAD转换,AD速率35MSPS,模块含SPI串口屏幕显示、PMOD扩展口,同时支持高速ADDA转换,可搭配盘古22K、盘古50K开发板使用

2024-03-13 18:25:46

`高速PCB中的信号回流及跨分割这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。 IC1为信号输出端,IC2为信号输入端(为简化PCB模型

2013-10-24 11:12:40

变化速率)、dV(干扰源的摆幅)和R(干扰源负载)都是指干扰源的参数(如果是容性负载的话,dI/dt是与T10%-90%的平方成反比的。)。从式中可以看出,低速的信号未必比高速信号的串扰小。也就是我们说

2018-11-22 15:58:42

高速PCB中的地回流和电源回流以及跨分割问题分析

2021-04-25 07:47:31

间序列中,专用的全局复位GSR将复位FPGA中的所有寄存器。众所周知,GSR是不可见的,不能在用户的VHDL代码中使用。那么我们如何在VHDL代码中分配寄存器信号的起始值。我的意思是在正常情况下我们使用这样的重置信号:过程(clk,rst)开始 如果rst ='1'那么 regs

2019-05-22 11:40:55

本帖最后由 mr.pengyongche 于 2013-4-30 03:09 编辑

DSP+FPGA在高速高精运动控制器中的应用 摘要:数字信号处理器具有高效的数值运算能

2012-12-28 11:20:34

在 PCB 设计过程中,由于平面的分割,可能会导致信号参考平面不连续,对于低低频信号,可能没什么关系,而在高频数字系统中,高频信号以参考平面作返回路径,即回流路径,如果参考ᒣ面不连续,信号跨分割

2016-10-09 13:10:37

PCB设计中跨分割的处理高速信号布线技巧

2021-02-19 06:27:15

、摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总。 二、管脚分配方法FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按钮

2018-07-03 12:56:11

它们全部移除。我们只是想确保通过这样做,我们没有采用基于Spartan-6的设计的重要电路。此上电复位电路的目的是在它监控的两个电源中的任何一个时提供复位信号:+ 3.3V和+ 1.2V或者FPGA本身

2019-04-18 10:15:45

同步单元的起始状态或者将要返回的状态是一个已知状态(罗辑‘1’或者‘0’)就显得非常重要。在程序中,往往都在端口定义中使用同一个rst_n信号,通常的同步电路通常是由两种复位方式来进行电路的复位,即

2015-06-07 20:39:43

延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们也需要注意以下几个要点:● 尽可能

2016-07-25 15:19:04

引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA的时钟和复位

2016-08-08 17:31:40

to”,即多个信号分配给这个引脚?如图7.7所示,pin assignment中并没有多个信号分配给Pin_F16这个引脚,只有adv7123_sync_n分配给了它。 图7.7 引脚分配再来看看如图

2016-12-05 18:27:37

PlanAead引脚分配这个例程的顶层源码里有3个接口,即:input ext_clk_25m, //外部输入25MHz时钟信号input ext_rst_n,//外部输入复位信号,低电平有效output reg

2018-02-27 21:50:07

本期讲解的是PCB设计中处理关键信号的注意事项。一、关键信号的识别关键信号通常包括以下信号:时钟信号(*CLK*),复位信号(*rest*,*rst*), JTAG信号(*TCK*)二、处理关键信号

2017-11-01 17:06:26

大家好,我刚开始学习FPGA并试图弄清楚哪些FPGA引脚可以分配我的数据信号。我正在使用FPGA Spartan 6封装TQG114器件LX9。查看产品规格,有102个可用的用户I / O.这是

2019-04-23 06:55:23

FPGA 在单板中的方向,同时按照就近的原则将相关的信号分配到相关的 BANK 中,这样的方法可以完成一般信号的分配。3、 掌握所选 FPGA 每个 BANK 所支持的 I/O 标准。从图 2 中可以看出

2015-01-06 17:38:22

的输入输出接口设计就显得尤为重要。1 高速采集系统介绍 数据采集系统原理框图如图1所示,输入的中频信号经A/D采样电路采样后,转换成LVDS信号送入FPGA中,或通过FPGA的端口RocketIO从高速接口

2018-12-18 10:22:18

在本文中,我将首先讨论两种开发 RFID 应用程序的方法:传统方法和 RFID Web服务。然后,我将 讨论把 RFID Web服务集成到多个 SOA 中的 EAI 应用程序将如何提高带 RFID

2019-07-17 06:31:53

芯片输出的数据在 60MHz 的时钟上升沿变化,而 FPGA 内部需要使用 100MHz 的时钟来处理 ADC 采集到的数据(多 bit)。在这种类似的场景中,我们便可以使用异步双口 RAM 来做跨

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

2019-10-16 07:11:33

由于 ES_LPC5411x 中的勘误表 USB.1,需要 TN00031 中的解决方法才能跨多个 USB 集线器实现无晶体 USB。我正在研究从单个设备支持多个串行端口。但是,SDK 中的示例

2023-05-06 07:03:28

请帮帮我。我无法在FPGA中创建可用信号。(引脚FPGA中的网关输出)显示错误。焊盘位置的数量必须与驱动该网关输出的信号的位数相匹配。格式必须指定为单元格数组,例如{'MSB',...,'LSB

2019-09-10 12:44:58

问题是:如果相同的VCCO电压,不同的IO级标准信号可以在xilinx spartan6-45t FPGA的同一个BANK中一起分配?例如LVDS 3.3 V,TMDS 3.3 V

2019-10-23 10:03:17

这三类约束文件分开写在三个xdc/sdc文件中。 第一类是物理约束,它主要对设计顶层的输入输出引脚的分配约束、电平标准的约束,如下图所示:在quartus环境下,对pcie_rstn

2022-11-15 14:47:59

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-04-24 16:05:19 1274

1274

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-05-01 11:14:27 1655

1655

VGA分配器将来自一个信号源的视频信号分配成两个或多个信号。高分辨率视频分配放大器的一个常见应用就是,在接收来自一个计算机视频端口的信号后将其放大,并在保持原有信号质量的情况下将其分配到两个或多个高分辨率数据显示设备

2011-02-21 10:55:32 9634

9634

现在的FPGA向引脚分配信号的任务曾经很简单,现在也变得相当繁复。

2016-07-27 20:24:00 6740

6740 在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 876

876

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2017-05-18 10:51:54 29124

29124

在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 1989

1989 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

2018-08-07 09:17:18 10969

10969 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 10154

10154 FPGA设计中,层次结构设计和复位策略影响着FPGA的时序。在高速设计时,合理的层次结构设计与正确的复位策略可以优化时序,提高运行频率。

2019-02-15 15:15:53 849

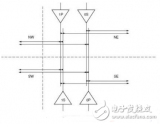

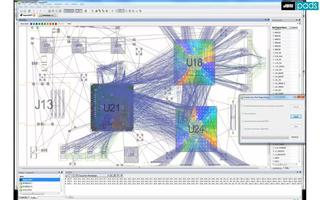

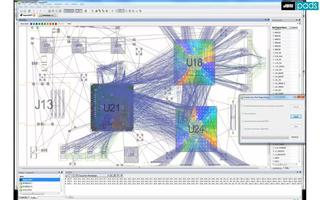

849 在遵循管脚特定的规则和约束的同时,可以在 PCB 上的多个 FPGA 之间自动优化信号管脚分配。减少布线层数,最大限度地减少 PCB 上的交叉数量并缩短总体走线长度,以及减少信号完整性问题,从而提高完成率并缩短 FPGA 的布线时间。

2019-05-14 06:23:00 3276

3276

信号销任务之间可以自动优化PCB上的多个fpga同时尊重pin-specific规则和约束。减少路由层,减少跨界车和整体跟踪PCB上的长度,并减少信号完整性问题较高的毕业率和更短的FPGA路线时间。

2019-10-14 07:06:00 2849

2849 复位信号设计的原则是尽量不包含不需要的复位信号,如果需要,考虑使用局部复位和同步复位。

2019-10-27 10:09:53 1735

1735

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 2456

2456

最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 323

323 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 25

25 在这些情况下,复位信号的变化与FGPA芯片内部信号相比看起来是及其缓慢的,例如,复位按钮产生的复位信号的周期至少是在毫秒级别的,而我们FPGA内部信号往往是纳米或者微秒级别的。

2022-05-06 10:48:45 2462

2462 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 1585

1585 ANSI EIA/TIA-644 低压差分信号 (LVDS) 标准比更传统的 ECL、PECL 和 CML 标准提供更低的功率和更低的噪声发射,用于高速信号分配。本应用笔记比较了这些通信标准的一些特性,并讨论了LVDS标准的一些优点。

2023-03-29 11:05:07 662

662

本应用笔记讨论了EIA/TIA-644低压差分信号(LVDS)标准在3G移动通信中的应用。LVDS具有低功耗和低辐射特性,非常适合WCDMA、EDGE和cdma2000®基站中的高速时钟和信号分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中继器和MAX9152交叉点开关。

2023-03-29 11:14:33 750

750

FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 806

806 。 下面将讨论FPGA/CPLD的复位电路设计。 2、分类及不同复位设计的影响 根据电路设计,复位可分为异步复位和同步复位。 对于异步复位,电路对复位信号是电平敏感的,如果复位信号受到干扰,如出现短暂的脉冲跳变,电路就会部分或全部被

2023-04-06 16:45:02 782

782 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38:53 597

597 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 3347

3347

jtag端口的复位信号jtag_trst用于复位TAP状态机模块,该复位信号可选。

2023-05-25 15:09:43 622

622

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 2110

2110

对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。

2023-06-21 10:39:25 651

651

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应如何分配? 在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应该经过合理分配。接地

2023-11-24 14:38:21 635

635

电子发烧友App

电子发烧友App

评论