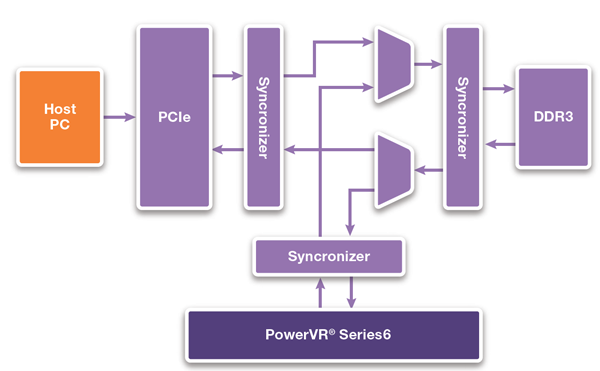

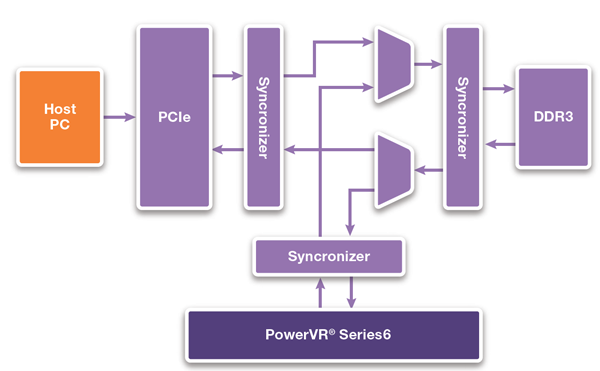

Synopsys所做的第一步是启动一个概念验证项目。这个项目为Imagination的PowerVR Series6 GPU展示了基于FPGA的原型设计。

2015-06-24 09:47:00 1619

1619

什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 1735

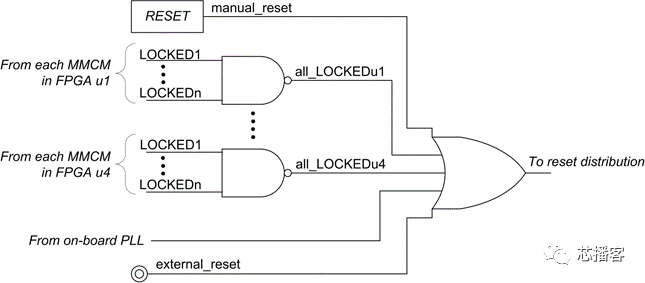

1735 Tape Out并回片后都可以进行驱动和应用的开发。目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。本文我就将与大家探讨FPGA原型验证的几个经典挑战性场景,(具体应对的办法,请戳原文。)容量限制和性能要求

2020-08-21 05:00:12

OpenFlow。研究人员可以在全国范围内在国家级测试平台上,比如美国的GENI和欧盟的FIRE上试验新型网络架构。 研究人员还越来越多地将NetFPGA开发板用于新理念的硬件原型设计,诸如新的转发模式、调度

2011-07-19 15:51:05

[attach]***[/attach]FPGA中双向端口IO的研究针对现 场 可 编 程 门 阵 列 芯 片 的 特 点 研 究 中 双 向 端 口 的 设 计同 时 给出 仿真初始化双向端口 的方法 采用这种双向端口的设计方法 选用 的 芯片设计一个多通道图像信号处理系统

2012-08-12 12:00:13

上面介绍的是整个 FPGA 固件系统的实现方法,为了验证设计的正确性,还需要编写一个测试平台对整个系统进行仿真。由于实际情况下 FPGA 是和 PDIUSBD12 进行通信,所以在测试平台中需要虚拟

2018-11-28 15:22:56

各位专家好:

关于多片C6678的同步调试问题想咨询下:

我打算做两个板子,每个板子上集成两片C6678的芯片,板间通信打算用光传输,现在想咨询的问题是在用CCS进行调试的时候,这个能不能实现同步调试,比如在某个时间一起停下来,去看看各自寄存器或者变量的值。谢谢。

2018-06-21 02:37:42

调试过程中发现:多片AD9361同步后,一段时间内相位恒定,散热风扇撤掉或者一二十分钟后会有片子相位翻转180°,片子位号随机,请问一下这个是片子本身特性还是散热影响(若散热影响,麻烦告知影响机理),又或者代码哪里未设置对?期待您的回答

2023-12-07 07:36:42

Hi,ADI我们现在在做一个5.8GHz的多通道接收机系统,需要多片AD9361之间载波相位同步我在AD9361的userguide UG570 page19,发现ad9361的external LO只能支持70MHz至4GHz?我的理解是否正确如果我希望使用5.8GHz的本振同步,有方法实现吗?

2018-10-08 10:51:27

多片AD9680如何同步?需要注意什么问题?

2023-12-08 08:02:57

用FPGA控制两片AD9739(以下简称A和B),其中A的SYNC_OUT接到了B的SYNC_IN,而A的SYNC_IN和B的SYNC_OUT接到了FPGA中。

现在配置0x10寄存器,采用无同步

2023-11-27 14:45:26

用4片AD9910,各种模式输出单片的调试都没有问题。现在要调多片同步,按照数据手册上的要求进行各个寄存器的配置,25M参考时钟输入,内部用锁相环陪频到1G,就是多片同步不了,12脚一直为高,检测

2018-11-20 09:11:33

用4片AD9910,各种模式输出单片的调试都没有问题。

现在要调多片同步,按照数据手册上的要求进行各个寄存器的配置,25M参考时钟输入,内部用锁相环陪频到1G,就是多片同步不了,12脚一直为高,检测不到有效地SYNC_IN信号,不知道原因,请技术支持帮助

2023-11-27 06:00:09

笔者在多通道无源雷达信号处理机的设计中,采用了DSP芯片TMS320VC5409控制4片DDC芯片HSP50214B的接口电路,研究了同步控制多片HSP50214B等关键技术。DDC芯片

2019-06-04 05:00:17

官方应用笔记an605介绍了如何同步多片DDS9854, 上图是在倍频至300M时的需满足的时序图,要求EXT I/O UPDATE CLK的上升沿发生在REFCLK上升沿的前0.3ns和后

2018-09-29 15:36:31

国内虚拟研究平台多基于单电机设计,而实际工业中多电机配合工作更为常见,如机器人、3D打印机等。多电机同步控制在工业自动化生产系统中广泛存在,但目前基于FPGA纳秒级实时仿真平台多为单电机设计,进行多

2024-03-19 16:13:55

实现通用的原型开发环境。功能包括:开发平台展示了跨转换器IC和跨板的多通道同步。在客户面前先在评估板环境中验证多通道性能,而不是仅仅为了同时测试多个通道而致力于生产设计。一定程度的集成和功能性,可以

2020-08-21 14:24:29

大家好,JESD204B协议已让单板多片AD采样同步变得更容易了,想请教下,如何做到多板间的AD采样同步啊,有没有什么好的思路啊。

还有AD6688的采样时钟频率范围为2.5G~3.1G,芯片支持

2023-12-12 08:27:58

最近在调AD9910使两片同步,可是无论怎么配置,同步SYNC_OUT总是没有输出,两片均没有。主要寄存器设置如下:reg [39:0] cfr1=40'h0000806200;reg [39:0

2018-09-18 11:18:15

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

MPS2和MPS2+FPGA原型板是ARM Cortex-M评估和开发的开发平台。

MPS2和MPS2+FPGA原型板提供以下功能:

Altera Cyclone FPGA和主板上电和配置MPS2

2023-08-18 07:25:28

十、Kubernetes平台中日志收集

2019-11-04 09:19:30

本文探讨ADI公司新推出且拥有广泛市场的LIDAR原型制作平台,以及它如何通过提供完整的硬件和软件解决方案,使得用户能够建立其算法和自定义硬件解决方案的原型,从而帮助客户缩短产品开发时间;详细介绍

2021-06-17 09:08:54

分割到24颗FPGA内。 此外, 实时运行功能还可以通过网络对多块基于FPGA的原型平台进行控制和监测。我非常高兴我们可以向客户提供这种新的能力。”

2019-07-02 06:23:44

目前,无线传感器网络时间同步技术的研究重点已经从单跳网络发展到多跳网络。现有的多跳时间同步算法充分体现了同步功耗和同步精度以及同步周期间的折衷,本文着重解决的问题就是在不显著增加同步功耗的前提下扩展同步周期,本文的硬件平台为Silicon Labs公司的Si1000无线MCU芯片。

2020-04-24 08:29:05

项目里用到fpga和单片机,采样率24bit100kHz。使用fpga一个是用来GPS PPS时钟同步,一个是多通道A/D数据同步采集(起始沿和clk时钟同步),采集后存到RAM里,采满后通知单

2018-11-06 09:35:33

`1月5日-8日拉斯维加斯消费电子展(CES)上,地平线机器人(以下简称“地平线”)将与英特尔联合展示一款基于单目摄像头和FPGA的ADAS产品原型系统。车辆检测结果该原型由英特尔和地平线联合开发

2017-01-06 18:09:34

测试平台,采用系统级指标分析HDL实现 方案;通过FPGA在环仿真加速验证(图1)。为什么在FPGA上建立原型?在FPGA上建立算法原型可以增强工程师的信心,使他们相信自己的算法在实际环境中的表现能够

2020-05-04 07:00:00

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

和体系建立智能家庭网络整体结构。给出了MAIHN模型的各个组成部分,对模型中各种Agent的功能设计与实现模型进行了分析,研究了MAIHN模型中的多Agent协作与通信策略,并设计了系统的实验原型。关 键 词 智能家庭网络; 分布式; 多Agent系统; 多Agent通信[hide][/hide]

2009-06-14 00:22:04

斯坦福大学与赛灵思研究实验室(Xilinx Research Labs)联手开发专门面向研究社群的第二代高速网络设计平台 NetFPGA-10G。该新型平台采用最先进的技术,能够帮助研究人员迅速构建

2019-08-27 08:30:57

芯片设计和验证工程师通常要为在硅片上实现的每一行RTL代码写出多达10行测试平台代码。验证任务在设计周期内可能会占用50%或更多的时间。尽管如此辛苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以发现系统级错误,芯片设计人员正利用FPGA来加速算法创建和原型设计。

2019-09-18 07:50:02

Memtool 是一个有用的调试工具,可以读/写一些 i.MX 寄存器。Linux 默认支持,Android 不支持。

本文介绍如何将 memtool 集成到 i.MX8MM Android 12 平台中,这在其他 i.MX 新安卓平台中也类似。

2023-05-16 06:56:08

方案说是以后可能要用到调试多片DSP,我想知道如何调试多片DSP? ?

2019-07-05 04:55:36

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。

2021-05-06 07:20:48

的设计和验证的复杂性需求。随着原型技术在设计分割以及多 FPGA 联 合调试领域的进步,基于FPGA 的原型系统不仅可以满足百万门级的设计需求,还可以实现设计规模高达15 亿门。基 于FPGA

2018-08-07 09:41:23

550MHz的兆位RAM以及数百个25×18乘法器/DSP功能。 这些可能还包含多个硬和/或软处理器内核和相关外围器件的设备可以用作ASIC和片上系统(SoC)元器件的功能强大的原型平台。 新工

2020-07-07 09:08:34

有什么办法可以获取rk3288平台中的serial number?

2022-03-10 06:18:52

多片fpga组成jtag链的时候如何加载?

2023-08-11 09:10:26

求大神详细介绍一下基于FPGA的电子稳像平台的研究

2021-05-07 06:02:47

直线电机在平台中有哪些应用?

2021-10-29 06:39:19

评估新类别的元件。SDP连接至FPGA评估与原型制作平台,可以轻松创建并演示采用ADI元件通信的定制FPGA嵌入式设计。用户可以迅速建立定制评估与原型制作系统,还可以重复使用各种平台元件,演示各种丰富

2018-10-24 10:24:31

您好: 我想问下多片AD9361同步精度可以做到多高?有没有大神做过相关的?

2019-01-14 14:30:29

500MSPS的采样,但是没有提到任何多片同步的机制?有没有具体的实现多片ADCs(8路数据,最少4片)的同步实现操作?

2019-01-11 08:06:29

请教一下论坛里的诸位大牛; 我需要用多片AD9361接收5.8GHz的射频信号,如何保证多片AD9361的相位同步?因为AD9361的external LO只能支持70MHz至4GHz,不能满足

2019-02-15 14:55:35

如何将多片AD9361芯片进行相位同步,技术文档有说通过sync管脚进行MCS同步,但是仅仅只针对数据时钟完成同步。个人理解数据相位主要由RF混频处理以及后续数字处理决定,通过sync管教能够完成

2018-12-25 11:42:25

如何实现多片AD9361接收同步?每次上电周期的相位补偿是否可以通过软件自动补偿?

2019-02-18 07:58:53

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

2019-06-18 07:43:00

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

分析了MobiLink数据库同步技术的原理,研究了通过MobiLink实现移动数据库和统一数据库同步的方法,针对Windows CE平台中的MobiLink客户端不能有效传递参数和输入不便的问题,提出了一

2010-10-21 16:30:06 0

0 摘要: 分析了传统电子稳像平台的缺陷,研究并设计了基于FPGA的专用平台。针对该平台研制过程中所涉及的一些关键问题进行了详尽的分析与探讨,给出了可行的

2009-06-20 14:28:14 333

333

富士通微电子正式采用亚科鸿禹FPGA原型验证平台

富士通微电子(上海)有限公司近日赴北京亚科鸿禹电子有限公司,圆满完成了对StarFire-V530原型验证板的测试验收工作。

2010-02-24 08:50:34 740

740 《 FPGA的原型开发方法手册》(FPMM),这是一本介绍如何使用 FPGA 作为平台进行片上系统(SoC)开发的实用指南。FPMM 收录了众多公司的设计团队在设计和验证方面的宝贵经验,

2011-03-14 09:06:50 734

734 自升式海洋平台多桩腿同步控制的研究_齐继阳

2017-01-16 14:04:30 0

0 石油平台中控系统操作记录的实现_武岳

2017-02-07 15:11:11 0

0 如今,设计人员使用两种相对独立的方法进行 SoC 原型验证:以事务级模型为基础的虚拟原型验证和基于 FPGA 的原型验证。 虚拟原型验证执行快速的 TLM,并可提供更高效的调试和分析方案,非常适合

2017-02-08 14:32:11 293

293 完整原型设计平台便是当之无愧的大方案,该平台由现有的一些设备组成: Prodigy逻辑模块:基于FPGA的原型开发板。如,基于XilinxVirtex-72000T 3D FPGAs的TAI 逻辑模块

2017-02-09 03:49:04 437

437 效率。Protium S1与Cadence® Palladium® Z1企业级仿真平台前端一致,初始设计启动速度较传统FPGA原型平台提升80%。

2017-03-02 11:13:11 2744

2744 基于FPGA的MSK同步调谐研究_金国庆

2017-03-18 08:00:00 0

0 在校园信息化平台中研究与实现MVC2x框架_姚炼

2017-03-20 09:24:02 1

1 门阵列(FPGA)做为安谋国际核心测试芯片,进而建构SoC原型制作平台。 验证SoC设计 FPGA原型最稳当 FPGA原型制作是在FPGA上实作SoC或特定应用集成电路(ASIC)设计的方法,并进行硬件验证和早期软件开发。

2018-05-11 09:07:00 2405

2405

原型设计允许硬件验证和软件工作更早地开始,在第一个硅之前,有效地流水线设计过程。现代可重新编程的FPGA是灵活多样的计算和原型平台-易于重新配置开发系统以测试总体设计中的连续过程,这为开发人员提供了一个主要优势,并在承诺生产成本高

2019-06-25 08:00:00 2

2 FACE-VUP:大规模FPGA原型验证平台 FACE-VUP大规模FPGA原型验证平台是FACE系列的最新产品。FACE-VUP同时搭载16nm工艺的Virtex UltraScale+系列主器件

2020-05-19 10:50:05 2521

2521 Corundum是一个基于FPGA的开源原型平台,用于高达100Gbps及更高的网络接口开发。Corundum平台包括一些用于实现实时,高线速操作的核心功能,包括:高性能数据路径,10G/ 25G

2022-11-03 10:02:14 788

788 教程 7:DA1458x 原型启动指南

2023-03-16 19:00:43 0

0 FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 928

928 FPGA原型平台的性能估计与应用过程的资源利用率以及FPGA性能参数密切相关,甚至FPGA的制程也是一个因素。

2023-04-04 09:49:04 1475

1475 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:03 628

628 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:37 443

443 当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-10 10:15:16 187

187 当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-23 15:31:10 319

319 教程 7:DA1458x 原型启动指南

2023-07-06 19:46:05 0

0 所有形式的原型都为验证硬件设计和验证软件提供了强大的方法,模型或多或少地模仿了目标环境。基于FPGA的原型设计在项目的关键后期阶段尤其有益。用户有几个原型设计选项根据他们的主要需求,可以选择各种基于软件和硬件的技术来原型他们的设计。

2023-10-11 12:39:41 275

275

FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 proFPGA是mentor的FPGA原型验证平台,当然mentor被西门子收购之后,现在叫西门子EDA。

2024-01-22 09:21:01 546

546

FPGA原型验证流程是确保FPGA(现场可编程门阵列)设计正确性和功能性的关键步骤。它涵盖了从设计实现到功能验证的整个过程,是FPGA开发流程中不可或缺的一环。

2024-03-15 15:05:33 97

97 FPGA原型验证平台与硬件仿真器在芯片设计和验证过程中各自发挥着独特的作用,它们之间存在明显的区别。

2024-03-15 15:07:03 131

131

电子发烧友App

电子发烧友App

评论