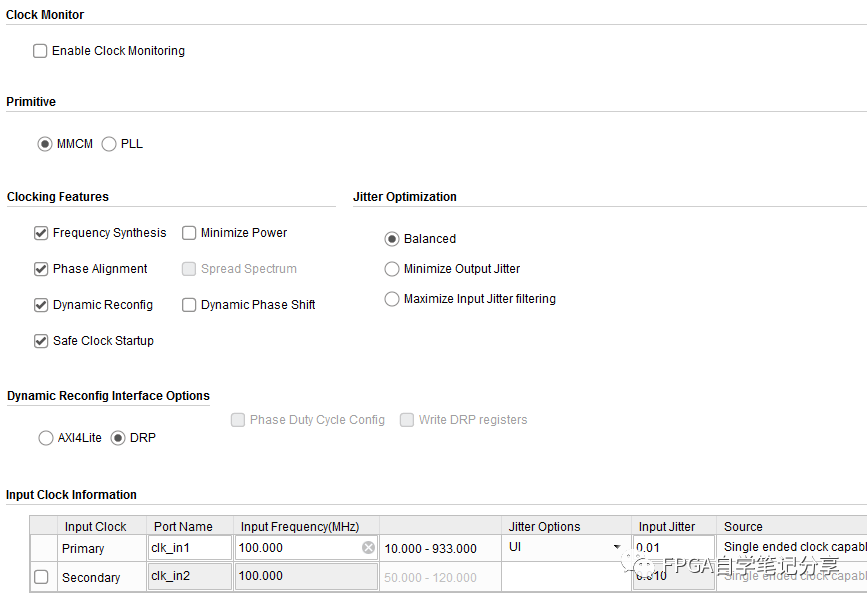

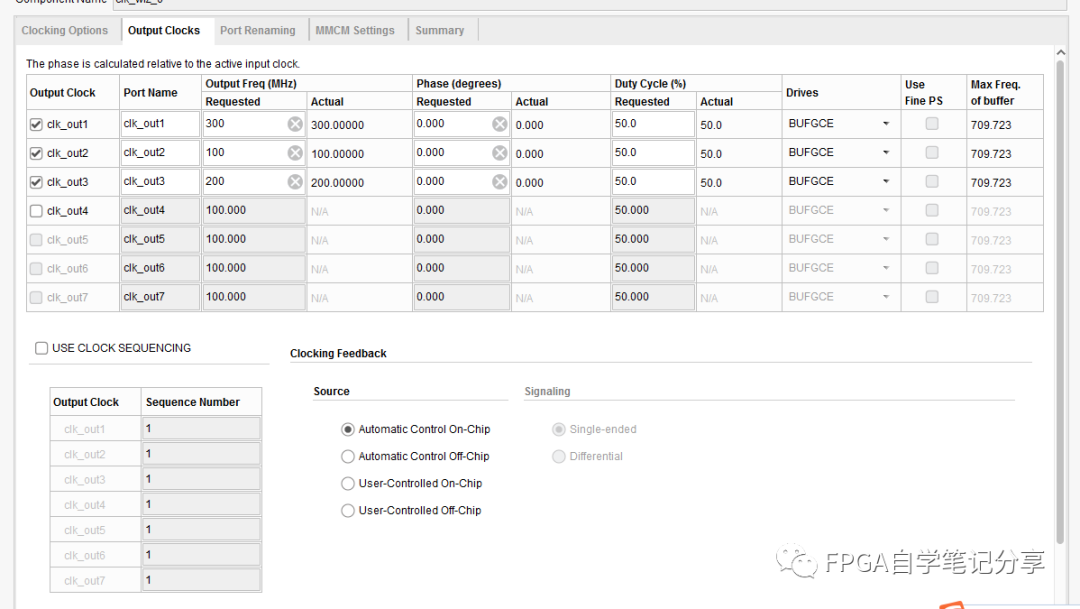

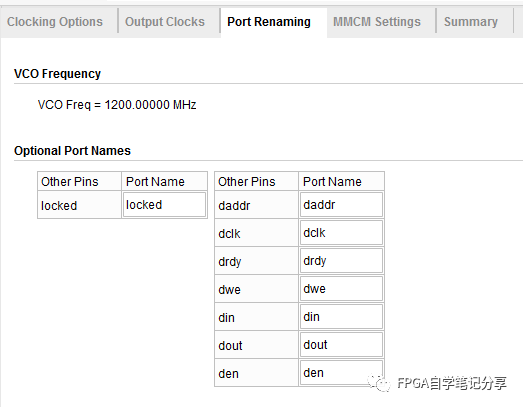

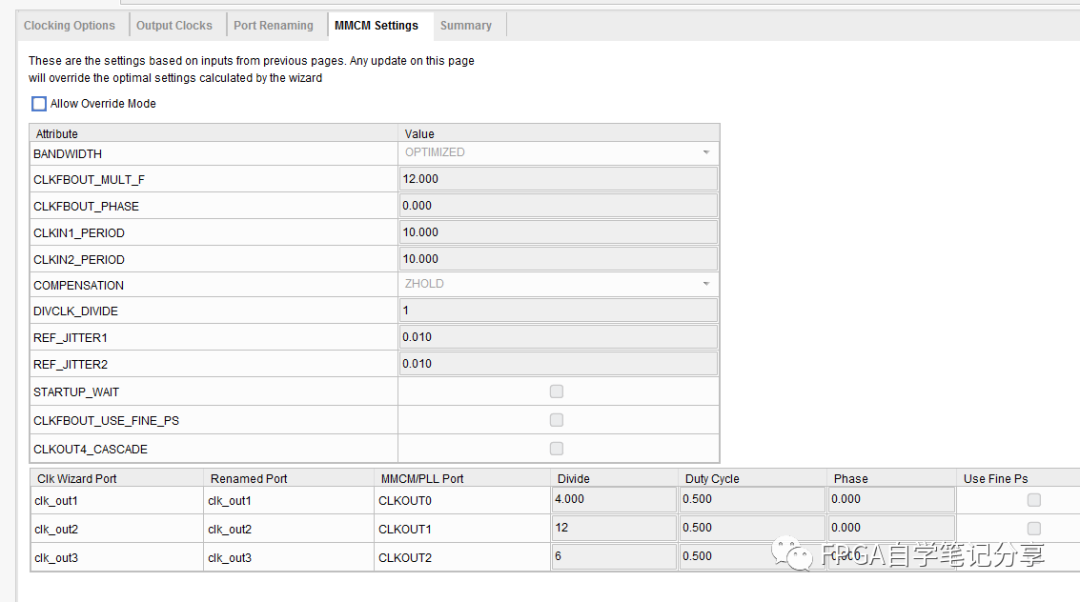

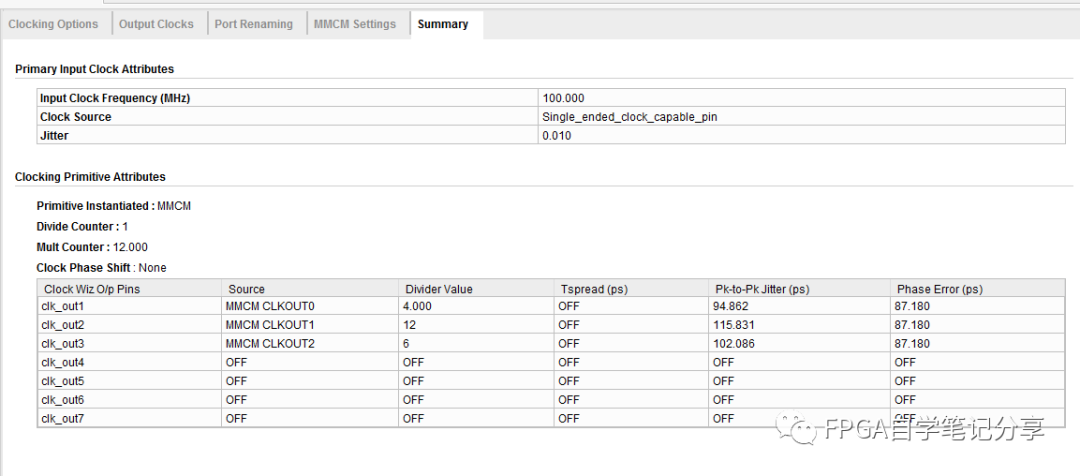

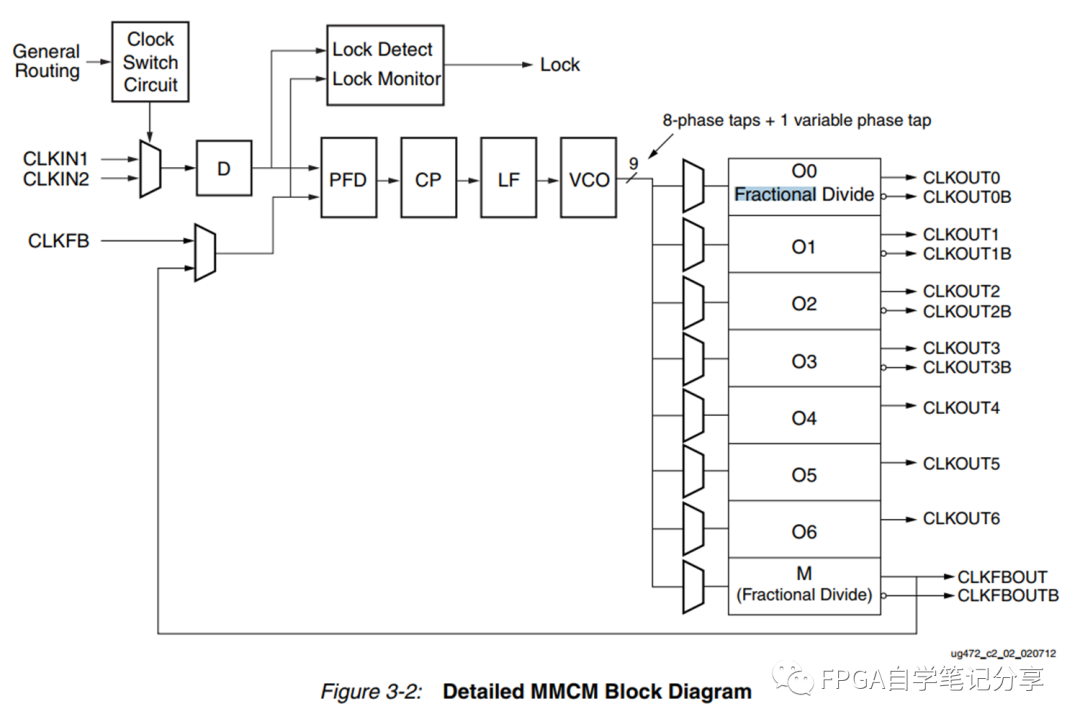

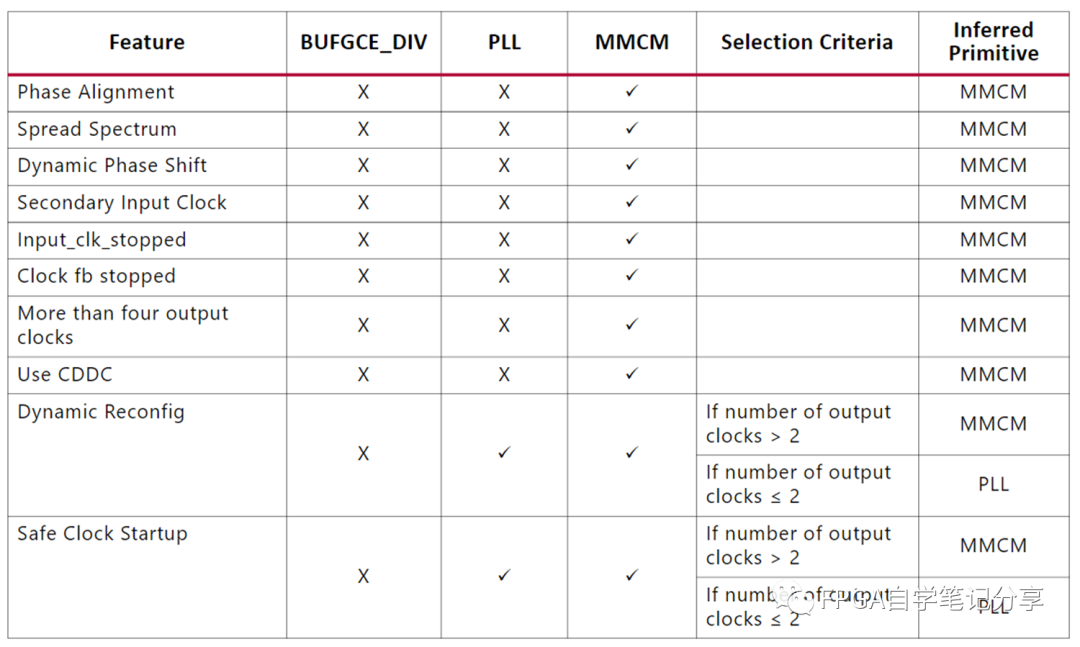

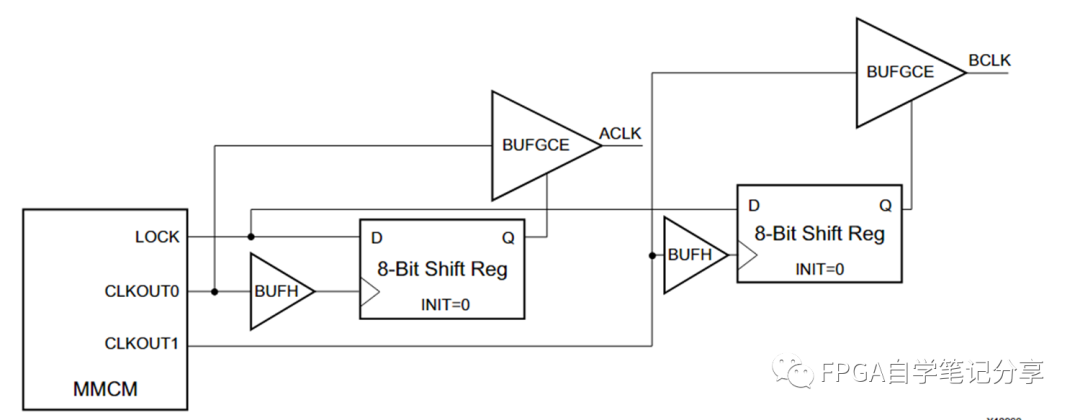

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2019-04-08 09:34:43

FPGA系统设计原则和技巧之:FPGA系统设计的3种常用IP模块.pdf(1012.86 KB)

2019-04-24 13:33:04

不多说,上货。IP CORE 之 PLL- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。Xilinx

2023-04-06 16:04:21

Xilinx FPGA入门连载24:PLL实例之基本配置 1 工程移植可以复制上一个实例sp6ex7的整个工程文件夹,更名为sp6ex8。然后在ISE中打开这个新的工程。 2 新建IP核文件

2019-01-21 21:33:40

,如图所示,选择IP核类型为“FPGA Features andDesign à Clocking à Clocking Wizard”。点击“Next”继续。如图所示,前面的配置信息在“New

2015-11-16 12:09:56

`Xilinx FPGA入门连载34:超声波测距终极结果显示之除法器IP解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1概述在本例

2015-12-09 12:22:00

`Xilinx FPGA入门连载35:超声波测距终极结果显示之乘法器IP解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 概述在

2015-12-07 13:06:00

`Xilinx FPGA入门连载40:SRAM读写测试之设计概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能简介如图所示,本

2015-12-18 12:57:01

`Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2016-01-08 13:12:44

`Xilinx FPGA入门连载48:FPGA片内RAM实例之RAM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1新建源文件打开

2016-01-22 13:39:24

Xilinx FPGA入门连载50:FPGA片内RAM实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-01-27 13:10:35

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打开

2016-02-29 13:35:55

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打开

2016-02-29 13:35:55

`Xilinx FPGA入门连载54:FPGA 片内FIFO实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-04 13:13:12

`Xilinx FPGA入门连载56:FPGA片内异步FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1新建

2016-03-09 10:49:56

`Xilinx FPGA入门连载58:FPGA 片内异步FIFO实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-16 12:13:05

`Xilinx FPGA入门连载5:ISE与Modelsim联合仿真之库编译特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1 操作系统

2015-09-14 12:37:44

`Xilinx FPGA入门连载73:波形发生器之IP核CORDIC(正弦波)配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-24 18:57:15

`Xilinx FPGA入门连载74:波形发生器之IP核CORDIC(正弦波)功能仿真特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-25 08:33:11

Xilinx FPGA配置clocking时钟动态相位输出

2019-08-05 11:35:39

显示之乘法器IP解析Lesson36 特权Xilinx FPGA SF-SP6入门指南 -- 超声波测距终极结果显示之除法器IP解析Lesson37 特权Xilinx FPGA SF-SP6入门指南

2015-07-22 11:49:20

Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2019-01-09 16:02:21

《FPGACPLD设计工具──Xilinx+ISE使用详解》

2018-01-12 15:04:43

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

Xilinx_FPGA下载烧写教程(超详细)Step by step 学习下载配置 Xilinx 之 FPGA配合 Mars-EDA 的 Spartan2 核心板,用图文方式向大家详细讲述如何下载配置 Xilinx的 FPGA。

2017-10-31 12:16:03

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

Altera系列FPGA芯片IP核详解

2020-06-28 13:51:01

在Vivado 2016.1和Kintex-7 FPGA中,我可以使用名为“Clocking Wizard v5.3”的IP来配置为我的项目输出系统时钟的MMCM。自定义此IP后,将自动为IP生成

2019-08-02 09:54:40

Stevens关于TCP/IP的经典著作(共3卷)的中译本。其中的卷3:《TCP/IP详解 卷3:TCP事务协议、HTTP、NNTP、UNIX域协议》。

2009-08-08 17:30:49

本帖最后由 lee_st 于 2017-11-2 15:01 编辑

《FPGACPLD设计工具──Xilinx+ISE使用详解》第 1 章 ISE 系统简介

2017-11-02 10:02:32

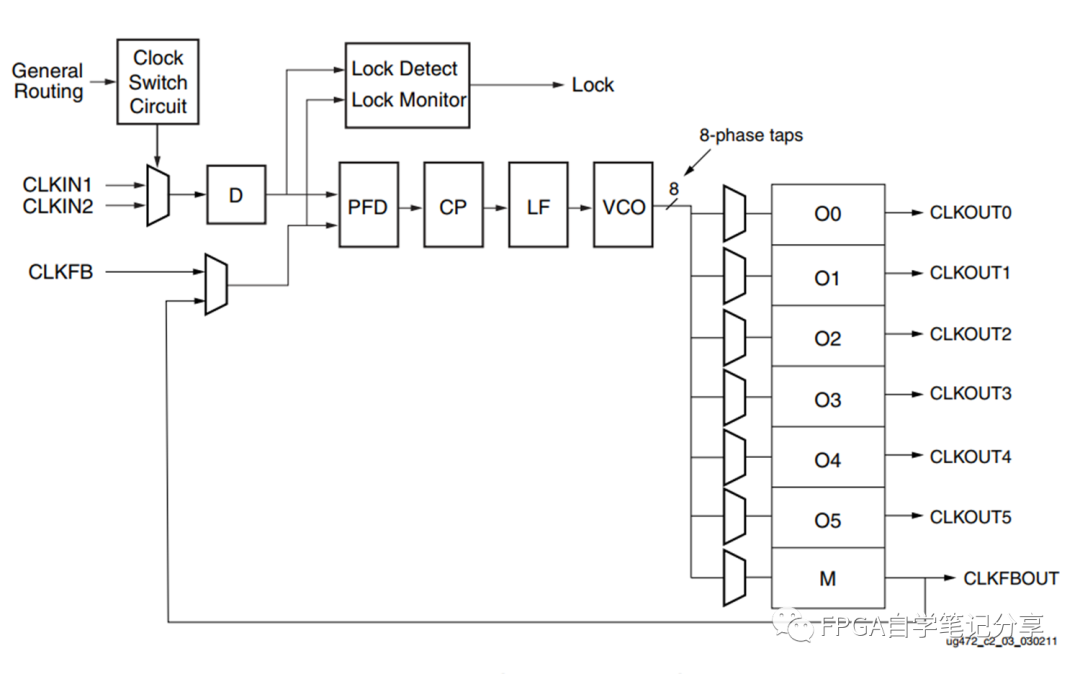

*M/D,PLL的输出频率为FOUT=(FIN*M)/(N*O)。Xilinx提供了用于实现时钟功能的IP核Clocking Wizard,该IP核能够根据用户的时钟需求自动配置器件内部的CMT及时

2020-09-22 16:48:59

除了在Xilinx官网上在哪里能下载到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

do after Xilinx Clocking Wizard, there is no responding vhdl file generated. I want to know what

2019-01-15 10:22:23

Altera系列FPGA芯片IP核详解

2016-08-19 17:24:48

怎样开发用户自定义IP。本书内容翔实,实践性强,结合具体的实验详细讲解了开发工程的过程,以帮助用户较快熟悉用户IP的开发。本书适用于具有一定XILINX FPGA开发应用经验,熟悉DHL语言,致力于

2017-12-08 14:27:35

FPGA的特点及其发展趋势IP资源复用理念与IP Core设计基于Xilinx FPGA的嵌入式系统设计

2021-04-30 07:21:50

本帖最后由 scratdqy 于 2015-8-17 11:06 编辑

向各位大神求助GTX问题!!用xilinx的Vivado中的7 Series FPGAs Transceivers

2015-07-28 18:54:12

网络革新之软定义网络(SDN)详解

2021-05-24 06:34:46

Xilinx系列FPGA芯片IP核详解 ,altera系列FPGA芯片IP核详解 , 相关资料 谢谢!!万分感谢!!!!!

2015-06-03 15:03:34

FPGACPLD设计工具——Xilinx ISE使用详解的主要内容:第1章 ISE系统简介第2章 工程管理器与设计输入工具第3章 ModelSim仿真工具第4章 ISE中集成的综合工具第5章 约束第6章

2009-07-24 16:06:58 197

197 tcp ip协议详解卷一:《TCP/IP详解,卷1:协议》是一本完整而详细的TCP/IP协议指南。描述了属于每一层的各个协议以及它们如何在不同操作系统中运行。作者用Lawrence Berkeley实验室的tcpd

2010-05-19 12:02:19 711

711 通过将第三方IP集成到NI LABVIEW软件中,您可以使用许多为XILINX现场可编程门阵列(FPGA)精调过的算法实现高性能,并且提高代码重用度。LABVIEW FPGA模块为导入外部IP提供了两个方法:组件级知识产权(CLIP)节点和结合XILINX核心生成器的IP集成节点。本技

2011-03-15 13:25:58 90

90 TCP/IP Configuration Wizard V3.32软件说明: TCP/IP配制向导 V3.23 注:它内部所提供的LIB库是KEIL V8.0X版本,低版的KEIL会通不过的!请使用新的正版KEIL编译软件!

2011-04-16 09:05:39 169

169 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

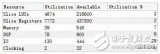

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 CST天线阵模块详解(Array Wizard)

2013-09-12 16:19:15 93

93 2014年11月17日,中国北京 - All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布推出业界首款FPGA低时延25G以太网IP,用以解决数据中心应用所面临的吞吐量难题。

2014-11-17 15:50:00 1358

1358 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 利用FPGA的IP核设计和实现FFT算法

2016-05-24 14:14:47 36

36 Xilinx FPGA工程例子源码:PCI Express IP核应用参考设计

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源码:IP camera的开源系统

2016-06-07 14:13:43 13

13 Xilinx FPGA工程例子源码:LCD IP CORE

2016-06-07 14:13:43 10

10 Xilinx FPGA工程例子源码:USB IP核

2016-06-07 14:41:57 13

13 Xilinx FPGA工程例子源码:Xilinx TCP_IP协议实现

2016-06-07 14:54:57 31

31 Xilinx FPGA工程例子源码:Xilinx 的IP:1024点FFT快速傅立叶变换

2016-06-07 15:07:45 51

51 研究了TCP/IP通信协议栈在Xilinx 公司现场可编程门阵列FPGA上的实现,介绍了其软硬件的系统组成

和原理,提出一种不需操作系统的TCP/IP协议栈的高效工作模式,并在

2017-09-04 09:24:59 9

9 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 。 使用Xilinx内核生成器IP函数实现FPGA VI中不同的Xilinx内核生成器IP。LabVIEW使用IP集成节点实现上述函数。函数名称和说明来自于Xilinx数据表。单击Xilinx内核生成器配置对话框的数据表按钮,了解IP内核的详细信息。 选板随终端变化且仅显示FPGA设备系列支持的IP。

2017-11-18 05:54:05 1286

1286 本页包含通过LabVIEW FPGA模块可用的Xilinx CORE生成器IP的列表。LabVIEW通过Xilinx IP节点实现该IP。 下列IP名称和说明来自于Xilinx数据表。LabVIEW

2017-11-18 05:55:51 4465

4465 LabVIEW使用IP集成节点方便的整合Xilinx内核生成IP至FPGA VI。按照下列步骤添加Xilinx内核生成器IP至FPGA VI。 1、在支持的FPGA终端下新建一个空白VI,并显示VI

2017-11-18 05:56:22 1746

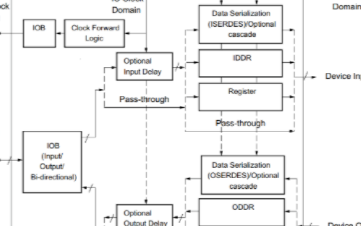

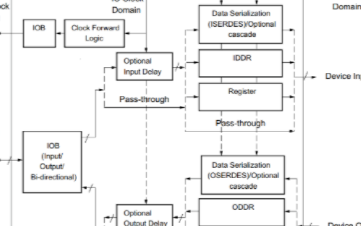

1746 这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

2018-03-21 14:48:00 4672

4672

JESD204B协议是目前高速AD,DA通用的协议。对于基带使用FPGA用户来说,Xilinx品牌的FPGA使用更为常见。Xilinx提供了JESD204的IP core,设计起来比较方便。

2018-07-04 10:12:00 3977

3977 本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。

2019-02-17 11:03:52 10578

10578

本文档的主要内容详细介绍的是基于XIlinx芯片FPGA开发的CTC8 IP核工程文件 用于8进制循环计数 免费下载。

2019-07-26 08:00:00 13

13 本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 Xilinx LogiCORE IP块内存生成器(BMG)内核是一种高级内存构造函数,它使用XilinxFPGAs中的嵌入式块RAM资源生成区域和性能优化的内存。

2020-12-09 15:31:00 22

22 时钟向导逻辑存储器™ IP简化了为时钟电路定制的HDL源代码包装器的创建,以满足您的时钟要求。向导将指导您为计时原语设置适当的属性,并允许您覆盖任何向导计算的参数。除了提供用于实现所需时钟电路的HDL包装器外,时钟向导还提供由Xilinx®计时工具为电路生成的时序参数摘要。

2020-12-10 14:20:11 1

1 Validating ADI Converters Inter-operability with Xilinx FPGA and JESD204B/C IP

2021-02-19 16:05:33 11

11 验证ADI转换器与Xilinx FPGA和JESD204B/C IP的互操作性

2021-04-09 14:37:51 13

13 AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 11

11 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA参考设计

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 17

17 验证ADI转换器与Xilinx FPGA和JESD204BC IP的互操作性

2021-06-02 12:36:44 8

8 雷达信号处理离不开高速ADC/DAC的使用,而高速ADC/DAC的信号处理对时序的要求非常苛刻。Xilinx SelectIO IP的出现满足了大多数芯片对于时序的处理需求,开发者可以高效的完成ADC/DAC驱动设计。

2021-07-02 17:57:43 4351

4351

Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 24

24 ISE版本为14.7 1、时 钟IP核(Clocking Wizard) 第一页 Clocking Features选项框中: (1)Frequency synthesis选项是允许输出与输入

2022-07-03 14:42:10 2163

2163 今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

2023-02-02 10:14:01 2529

2529 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。

2023-07-10 10:43:18 632

632

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 2357

2357

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

本文开源一个FPGA高速串行通信项目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收发器,本工程主要是围绕该IP核采用Vivado提供的例程创建。

2023-10-01 09:48:00 2604

2604

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317 Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

电子发烧友App

电子发烧友App

评论