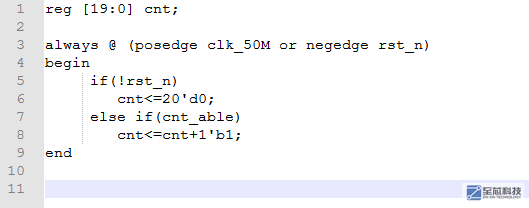

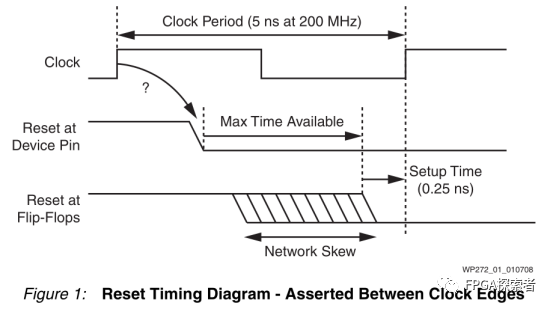

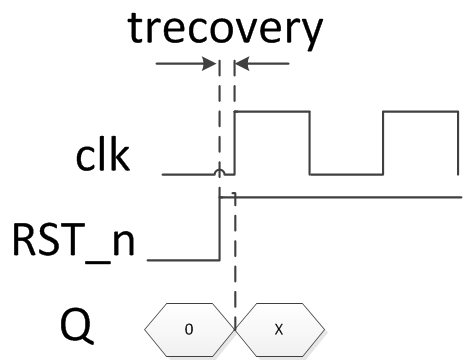

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

8153 大家好,博主最近有事忙了几天,没有更新,今天正式回来了。那么又到了每日学习的时间了,今天咱们来聊一聊 简谈FPGA的上电复位,欢迎大家一起交流学习。 在基于verilog的FPGA设计中,我们常常

2018-06-18 19:24:11 19894

19894

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 1461

1461

本篇文章参考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global 在没看这篇文章前,回想一下平时我们常用的复位方式

2020-11-18 17:32:38 3110

3110 内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。后来也看了一些书籍,采用异步复位同步释放,对自己设计的改进。 不过自从我研读了Xilinx的White Paper后,让我对复位有了更新的认识

2020-12-25 12:08:10 2303

2303

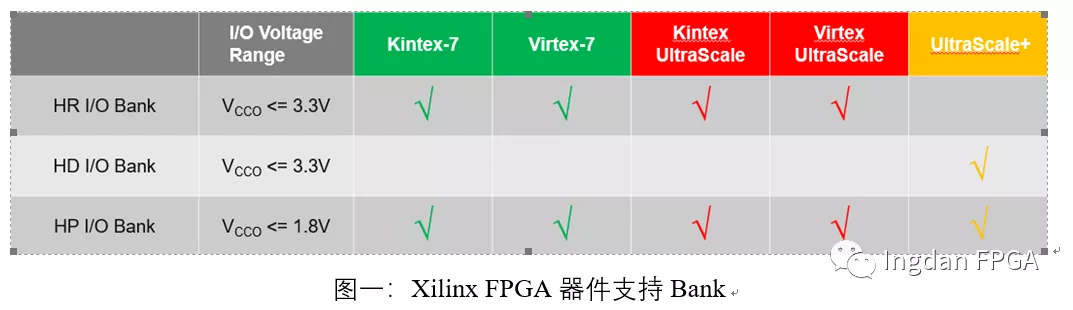

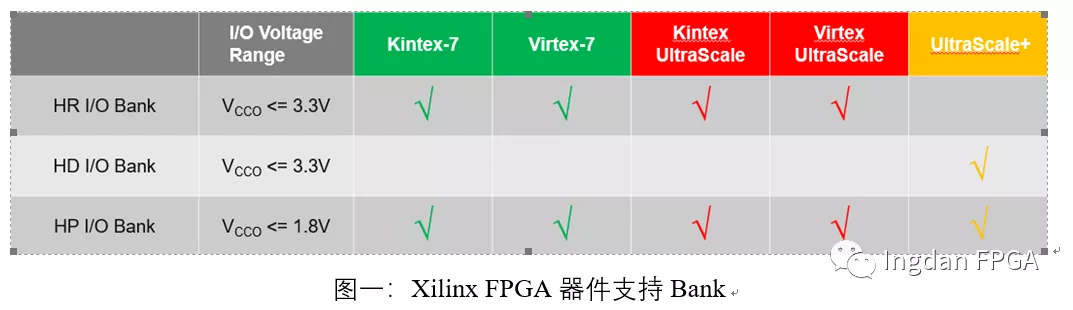

FPGA是电子器件中的万能芯片,Xilinx FPGA处于行业龙头地位更是非常灵活。FPGA管脚兼容性强,能跟绝大部分电子元器件直接对接。Xilinx SelectIO支持电平标准多,除MIPI

2022-08-02 09:31:28 4824

4824

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 1679

1679

在FPGA设计中,当复位整个系统或功能模块时,需要将先关寄存器被清零或者赋初值,以保证整个系统或功能运行正常。在大部分的设计中,我们经常用“同步复位”或“异步复位”直接将所有的寄存器全部复位,这部分可能大家都习以为常。但实际上,是否需要每个寄存器都进行复位呢?这是一个值得探讨的问题。

2023-05-14 14:49:19 1701

1701

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

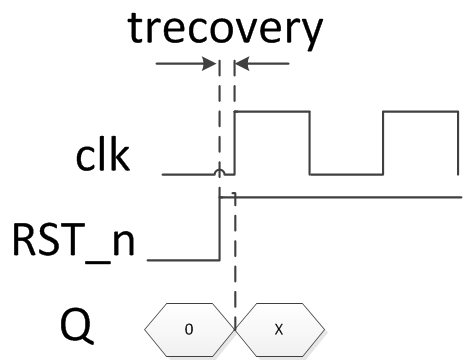

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2023-06-21 09:59:15 647

647

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

需要注意以下几个要点:●尽可能使用FPGA的专用复位引脚。(特权同学,版权所有)●上电复位时间的长短需要做好考量。(特权同学,版权所有)●确保系统正常运行过程中复位信号不会误动作。(特权同学,版权所有) Xilinx FPGA入门连载

2019-04-12 06:35:31

随着FPGA设计越来越复杂,芯片内部的时钟域也越来越多,使全局复位已不能够适应FPGA设计的需求,更多的设计趋向于使用局部的复位。本节将会从FPGA内部复位“树”的结构来分析复位的结构。我们的复位

2019-05-17 08:00:00

FPGA的任意一个管脚都可以作为时钟输入端口,但是FPGA专门设计了全局时钟,全局时钟总线是一条专用总线,到达片内各部分触发器的时间最短,所以用全局时钟芯片工作最可靠,但是如果你设计的时候时钟太多

2012-02-29 09:46:00

本帖最后由 ycq654263138 于 2012-9-13 16:53 编辑

各位FPGA工程师们,本人FPGA新手,但对FPGA有着极大的兴趣!所以,想问问前辈们,你们的FPGA开发板,你

2012-09-06 16:19:02

本帖最后由 lee_st 于 2017-10-31 08:58 编辑

FPGA技巧Xilinx,

2017-10-21 20:30:04

FPGA技巧Xilinx,,

2017-09-28 13:45:41

图如图2所示。图2 异步复位电路图根据异步电路的特点,异步复位的优点有:(1)由于多数目标器件库的触发器都包含异步复位端口,异步复位会节约逻辑资源。(2)异步复位设计简单。(3)对于多数FPGA,均有

2021-06-30 07:00:00

FPGA设计高级技巧Xilinx篇

2012-08-11 16:07:48

Use Virtual IO core and TCL script to accommodate FPGA debugging/testing.基础:Virtual IO 是Xilinx FPGA

2012-03-08 15:29:11

本本将从常见的XILINX FPGA和Altera 两家FPGA的电源供电作如下介绍:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

`Xilinx FPGA入门连载17:PWM蜂鸣器驱动之复位与FPGA重配置功能特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1 复位

2015-10-26 12:05:15

Xilinx FPGA SF-SP6入门指南 -- PWM蜂鸣器驱动之FPGA配置芯片固化Lesson19 特权Xilinx FPGA SF-SP6入门指南 -- PWM蜂鸣器驱动之复位与FPGA重配

2015-07-22 11:49:20

Xilinx_FPGA_内部结构深入分析存储单元存储单元可以配置为D触发器,就是我们常说的FF,Xilinx称之为FD;也可以配置为锁存器,Xilinx称之为LD。输出和三态通路各有一对寄存器外加一

2012-08-02 22:48:10

好。 另外就是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,如果你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,这样你的RAM资源就少了一半,如果你的应用对片内双口RAM的需求很重要,用Altera的就划不来。更多资料请点击下载:[hide][/hide]

2012-02-28 14:40:59

您好Xilinx社区,有人能否就Spartan-6 FPGA是否需要设计中的上电复位电路给出明确的答案?在附图中,我们的设计中有这个上电复位电路。然而,我们遇到了电路问题,并决定在我们的设计中将

2019-04-18 10:15:45

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP产品介绍使用Xilinx的FPGA、SoC和ACAP进行设计和开发

2021-01-22 06:38:47

Altera所不及,马上要找工作了,仅仅会一点Altera的FPGA,对当前国内大部分公司用的FPGA是什么都不太清楚,Xilinx做的那么好市场那么大,我学的Altera是否还有用武之地,望大神们赐教,别跟我说学什么都一样,我只是想知道现状,谢谢

2016-12-04 15:42:25

很逼真的水淹电脑屏保_可能会吓坏你哦

2008-06-23 12:34:52

本帖最后由 jfzhangjin 于 2015-1-8 10:48 编辑

之前也一直在做关于Xilinx FPGA各个方面的文章,但是总体而言就显得有些杂,总希望能有人能整理一下便于查阅;另外

2014-11-03 17:15:51

之前也一直在做关于Xilinx FPGA各个方面的文章,但是总体而言就显得有些杂,总希望能有人能整理一下便于查阅;另外针对目前电子发烧友网举办的“玩转FPGA:iPad2,赛灵思开发板等你拿

2014-11-05 13:56:42

xilinx fpga开发板spartan6 xilinx spartan-6 xilinx板xilinx套件我希望在1周内从新加坡这个董事会更老。如果你知道plz与我分享link.thx以上

2019-07-22 09:00:55

,但不建议在 FPGA 内部使用锁存器形式的异步逻辑)。每个寄存器的时钟(或使能信号)可以配置为高电平有效或低电平有效。同样,置位 / 复位输入的有效电平也是可配置的。 这些逻辑块可以被视为漂浮

2020-10-22 11:46:32

我有一个用于过时的Xilinx FPGA的加载文件。是否有机会将其转换为Xilinx新FPGA的文件?例如斯巴达。以上来自于谷歌翻译以下为原文I have a loading fille fora

2019-02-13 07:53:44

简化Xilinx和Altera FPGA调试过程:通过FPGAViewTM 解决方案,如混合信号示波器(MSO)和逻辑分析仪,您可以在Xilinx 和Altera FPGA 内部迅速移动探点,而无需重新编译设计方案。能够把内部FPGA

2009-11-20 17:46:26 26

26 十分钟学会Xilinx FPGA 设计

Xilinx FPGA设计基础系统地介绍了Xilinx公司FPGA的结构特点和相关开发软件的使用方法,详细描述了VHDL语言的语法和设计方法,并深入讨

2010-03-15 15:09:08 177

177 安富利推出Xilinx Virtex-6 FPGA DSP开发工具套件安富利公司旗下运营机构安富利电子元件宣布推出Xilinx Virtex -6 FPGA DSP开发工具套件。这套件是为DSP设计而打造,是Xilinx目标设计平

2010-04-24 09:56:31 1331

1331 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(二)——Xilinx FPAG开发环境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 Xilinx-ISE9.x-FPGA-CPLD设计指南合集

2022-03-22 18:03:09 76

76 Xilinx FPGA工程例子源码:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 FPGA学习资料教程之Xilinx-FPGA-引脚功能详细介绍

2016-09-01 15:27:27 0

0 FPGA学习资料教程之Xilinx-FPGA高级开发工具,感兴趣的可以看看。

2016-09-01 15:27:27 0

0 赛灵思(Xilinx)公司FPGA器件的高速串行收发器类别如下

2017-02-11 11:11:30 5958

5958

在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 876

876

当ISE调用ModelSim进行仿真的时候,如果在FPGA设计中使用了Xilinx提供的的IP core或者其他的原语语句,ModelSim不添加Xilinx相应的库文件的话,是无法仿真的。

2017-02-11 15:22:37 1274

1274

(Xilinx)FPGA中LVDS差分高速传输的实现

2017-03-01 13:12:04 64

64 文档内容包含基于Xilinx FPGA的开发板代码及原路图,供网友参考。

2017-09-01 11:09:24 20

20 FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

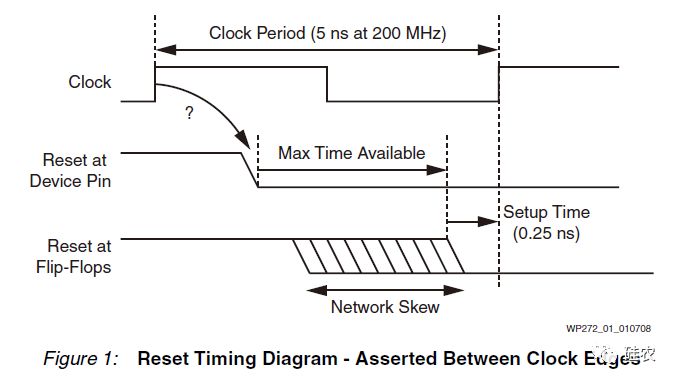

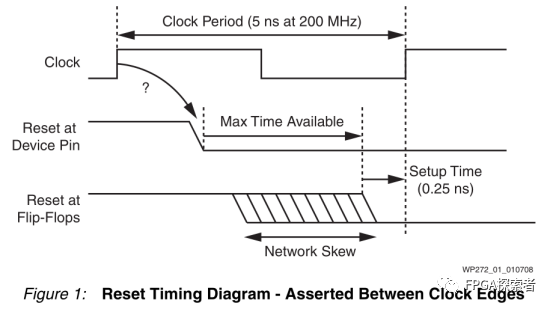

23 在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

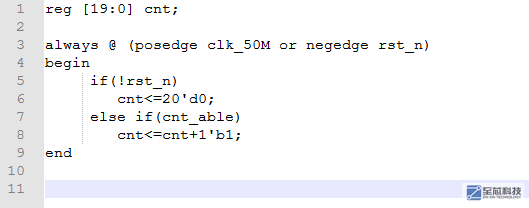

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 1989

1989 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 JESD204B协议是目前高速AD,DA通用的协议。对于基带使用FPGA用户来说,Xilinx品牌的FPGA使用更为常见。Xilinx提供了JESD204的IP core,设计起来比较方便。

2018-07-04 10:12:00 3977

3977 使用TI解决方案为Xilinx新型FPGA提供电源(一)

2018-08-22 00:01:00 3168

3168 在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

2018-08-07 09:17:18 10969

10969 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 10154

10154 FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 1588

1588 在此Xilinx研究实验室演示中,解释了单源SYCL C ++示例以及生成在Xilinx FPGA上运行的硬件实现的方法。

2018-11-20 06:30:00 2918

2918 Xilinx FPGA是支持OpenStack的第一个(也是目前唯一的)FPGA。

该视频快速介绍了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展台上运行每个演示,并使用OpenStack进行配置和管理。

2018-11-23 06:14:00 3322

3322 xilinx推荐尽量不复位,利用上电初始化,如果使用过程中需要复位,采用同步高复位。

2019-02-14 14:29:49 5419

5419 复位信号设计的原则是尽量不包含不需要的复位信号,如果需要,考虑使用局部复位和同步复位。

2019-10-27 10:09:53 1735

1735

本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 2456

2456

最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 323

323 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 14065

14065 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 本文档的主要内容详细介绍的是Xilinx 7 系列FPGA中的Serdes总结。

2020-12-31 17:30:58 25

25 SSM2518 pmod Xilinx FPGA参考设计

2021-04-20 16:05:07 3

3 AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 11

11 引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

2021-05-01 09:47:00 10367

10367

ADXL362 pmod Xilinx FPGA参考设计

2021-05-11 10:44:18 9

9 ADT7420 pmod Xilinx FPGA参考设计

2021-05-12 08:08:26 3

3 ADXL345 pmod Xilinx FPGA参考设计

2021-05-16 19:45:16 8

8 ADP5589 pmod Xilinx FPGA参考设计

2021-05-16 20:37:58 1

1 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA参考设计

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 17

17 基于FPGA的小波滤波抑制复位噪声方法

2021-07-01 14:42:09 24

24 Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 24

24 自 1985 年 Xilinx 开发出第一个商业上可行的 FPGA 以来,FPGA 细分市场的价值已经增长到数十亿美元。Xilinx 本身的年收入超过 30 亿美元,在汽车、5G、基础设施和数

2022-08-05 16:49:26 979

979 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 1585

1585 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 3347

3347

本文将探讨在 FPGA 设计中添加复位输入的一些后果。 本文将回顾使用复位输入对给定功能进行编码的一些基本注意事项。设计人员可能会忽略使用复位输入的后果,但不正确的复位策略很容易造成重罚。复位

2023-05-25 00:30:01 483

483 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 2110

2110

Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 尽量少使用复位,特别是少用全局复位,能不用复位就不用,一定要用复位的使用局部复位;

2023-06-21 09:55:33 1337

1337

能不复位尽量不用复位,如何判断呢?如果某个模块只需要上电的时候复位一次,工作中不需要再有复位操作,那么这个模块可以不用复位,用上电初始化所有寄存器默认值

2023-06-28 14:44:46 526

526

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

电子发烧友App

电子发烧友App

评论