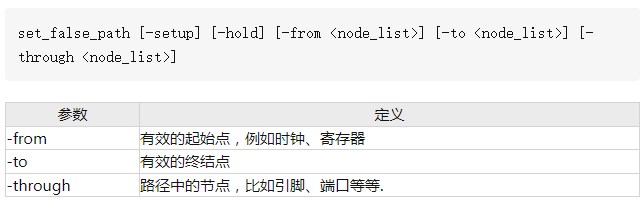

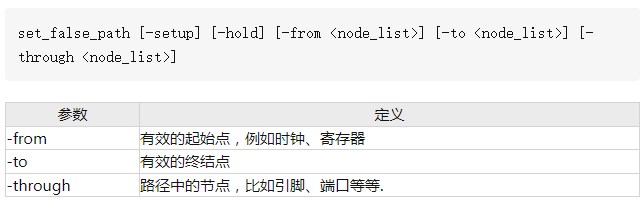

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

32位ARM嵌入式处理器的调试技术摘要:针对32位ARM处理器开发过程中调试技术的研究,分析了目前比较流行的基于JTAG的实时调试技术,介绍了正在发展的嵌入式调试标准,并展望期趋势。关键词:嵌入式

2021-12-14 09:08:18

本文以Altera公司的FPGA为目标器件,通过开发实例介绍FPGA开发的完整的流程及开发过程中使用到的开发工具,包括QuartusII、FPGA CompilerII、Modelsim,并重点解说如何使用这三个工具进行协同设计。

2021-04-29 06:04:13

的方法一般有四个步骤:时序分析→时序约束→时序报告→时序收敛。

为什么要进行时序分析?

信号在系统中传输时由于经过一些逻辑器件和PCB上的走线会造成一定的逻辑延时和路径延时,如果系统要求信号

2011-09-23 10:26:01

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

造成困难。 2. 时序修正 严格遵守Vivado开发流程,在第一次跑综合时最好是在没有任何物理约束的情况下,Vivado在越少物理约束的情况下综合出来的效果越好。查看每个阶段的时序报告,将每一阶

2020-12-23 17:42:10

的,在有问题的时候能有人能够解答,也是我感触很深的一点,大家在帖子下方发出学习过程中遇到的问题,我会力所能及的回答大家的问题。希望大家在FPGA开发的道路上越来越顺利。提问的范围举例:1、FPGA硬件

2019-10-14 10:08:35

CMOS摄像头接口时序设计5时序报告(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s

2015-08-19 21:58:55

。 在FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner软件可以提取相关信息和利用图表更新

2017-09-01 10:28:10

学习。个人学习的时候可以根据实际情况选择最高至Vivado2019.1。(从Vivado2019.2开始,PS开发使用Vitis,没有SDK了)第1章 FPGA技术分析 / 11.1 FPGA内部结构

2020-10-21 18:24:48

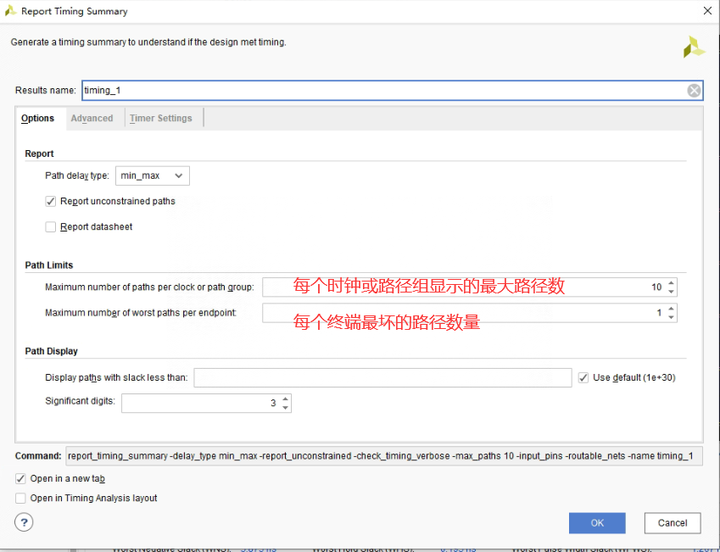

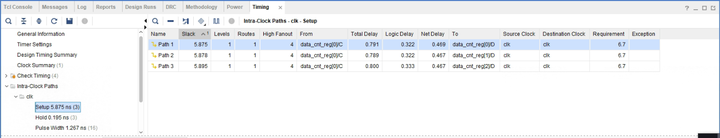

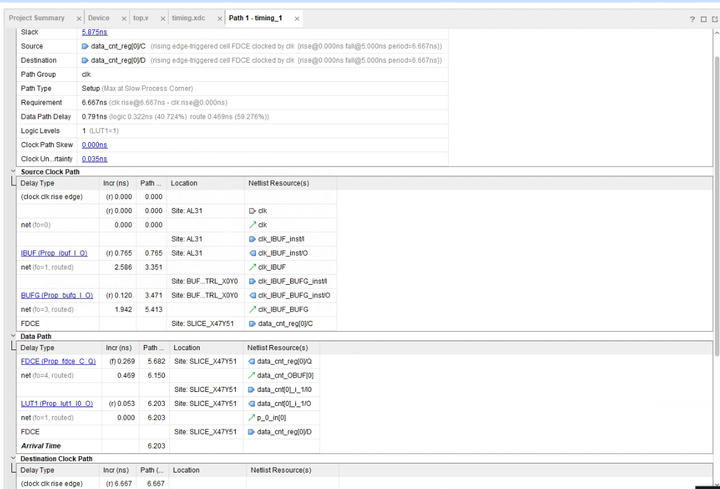

Vivado运行Report Timing Summary时,只显示各个子项目最差的十条路径,很可能并不包含你最关心的路近,这个时候显示指定路径的时序报告就显得很重要了,下面就简单介绍一下

2021-01-15 16:57:55

在学习fpga的过程中的疑问:1、在功能仿真和板级验真后没问题,还需要进行时序分析吗2、怎么知道自己写的代码有时序问题?

2017-01-08 17:50:35

最近用华大 HC32L176KATA开发过程中发现一个问题,引脚PC11控制LED指示灯,调用函数Gpio_WriteOutputIO(GpioPortC, GpioPin11, x&

2021-12-06 06:50:14

LabVIEW开发FPGA?开发过程是什么?有相关书籍资料吗?

2015-08-10 21:08:55

JTAG设备STM32 汇编汇编中含C语言注释数字信号处理滤波IIR滤波器本人STM32开发过程中的一些心得及总结。比较好的文章加密STM32MCU加密原理与方法 (很详细)驱动开发启动使用CCMRAM内...

2021-08-17 08:50:02

STM32开发过程中遇到的一些问题,记录如下。Q1:下载后程序不运行,反复排查代码没问题。A1:栈空间太小,打开startup_stm32f10x_hd.s,把 Stack_Size EQU

2021-08-20 06:48:00

开发过程中的一个重要特点,这就要求设计者从一开始就要非常认真细致,否则后续的很多工作量可能就是不断的返工。图1.32 FPGA开发流程 基于Xilinx的Vivado开发工具,我们对以上开发流程所涉

2019-04-01 17:50:52

进行openharmony组件开发过程中,hi3516打开烧录进去的hap包显示蓝屏运行的hap包是官方的jsholleworld,上图是打开app时后台显示的信息与设备的显示画面

2022-04-13 11:28:07

设计意图以及性能的目标和综合工具之间的通信。设计一旦综合完毕,这些约束和关键路径信息将被自动注释到Vivado设计套件的摆放和路由(P&R)工具中,进一步确保满足时序。 第二步:RTL代码风格

2019-08-11 08:30:00

为什么开发过程中有些不带光耦隔离的继电器需要引脚开漏输出控制

2023-11-03 06:41:40

产品研发过程中EMC传导发射预测试方法

2015-08-05 15:51:37

分享两个开发过程中我最常用的文件

2016-10-25 14:23:12

**.**单片机开发过程中按键处理函数的实现**.**方法一 这种方法在单片机处理中反应不够好,当按键交替按时,会表现的不够好voidKey_Scan(void){uint8_t

2021-11-22 06:03:41

Flash在我们生活中无处不在,比如:U盘、固态硬盘、SD卡、内存卡等。同时,在单片机开发过程中也会遇到各种各样的Flash,...

2021-12-09 08:00:20

单片机在组装与开发过程中总是会出现一些问题,导致过程不是那么顺利的完成。今日分享一些单片机常见问题的解决办法1.单片机EN8F609兼容PIC12F629,仅有一个中断入口,要避免多个中断引发的冲突

2018-09-11 16:33:29

在FPGA开发过程中,编程与配置这两个操作有什么区别?

2023-04-06 14:44:05

设计意图以及性能的目标和综合工具之间的通信。设计一旦综合完毕,这些约束和关键路径信息将被自动注释到Vivado设计套件的摆放和路由(P&R)工具中,进一步确保满足时序。第二步:RTL代码风格和关键

2021-05-18 15:55:00

今天在RT-Thread完整版开发过程中引入watchdog,踩到一个坑,系统一直重启,喂狗一直失败,搞了一天才解决,总结一下。我的RT-Thread完整版系统是最新版4.0.3(截止2020年12

2022-02-17 06:05:39

在单片机开发过程中怎样使用定时器进行定时及超时处理呢?

2022-01-21 07:33:27

在嵌入式开发过程中常用的库函数有哪些?有何优势?

2022-02-25 07:07:18

目标 博文旨在总结自己在嵌入式linux开发过程中遇到的坑⛈、一些小知识点的汇总。☔等哪天发展到远离代码了,还能回一下当年的英姿。

2021-11-05 09:06:58

OSEK/VDX标准包括哪几个部分?OSEK/VDX任务管理的三种状态分析基于OSEK规范的应用开发过程是怎样的?

2021-05-13 06:55:08

本文主要是记录基于STM32WB55的核心板设计开发过程中遇到的关键问题及解决方案。1、硬件设计目前PCB已打板回来焊接完成。后续需要优化的地方有如下所示:1、LSM6DSLTR传感器的封装

2021-08-11 08:27:57

大家好,我想知道如何实现硬件(FPGA)中的时序报告给出的时序。我的意思是,如何测量FPGA和FPGA中输入信号的建立或保持时间与静态时间报告给出的值进行比较。FPGA怪胎以上来自于谷歌翻译以下

2019-01-15 11:07:15

FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner可以提取相关信息和利用图表更新。在这

2009-04-14 17:03:52

本文针对FPGA实际开发过程中,出现故障后定位困难、上板后故障解决无法确认的问题,提出了一种采用仿真的方法来定位、解决故障并验证故障解决方案。

2021-05-06 07:18:15

嵌入式开发过程中,遇到scp Permission denied,将目标文件chmod 777也不起作用,其实需要修改ssh的配置。如下:sudo vim /etc/ssh/ssh_config将其中的PasswordAuthentication 的值给为yes即可。...

2021-11-08 09:17:58

前言本篇主要是对嵌入式开发过程中遇到的一些很小的知识点进行记录,就像阅读一篇英语文章,碰见一些不认识的,不熟悉的单词,语法,查阅资料搞懂记录下来,这些零碎的东西聚少成多,也是一笔客观的知识财富。以后

2021-12-14 07:37:13

嵌入式linux开发过程中逗比的硬件问题

2021-12-21 06:47:52

嵌入式产品与普通电子产品一样,在开发过程中需要遵循一些基本过程,即从需求分析到总体设计,详细设计到最终产品完成的过程它包括两个部分:嵌入式软件和嵌入式硬件。针对嵌入式硬件和软件的开发,不需要参与普通

2021-12-17 08:18:13

对很多人来,嵌入式软件开发过程中模块化(Modularization)是一个海市蜃楼、是一个书面词汇、是一个过气的时尚——模块化似乎从未真正的实现过。吹牛时人们常不屑的说:没吃...

2021-12-20 07:22:06

职位概述:1、从事视频图像处理的研究与开发2、设计各种驱动芯片的时序逻辑职位要求:1、负责FPGA软件代码编写、模块设计及仿真2、负责FPGA调试,资源优化与时序优化3、负责编写开发过程中的各种技术

2016-05-11 15:15:41

求大神详细介绍一下FPGA嵌入式系统开发过程中的XBD文件设计

2021-05-06 08:19:58

设计源文件和设计过程。源文件只能从当前位置访问,在设计实现过程中的每一步,数据和运行结果都存在于 Vivado 分配到的机器内存中,在用户不主动输 出的情况下,不会存储到硬盘中。

简单来讲,非工程

2023-06-28 19:34:58

ATtiny13指令执行过程中的访问时序?

2020-11-10 07:09:28

ATtiny2313指令执行过程中如何访问时序

2020-11-11 07:31:09

请问atmel32单片机开发过程中常见的问题有哪些?

2021-09-18 06:43:13

ATmega168指令执行过程中的访问时序

2020-11-09 06:36:55

程序开发过程中如何确认寄存器的值是否正确?

2020-11-24 06:53:17

单片机开发过程中,有一个好的调试系统可以极大地提高开发效率。举个例子,做平衡系统时调节PID参数,你会选择 修改参数–>编译–>烧录–>运行–>修改…,还是做一个功能可以一边

2022-01-14 08:25:36

软件,完成设计规定的性能要求。在布局布线过程中,可同时提取时序信息形成报靠。(4)时序提取:产生一反标文件,供给后续的时序仿真使用。(5)配置:产生FPGA配置时的需要的位流文件。在实现过程中可以进行

2021-06-24 08:00:01

针对客户在STM32L011D4P6应用开发过程中,碰到的启动模式问题进行了分析。并且根据问题,介绍开发工具、烧录工具中如何配置以避免影响。一 问题描述发现尽管已经为Boot0引脚提供了低电平,在

2016-08-30 16:22:14

在项目的开发过程中,项目鸿蒙中的项目名称显示给我们的项目计划类,用英文表示,然后开始我们的虚拟机会发现界面顶部显示为英文,如下图:

2022-04-28 11:48:53

提出考虑资源约束的产品开发过程仿真模型。该模型考虑产品开发过程中的返工迭代以及资源约束,根据任务信息控制能力确定任务资源分配的优先级,相对于Cooper 提出的资源分

2009-04-16 11:36:30 16

16 就目前中小型客车生产企业在产品设计、开发过程中存在的问题, 提出抓产品质量应从产品的设计与开发这个源头抓起; 产品设计过程的基础是质量控制。关键词: 客车产品 设计

2009-07-25 16:34:39 27

27 本文通过对目标机硬件环境初始化过程和硬件驱动开发过程的描述,详细介绍了基于PPC8270的BSP开发过程。在该开发实例中,该BSP软件能够在目标机模块上稳定运行,并为上层操作系统及

2011-07-23 10:32:39 2574

2574

本内容详细介绍了基于DSPs的系统开发过程

2011-09-29 17:28:18 136

136 本文结合作者在单片机开发过程中体会,讨论硬件调试的技巧。当硬件设计从布线到焊接安装完成之后,就开始进入硬件调试阶段

2012-06-01 16:09:55 13601

13601 我这个题目想说明的是,FPGA的内部的有其相应的Fabric,如何在开发过程中最好最大限度的使用它。

2017-02-11 12:53:11 1158

1158 嵌入式软件开发过程中基于功能点的缺陷度量_李冰

2017-03-14 08:00:00 0

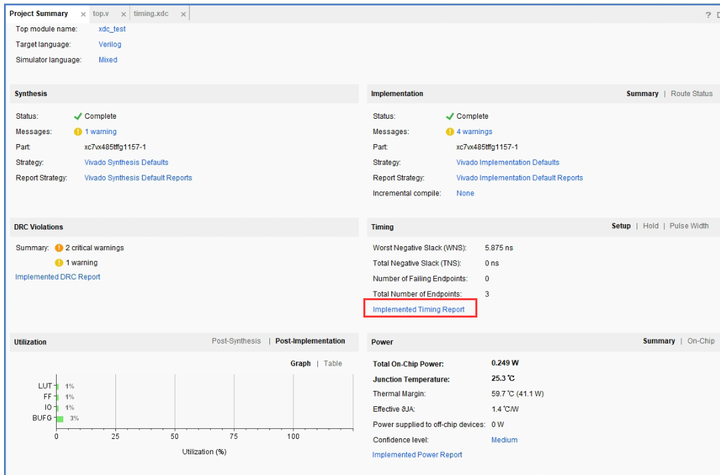

0 过程必须以满足XDC中的约束为目标来进行。那么: 如何验证实现后的设计有没有满足时序要求? 如何在开始布局布线前判断某些约束有没有成功设置? 如何验证约束的优先级? 这些都需要用到Vivado中的静态时序分析工具。

2017-11-17 18:03:55 34003

34003

Unity开发了一个多平台API和实用程序,帮助解决你在AR开发过程中遇到的众多难题,他们将其称之为 AR Foundation。

2018-09-11 09:51:00 5198

5198 在软件项目开发过程中,应该按软件开发要求撰写十三类文档,文档编制要求具有针对性、精确性、清晰性、完整性、灵活性、可追溯性!

2018-09-15 09:03:00 5801

5801 时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 5787

5787

了解report_design_analysis,这是一个新的Vivado报告命令,可以独特地了解时序和复杂性特征,这些特性对于分析时序收敛问题很有价值。

2018-11-26 07:01:00 3314

3314 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:06:00 2166

2166

小技巧进行归纳。 清理/压缩工程 实际使用vivado的过程中,由于vivado会自动产生一系列文件,有些是不

2020-12-25 14:53:36 8000

8000

VIVADO中时序报告中WNS,WHS,TNS,THS含义运行“report_timing”或“report_timing_summary”命令后,会注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

嵌入式开发过程中的一点调试经验嵌入式开发最麻烦的在现场调试过程中或实际运营过程中出现问题很难定位。我在实际开发过程中一点经验分享给大家嵌入式开发调试分为开发阶段调试,现场调试,运行调试以STM32

2021-11-02 18:06:03 15

15 **.**单片机开发过程中按键处理函数的实现 **.**方法一 这种方法在单片机处理中反应不够好,当按键交替按时,会表现的不够好void Key_Scan(void

2021-11-13 12:36:02 16

16 基于Energia的MPS430单片机开发过程中的问题

2021-11-19 17:21:02 9

9 对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20:31 2368

2368

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

FPGA开发过程中软件的综合布线耗时很长,这块对FPGA产品开发的进度影响很大。

2023-06-26 14:58:09 367

367

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

在单片机项目开发过程中,经常会出现一个有趣的问题,即弄清楚如何延迟代码执行。有时,[单片机开发]人员可能只是希望有10微秒的延迟,以使I/O线在读取之前稳定下来,或者可能希望在两次读取之间指定的时间间隔使它反跳。在本文中,我们将探讨五种延迟代码执行的技术。

2023-07-10 10:43:17 989

989 电子发烧友网站提供《Android校园应用开发过程.pdf》资料免费下载

2023-10-19 11:36:21 0

0 电子发烧友网站提供《ASIC芯片开发过程.ppt》资料免费下载

2023-12-25 10:04:49 1

1 有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18:36 291

291

电子发烧友App

电子发烧友App

评论