大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

FPGA芯片简介

作者:郝旭帅 校对:陆辉

在介绍FPGA芯片之前,首先介绍一下等效电路。

先解释一下“等效”。

等效是指效用相同。通俗的解释就是不关心过程,结果是相同的。

图1 :行走路径图

举例说明:小明现在在A点,想要到C点去。从图1中我们简单分析出,可以是A点 —> B点 —> C点,也可以A点 —> D点 —> C点。如果小明不嫌弃累的话,也可以A点 —> B点 —> A点 —> D点 —> C点。在我们不考虑不过程的情况下,只考虑最后小明的位置,那么无论哪种方案,最终的结果都是相同的。

在做电路的设计和分析的时候,我们也经常引入等效的概念,来解决复杂的问题。例如:诺顿定理(Nortons theorem)和戴维南定理(Thevenin's theorem)。在这里这两个定理不做过多介绍,有兴趣的读者可以自行查询。

黑盒测试也称功能测试,它是通过测试来检测每个功能是否都能正常使用。在测试中,把程序看作一个不能打开的黑盒子,在完全不考虑程序内部结构和内部特性的情况下,在程序接口进行测试,它只检查程序功能是否按照需求规格说明书的规定正常使用,程序是否能适当地接收输入数据而产生正确的输出信息。黑盒测试着眼于程序外部结构,不考虑内部逻辑结构,主要针对软件界面和软件功能进行测试。

黑盒测试是以用户的角度,从输入数据与输出数据的对应关系出发进行测试的。很明显,如果外部特性本身设计有问题或规格说明的规定有误,用黑盒测试方法是发现不了的。

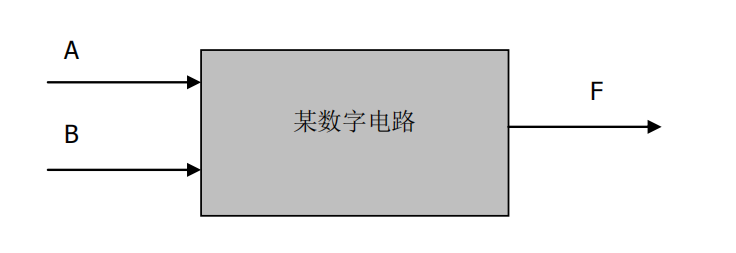

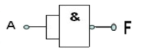

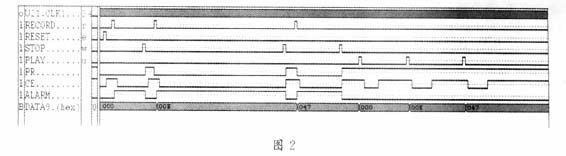

图2 :某数字电路模型

已知图2-1所示数字电路为组合逻辑,经过测试后,得出如下功能表(真值表)。

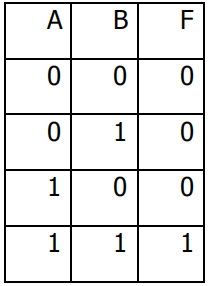

图3 :功能表

根据对功能表的分析,可以认定图2所示数字电路完成了二输入与门的功能。那这个电路里面一定是一个二输入与门吗?答案是:不一定。

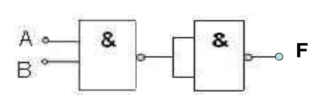

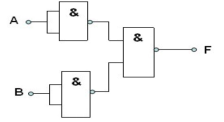

图4 :利用两个与非门构成的与门

利用两个与非门按照图2-4的方式连接,就可以构成一个“与门”。所以我们只能说图2所示数字电路只是完成了二输入与门的功能,不能说明内部就是一个二输入的与门;或者说图2所示数字电路等效为二输入与门。

在数字组合逻辑电路设计时,给出真值表后,容易得出一个布尔表达式。布尔表达式我们可以化简,化简的每个阶段,我们都可以做出对应的电路图。那么这些电路都是等效电路,只是电路延迟可能会有细微的差距。

在学习数字电路基础时,布尔表达式化简完后,经常让我们化简为与非的形式,也就是说最后的电路都要用与非门来实现?这件事情怎么证明呢?

基本逻辑的门电路有很多,例如:与门、非门、或门、与非门、异或门、或非门等等。但是最最基本的门电路只有三种:与门、非门、或门,其他的门电路或者复杂电路都可以由这三种基本电路所构成。只要证明与非门可以实现这三种逻辑门的功能就可以证明与非门可以实现所有的电路功能。

在图4中已经证明与非门可以实现与门。下面给出与非门实现或门(图5)和与非门实现非门(图6)。

图5 :利用三个与非门构成的或门

图6 :利用一个与非门构成的非门

通过之前的叙述可以证明,与非门可以实现任何数字逻辑。

所有的数字组合逻辑的功能,都可以用一个真值表来确定,我们利用一些方法,将真值表对应的逻辑功能,用电路的方式实现出来,就组成了数字电路。我们回过头来,看一下真值表,我们可以把真值表看做是一个查找表,怎么查找呢?把输入的电平值作为查表的依据,然后得出对应的结果值即可。

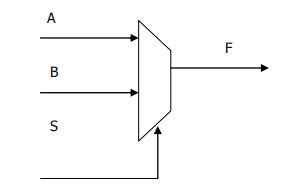

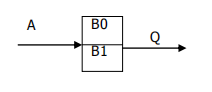

在做设计时,经常会需要一个多路选择器,下面我们以二选一多路选择器为例。

图7 :二选一多路选择器示意图

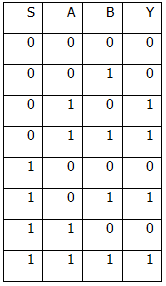

当S=0时,Y=A;当S=1时,Y=B。根据已知功能,列出真值表(图2-8)。

图8 :二选一多路选择器的真值表

根据数字组合逻辑电路的设计方法,首先做出布尔表达式,经过化简,得出简化后的布尔表达式,最后做出电路。

如果需要一个二选一多路选择器的等效电路,不关心内部是如何实现的。那么我们设计时,只需要考虑实现真值表的功能即可。当我们把真值表看做查找表时,A、B、S都是输入,任意指定一组值,都可以得出后面对应的Y即可。

下面解释一种器件:存储器。

存储器(Memory)是现代信息技术中用于保存信息的记忆设备。它根据控制器指定的位置存入和取出信息。

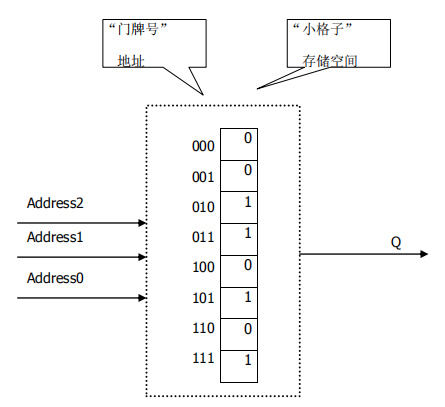

图9 :存储器模型

存储器中被分为了很多“小格子”,每一个“小格子”里面都可以放下很多的二进制数码。每个小格子都会有自己独特的标识,就像我们的门牌号一样,每个屋都是不同的。逻辑功能是当外部输入一个“门牌号”,对应的“小格子”里面的二进制数码就会输出。

存储器中的“小格子”的数量,在制造时,就已经确定。“小格子”的数量确定了,那么“门牌号”的形势也就被确定了。例:我们有100个房间,我们只有两个十进制的数码就可以表示了,00至99。在存储器中,“门牌号”也只能用二进制数来表示,例如:有4个“小格子”,那么“门牌号”就要用两个二进制码来表示,00~11。每个“小格子”里面存放的二进制数的个数,在制造时,也就确定好了。

通常我们把“门牌号”称为地址,“小格子”称为单个地址的存储空间,每个“小格子”能放下的二进制数码的个数称为“存储器的存储位宽”。

制作一个拥有8个地址,单个地址空间为1个二进制数码的存储器。此时,地址码应该有三位,每个地址对应的存储二进制数码 的个数为1个。要求:000地址中,放入0;001地址中,放入0;010地址中,放入1;011地址中,放入1;100地址中,放入0;101地址中,放入1;110地址中,放入0;111地址中,放入1;

图10 :存储器示意图

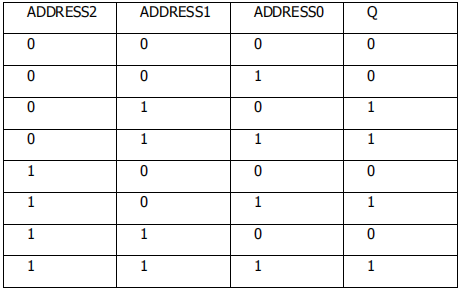

按照我们存储器的逻辑功能,给与地址,存储器就会给出对应地址中所存放的数据。那么存储器的功能表如下:

图11 :存储器的功能表

将存储器的功能表图11和二选一多路选择器的真值表图8相对比,我们会发现,除了自定义的信号名称不相同外,逻辑功能是相同的。那么也就是说,在黑盒设计时,我们可以将一个带有预设值的存储器放进去,它所对外的功能,也是可以实现二选一多路选择器的。此时,我们可以带有预设值的存储器可以等效为二选一多路选择器。

仔细观察,我们发现,任意真值表都可以用存储器来等效。那也就是说,存储器电路可以等效为任意组合逻辑的电路。

存储器电路的优势:不用做任何逻辑化简,不受基本逻辑门电路的样式限制,可以很快的得出最终的电路功能。如果存储器可以任意修改预设值的话,那么同一个存储器就可以随着不同的预设值等效为各类的电路。如果是基本门电路构成的话,就需要受到数量和样式的限制。

存储器电路的劣势:对于简单的门电路,用存储器实现是一种浪费。存储器电路也是一种相对复杂的电路。另外存储器电路的延迟一般偏大,原因同上。

在做数字组合逻辑电路设计时,如果采用门电路的设计方式,需要更新电路功能时,就需要重新布置电路结构,更换基本电路元器件;如果采用存储器等效的设计方式,只需要更改预设值即可。这种方法为我们做电路升级提供了一个很好的解决途径。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

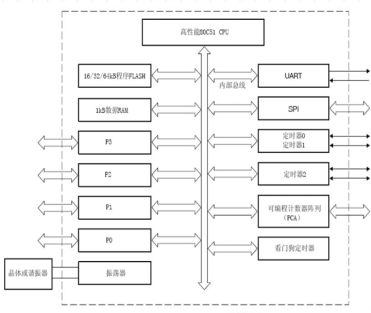

在介绍FPGA芯片结构之前,首先就FPGA和单片机做一个简单的对比。

单片机是一种微处理器,类似于电脑CPU。它的电路是固定的,是通过软件编程语言描述软件指令控制微处理器进行工作;它的所有指令都是微处理器顺序执行的;

图12 :某单片机结构图

FPGA是一种半定制电路。它的电路也是固定的,但是可以通过硬件编程语言描述电路功能,重新配置电路功能,得到我们想要的电路的等效电路;它的所有功能都是利用电路来直接实现的,所有的功能都是可以并行执行。

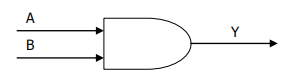

图13 :与门逻辑功能示意图

要求实现两路信号的与操作,将结果作为一路信号输出。那么在单片机中和FPGA中都是如何实现此功能的呢?

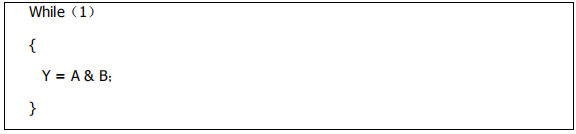

在单片机中,假设我们已经将对应的变量和引脚已经分配结束。我们会编写如下一段代码:

CPU会首先去读取A管脚的电平值,放入到自己的通用寄存器。然后读取B管脚的电平值放入到自己的通用寄存器。然后将两个电平值进行相与,结果写入通用寄存器。最后将存放结果的通用寄存器的值存入到Y管脚对应的寄存器。每一步都需要很久的时间。

在FPGA内部会形成一个存储器的等效电路(与门),直接将A管脚电平和B管脚的电平相与的结果用线连接到Y管脚了。

有些人可能不太明白,觉得这两个是相同的。都是取两个电平,然后把结果输送出去。不一样的地方有两个:

第一:单片机执行是顺序的,也就是说,每个时刻只能做一件事情。假设A管脚被取完电平后,突然降低一段时间,然后又拉高了。但是此时CPU去取B管脚电平或者输送结果到Y管脚了。那么整个设计将不会察觉到A管脚被拉低了一段时间。在FPGA中,都是直接线连接的,没有任何控制逻辑,任何的变化都会直接反映到电路的结果上。

第二:由于单片机的执行时顺序的,也就是有一个时间表,每一个时刻干什么规定好的。而FPGA是纯逻辑实现,每时每刻所有的电路都在工作。速度上要比单片机快很多。

所以FPGA的本质实现是靠自己的逻辑功能电路来实现,单片机是靠控制CPU,让CPU单个控制各个逻辑功能电路顺序实现的。

在数字电路基础中,我们知道,所有的数字电路都是由组合逻辑和时序逻辑构成,而时序逻辑是由组合逻辑和时序逻辑器件构成。所以数字电路是由组合逻辑和时序逻辑器件构成。

电路的重新配置按照现在的技术还实现不了。例如:有一个asic,现在想要他换一种功能,这是现在实现不了的,因为其中的电路是固定的,并且没有重新配置的功能。

如果想要电路能够重新配置,在上一节中叙述存储器等效电路时,我们了解到存储器电路预设不同的值是可以完成不同的电路功能。

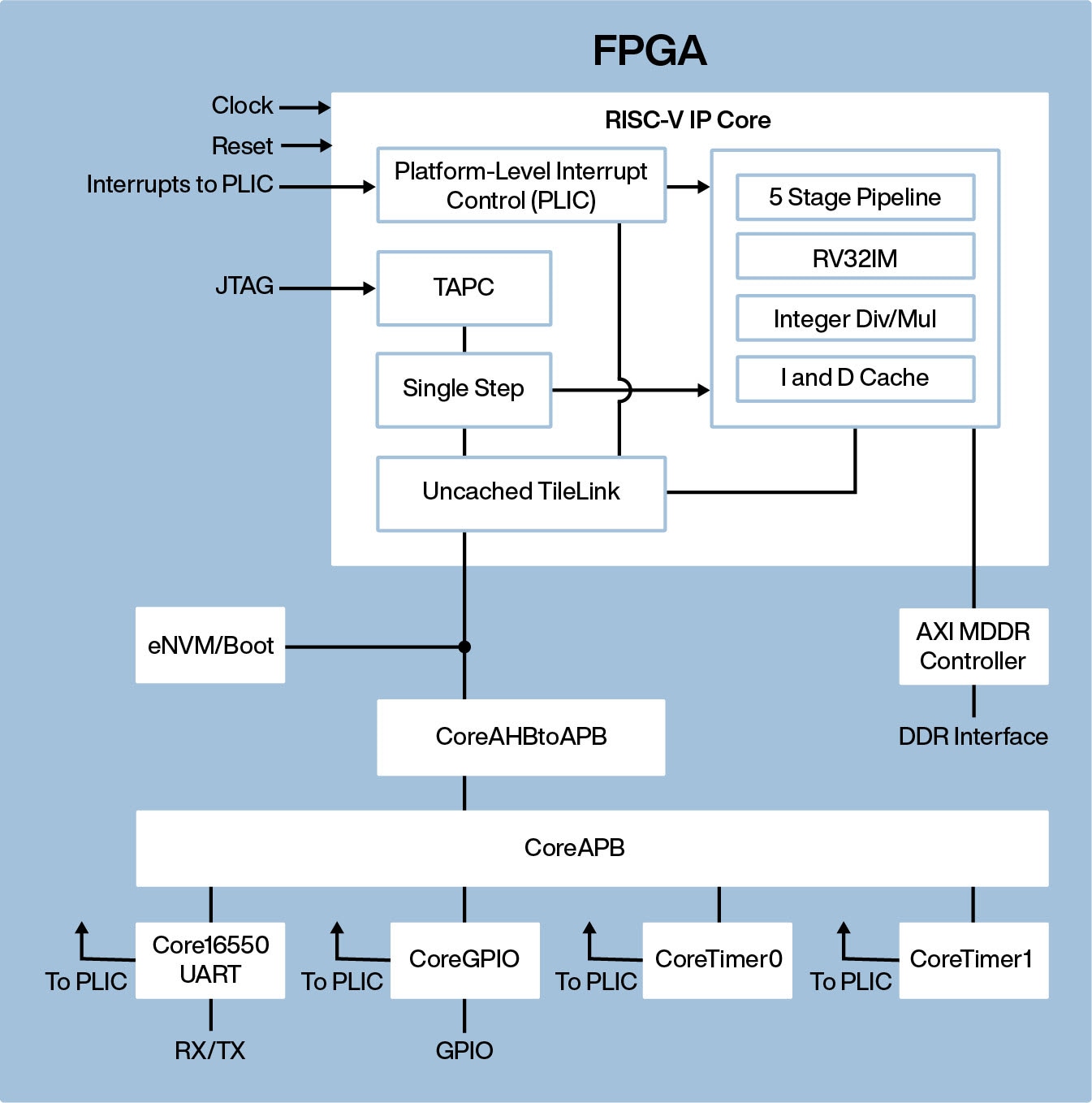

在FPGA中,由一定的存储器等效电路和时序逻辑器件构成最小单元。那么此单元可以被配置成为组合逻辑、时序逻辑。

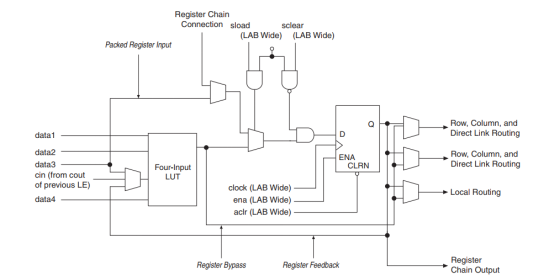

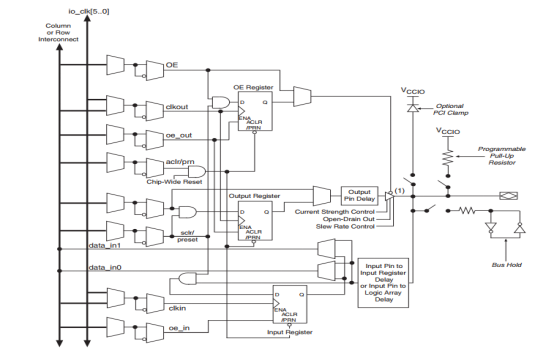

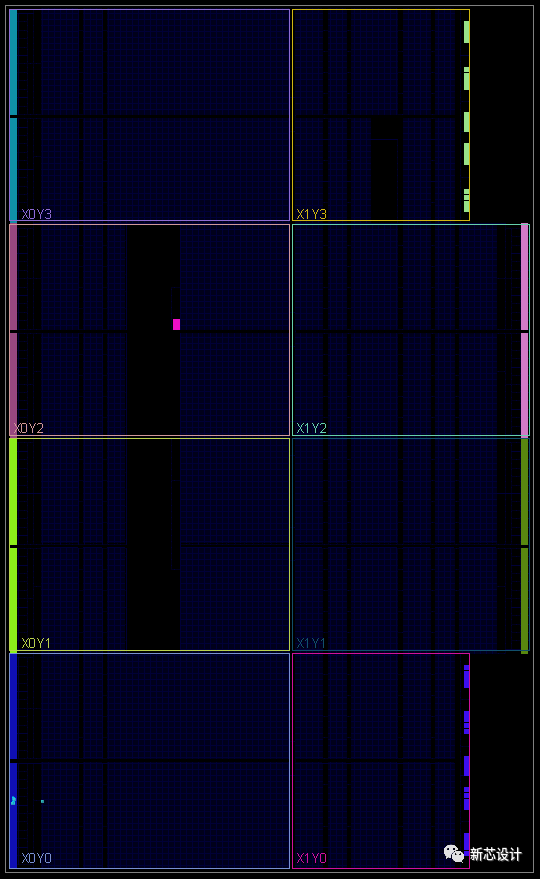

图14 :CYCLONE IV E 可编程最小单元示意图

CYCLONE IV E是INTEL FPGA中CYCLONE系列的第四代。在上图中,四输入查找表(Four – Input LUT)其实就是一个有16存储空间,每个存储空间只有1个二进制数字的存储器,LUT(Look Up Table)就是查找表。设置合理的预设值,就可以实现一定的数字组合逻辑电路功能。

那为什么要固定为16存储器空间呢?如果我们要实现一个5输入的与门,那16个存储空间就不够用了。那么此时我们应该怎么办?

其实也很简单,只需要将5输入的与门分为一个四输入的与门,然后把结果和另外一个输入进行相与即可。对于存储器电路也可以这样做。

如果可以级联的话,那么做成2输入的是不是也可以的。原则上是可以的,但是如果我们实现的逻辑功能比较复杂的话,那么就会级联特别长,延时就会很大。那做成1000输入的话,是不是就好了,再复杂的话,都不用级联。可是在设计时,我们做的不仅仅是复杂逻辑,还有很多的不复杂的,那么一个二输入与门的设计也要占用一个1000输入,那就得不偿失了。所以经过衡量,最终设计者将输入做成了4输入的查找表。

经过不断的发展,FPGA在各个场合的应用越来越多,所做的设计越来越复杂,要求的延迟越来越小。于是新出的FPGA系列拥有更多的输入查找表。

在图2-14中,后面还有一个时序逻辑器件。这个时序逻辑器件是FPGA厂商直接做到FPGA内部的,我们设计电路时,不需要设计,只需要调用出来即可。

由此,我们就可以实现组合逻辑和时序逻辑的一个小部分了。但是复杂的设计,往往是需要级联的。

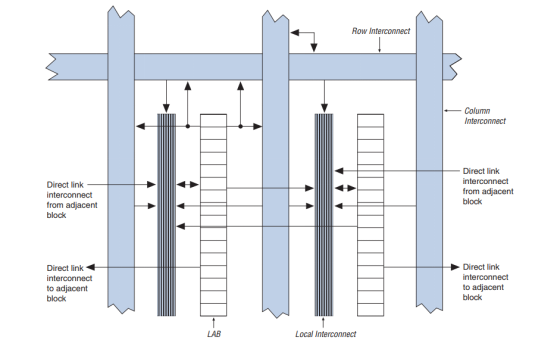

图15 :CYCLONE IV 中结构示意图

LAB中包含了很多最小可编程单元,这些可编程单元完成电路的一部分功能。然后通过各种interconnect(连线)互联,最终实现我们想要的复杂的逻辑功能。

通过可编程单元和连线资源就可以完成各种电路功能,但是最终还是在芯片内部,为了能够和外部的芯片进行通信,一定会需要IO单元。

图16 :CYCLONE IV的IO单元

在IO单元中,我们可以发现整个IO单元可以被配置为输入、输出、输入出。并且其中可以是否配置上拉电阻,以及电路延迟等等功能。

FPGA的IO数量较多,在需要同时控制多个外设时,不需要级联,一致性会比较好。

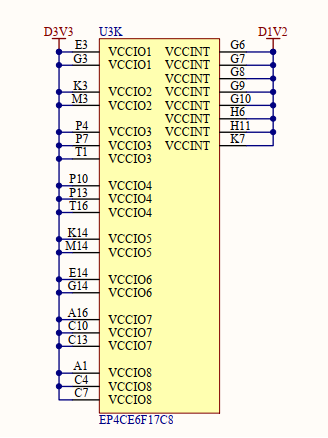

图17 :CYCLONE IV E的某块FPGA的IO供电bank

在FPGA中,内部逻辑运行是一种电压。输入输出被分为了好多个块(bank),每一个块都可以有自己的电平标准,这就让FPGA可以在不用转换电路的情况下,驱动多个不同电压标准的接口。

在图17中可以看到FPGA的内部逻辑电压相对较低,所以FPGA的功耗也相对较低。

通过上述的三种结构,一个简单的FPGA芯片就可以实现了。

在FPGA应用时,我们发现经常用到一些缓存和特殊电路,并且对这些电路的要求比较高,用FPGA实现不太现实。那么FPGA就会将其集成到FPGA内部,用大量的互联资源引出接口,供给内部逻辑进行控制或者通信。

设计者可以利用FPGA的资源实现CPU的功能,构成SOPC。

现在的很多FPGA将ARM的硬核放入到自己内部,构成SOC。

本文只是简单介绍FPGA内部结构,后续在设计时,需要详细了解结构时,会单独列出来详细讲解。有兴趣的同学可以自己查询FPGA的介绍文档。

FPGA是一种芯片,有很多的厂商都在生产和销售,下面简要介绍几个厂家以及他们的芯片。

Intel FPGA

Altera公司(阿尔特拉)自二十年前发明世界上第一个可编程逻辑器件开始,秉承了创新的传统,是世界上“可编程芯片系统”(SOPC)解决方案倡导者。Altera结合带有软件工具的可编程逻辑技术、知识产权(IP)和技术服务,在世界范围内为14,000多个客户提供高质量的可编程解决方案。我们新产品系列将可编程逻辑的内在优势——灵活性、产品及时面市——和更高级性能以及集成化结合在一起,专为满足当今大范围的系统需求而开发设计。

在2015年12月Intel斥资167亿美元收购Altera公司。至此,我们将Altera FPGA更名为Intel FPGA。

Intel FPGA的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Cyclone系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Startix、Arria系列等,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。

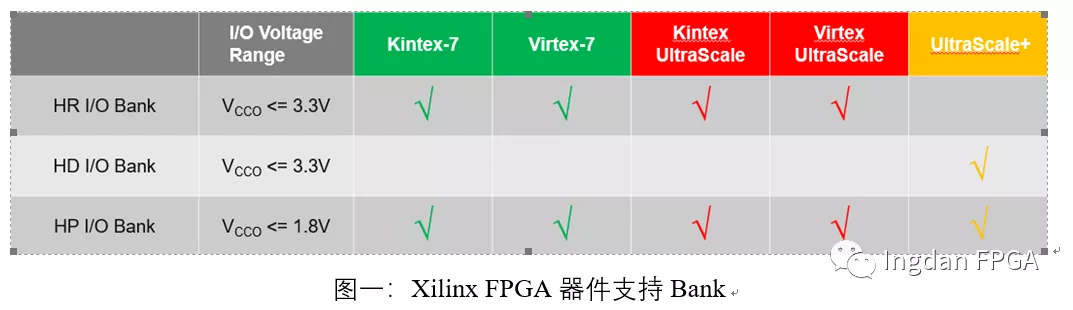

Xilinx FPGA

Xilinx(赛灵思)是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核。客户使用Xilinx及其合作伙伴的自动化软件工具和IP核对器件进行编程,从而完成特定的逻辑操作。

Xilinx的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Spartan系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Virtex系列,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。

继Xilinx正式向外界发布其推出全球首颗28nm制程的Kintex-7后,该公司推出7系列四款芯片Artix-7、Kintex-7、Virtex-7和Zynq的FPGA芯片,以及围绕7系列的开发资源。

Actel FPGA

ACTEL公司成立于1985年,位于美国纽约。之前的20多年里,ACTEL一直效力于美国军工和航空领域,并禁止对外出售。国内一些特殊领域的企业都是采用其它途径购买军工级型号。目前ACTEL开始逐渐转向民用和商用,除了反熔丝系列外,还推出可重复擦除的ProASIC3系列(针对汽车、工业控制、军事航空行业)。

Lattice FPGA

莱迪思(Lattice)半导体公司提供业界最广范围的现场可编程门阵列(FPGA)、可编程逻辑器件(PLD)及其相关软件,包括现场可编程系统芯片(FPSC)、复杂的可编程逻辑器件(CPLD),可编程混合信号产品(ispPAC)和可编程数字互连器件(ispGDX)。

国产FPGA

京微齐力、西安智多晶微电子、紫光国微、高云等等,他们都拥有自己的FPGA系列芯片。

FPGA的厂商有很多,但是基本的内部结构和开发流程是比较接近了,只要掌握一种FPGA的开发方式,其他的FPGA开发就会容易上手很多。

目前学习FPGA设计,使用INTEL FPGA和Xilinx FPGA的居多,这两家的FPGA芯片也是应用最多的。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA的特点有以下几点:

采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

FPGA可做其它全定制或半定制ASIC电路的中试样片。

FPGA内部有丰富的触发器和I/O引脚。

FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

FPGA的应用大可分为以下几种:

数据采集领域:自然界的大部分信号是模拟信号,在高速采集时,信息无法直接传入MCU或者DSP。此时,需要FPGA进行一定的转换和速率匹配。

逻辑接口领域:CPU在于外界通信时,需要各种专门的接口,而接口电路所引入的接口电路很庞大。加入FPGA,就可以CPU与FPGA做单独通信,由FPGA实现其他各种接口的扩展。

电平接口领域:不同的器件支持的电平不尽相同,如果需要连接各种接口时,就需要各种接口标准或者转换电路。对于FPGA来说,FPGA分为不同的BANK,可以直接支持不同的电平标准。

数字信号处理领域:通信、图像等领域近些年对计算量提出了更高的要求,FPGA支持并行计算,可以大大缩短计算的时间。

IC设计领域:IC在设计时,首先会使用FPGA设计出基础的电路模型进行各种理论验证,等验证通过后,才会进行IC制造等等。

通过上述的叙述,了解FPGA内部都是使用等效电路实现功能,那么它的速度是不是赶不上ASIC?

既然要做对比,就要说明一部分情况。例:如果是同等工艺条件下,FPGA是没有ASIC跑的快。各大FPGA厂商都是利用世界先进工艺做出的片子,如果某些应用类型公司尝试利用的最先进工艺做片子,那么风险比较高,费用也比较昂贵,如果采用成熟工艺去做片子,那么asic的速度不一定会有FPGA速度快。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论