三态电路有什么特点,什么是上拉电阻、下拉电阻以及高阻态?

2019-05-21 07:28:00 6269

6269

上才都有显示,这时测出的电压是5V上面的是用proteus仿真的情况,在实际中,我看jtag模块上都有一个74HC244这种芯片,我上网搜了一下,说244是三态8同相缓冲/驱动器,说是增加什么驱动

2014-07-20 11:49:56

关于FPGA的IO设计,我有以下几个疑问,希望大家多多指教1. 在FPGA设计中(Altera cyclone IV),对于一个三态口来说,设置成输入,是不是悬空的啊?(这种问题是不是找相应的手册

2015-10-31 20:13:49

FPGA布线开关的电路设计1 研究方法及其条件假定2 导通晶体管布线开关设计 2.1导通晶体管布线开关尺寸优化2.2 导通晶体管存在的问题及其改进3 三态缓冲布线开关的设计3.1三态缓冲器尺寸优化3.2 三态缓冲布线开关的缺点及其改进4 各种布线开关性能比较及其建议

2011-03-02 09:50:16

一、三态单片机IO的三态是指:高电平(1)、低电平(0)、高组态(Z)。二、高阻态高阻i是一种电路状态.既不是高电平,也不是低电平,以高阻态对下级电路输出,下级电路什么影响也没有.高阻态的IO电平

2021-11-25 06:42:28

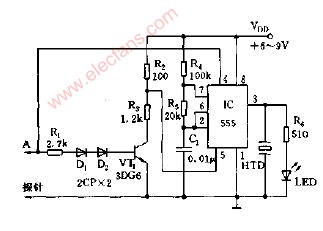

如图是一个三态反相缓冲器,我想把它和一个自偏电阻连起来做一个放大器。

2019-01-28 16:40:28

如果我在其中一个存储器上使用32位三态输出,则合成器会添加一个切片。有人能告诉我内部三态缓冲器在FPGA架构中的位置(我得到了kintex 7)吗?我在CLB指南中找了它,但没找到

2019-03-04 13:17:18

。看起来微处理器正在写入FPGA而不是从FPGA读取。但情况应该不是这样,而应该恰恰相反!在推断三态缓冲区时,我是否设置了错误?当我在planAhead中打开设计时,我可以看到“io_data”被认为是

2019-03-08 14:01:02

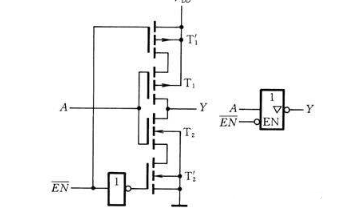

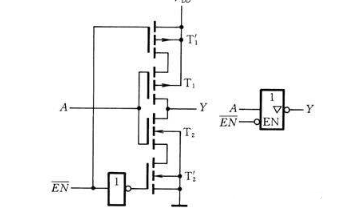

三态输出门的电路图和图形符号

2019-10-25 07:17:31

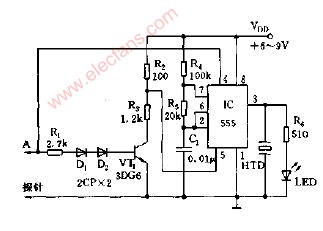

当电路的测试点没有接触任何信号电路或者接触的是高阻态时,由于电阻器R2、R3、二极管VD1、VD2的分压作用。使PNP型三极管VT1和NPN型三极管VT2均截止,LED1、LED2均不亮。

2021-05-10 07:31:04

三态门的工作原理是什么?

2021-05-20 06:55:47

三态门输入信号和输出信号之间接电阻是什么用法?

2017-04-09 19:36:20

- 2.5VVCCO_35 - 2.5V连接到I / O bank的一些外部电路在2.5V FPGA电源轨之前上电(这超出了我的控制范围)。这会以奇怪的方式导致2.5V FPGA电源轨斜坡,请参考附图。基本上2.5VFPGA

2020-07-30 09:51:29

/ axigpio_v2_0.tcl中有一个额外的']'是第246行的结尾在GPIO2接口上添加三态GPIO端口时会导致错误。以上来自于谷歌翻译以下为原文There is a small bug

2019-04-19 10:32:27

1、AD5420的SDO是否是三态输出脚

2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正确

2023-12-20 08:08:51

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?

现在问题是FPGA引脚不够用了,能否将两片AD9280数据D0-D7接在一起,时钟是共用的,两片AD同步输出,在数据开始输出后用三态引脚控制取数?

2023-12-14 06:49:33

not directly control the tri-state conditionof the SDOUT or SDIO output,尊敬的专家,如果CS没被选中,SDOUT是否是三态状态?在CS拉高后,SDOUT是否会立马变为三态?

2019-05-23 08:07:10

CPLD/FPGA实现I2C的透传,使用三态门,那么SDA的方向应向该如何确定?assign SCL_OUT = SCL_IN;wire mid;assign mid = dir?1'bz

2019-01-11 09:49:55

我正在寻找在Spartan 3A中使用多路复用器与三态缓冲器之间的比较。从某个区域和时间角度来看哪个更好?谢谢,戴尔以上来自于谷歌翻译以下为原文I'm looking for a

2019-01-16 10:37:07

PSoC Creator组件数据手册/PSoC 4:三态缓冲器 (Bufoe) 组件是非反相缓冲器,其使能信号高电平有效。当输出使能信号为真时,次缓冲器用作标准缓冲器。当输出使能信号为假时,次缓冲器关闭。

2013-07-03 11:15:11

如下图,这是一个RS485芯片与单片机连接的典型电路,通常我们用一个IO口来控制485的发送与接收选择引脚。那么隐患在哪里呢?在单片机的接收引脚RXD上。当单片机发送数据时方向控制引脚DIR变高,使

2021-11-26 08:04:17

位寄存器和一个存储器,三态输出功能。 该设备具有串行输入(SER)和串行输出(Q7S)来级联和异步复位输入SCLR的功能。移位寄存器和存储寄存器时钟都是分开的。在移位寄存器时钟(SCK)的上升沿时,SER上的数据会被移入移位寄存器,在存储寄存器时钟(RCK)上升沿时,移位寄存器里的数据传输到存储寄存器,

2021-12-06 07:56:36

1 )程序加载前,非配置相关的 IO 处于三态弱上拉,配置专用管脚处于工作状态,配置复用管脚与配置模式设置相关。 2) 程序加载时,非配置相关的 IO 处于三态弱上拉,配置专用管脚处于工作状态,配置

2022-10-27 07:54:59

inout Key_inout;wire Key_input;//输入reg Key_output;//输出reg Key_Ctr;//三态控制assign Key_inout=Key_Ctr

2014-09-23 15:34:43

如果:红色-0,绿色-1,蓝色-2

输入:数组

输出:布尔数组或簇

例如:输入数组为〔0 1 2 1 0〕

希望输出显示为红色,绿色,蓝色,绿色,红色的一组三态灯。

网上给的子vi是利用bool引用句柄实现一个灯的三态显示,如果数组元素少的话用枚举可以实现,但是如果数组元素很多,有什么简便的方法吗?

2015-12-09 14:32:54

等,要求信号为三态类型,也就是我们所说的输入输出(inout)类型。那么,本节梦翼师兄将和大家一起来探讨三态门的用法。项目需求设计一个三态门电路,可以实现数据的输出和总线“挂起”。系统架构 模块功能

2019-12-12 16:11:51

本帖最后由 gk320830 于 2015-3-4 23:25 编辑

【经典】集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

2012-07-29 21:17:03

如下图所示,电路由两片带三态输出的EPROM组成。存储单元由地址总线提供的地址A0 ~ A7选择,而输出的数据是EPROM-Ⅰ和EPROM-Ⅱ的内容则由三态输出控制CS选择,CS=0时EPROM-Ⅰ输出,EPR...

2021-04-15 07:30:26

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?现在问题是FPGA引脚不够用了,能否将两片AD9280数据D0-D7接在一起,时钟是共用的,两片AD同步输出,在数据开始输出后用三态引脚控制取数?

2019-01-09 09:30:29

在输入时读入外部电平用.1. 三态门的特点三态输出门又称三态电路。它与一般门电路不同,它的输出端除了出现高电平、低电平外,还可以出现第三个状态,即高阻态,亦称禁止态,但并不是3个逻辑值电路。 2.

2008-05-26 13:01:37

与非门、一个与门及场效应管驱动电路构成。有一定的数电基础可以分析得到:当Vgs大于一定值,场效应管导通。先分析内部结构:1.输入缓冲器:在P0口中,有两个三态的缓冲器。三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态)。读取D锁存器输出端Q的数据,

2021-12-07 07:12:40

三态LED 子vi

2017-01-13 10:39:39

设计上,它会成为一个错误!对我来说,三态使能引脚没有连接到芯片上的引脚,不是它是一个输出,所以它没有转换约束,测试设计没有用户约束文件,只是选择IO向导为选择IO IP制作的文件, 所以我在xilinx

2020-08-05 12:07:55

必须是明确的。 OFDDRSE元素可用于IOB中的数据路径,但我找不到更“完整”的元素,其中还包含三态路径(OFDDRTRSE只有简单的三态路径)。我尝试使用OFDDRSE并使用它来控制三态上的启用

2019-05-13 08:41:11

]set to input with tri-state,我给芯片配置完之后,只需要将DO(数据)引脚设置输入就行了吗?不太懂这里的输入三态啥意思?[size=18.6667px]而且,时钟线应该没啥

2017-03-29 10:29:23

如何才能制作一个三态指示灯?需要什么材料等等

2014-10-28 19:51:17

第一图的稍微修改一下很容易实现3种状态,就是分别用光耦驱动2个三极管,三极管的集射极并联2个等值电阻即可,管压降难免,如果有绝对电压要求的话继电器较合适,从描述的要求来看。这个电路设计同时隔离了...

2021-11-10 08:32:28

反相器的速度与哪些因素有关?什么是转换时间和传播延迟呢?怎样去设计一种CMOS三态缓冲器的电路呢?

2021-10-20 06:24:39

怎么实现楼宇对讲系统中音频电路的设计?怎样设计通话电路达到高租态呢?

2021-06-04 06:01:30

要找一个7路输入/输出并带高阻的三态输出的逻辑IC,体积要小点的,有知道的请推荐一下,谢谢!!!积分只有13分,全给了。

2016-01-04 11:36:40

如图一中,unused pin是配置为“三态输入输入”,还是“三态输入加弱上拉”。图二中,为什么要把这些dual_purpose_pin设置为“use as regular IO”.他们可是专用的引脚的啊

2018-07-11 23:35:47

1.有源晶振有4个引脚,无源晶振是2个引脚2.有源晶振上电就可以震荡,无源晶振需要精确匹配的外围电路如下 ,有源晶振 O322525MEDA4SC,上电即震荡,VC脚为实现三态enable功能

2022-02-25 06:53:38

原理如图。这两天遇到了这么一个情况,问题好几个:1、MCU是刚刚焊上去的,没有程序,根据MCU硬件配置,该电路控制IO应该是三态。 2、给电路板上电,用万用表测D极电压约为1.6V,并逐渐上升,经过

2019-03-07 09:16:26

门电路的三态包括哪些?门电路OC、OD和OE开路输出概念是什么?拉电流和灌电流分别是什么意思?

2021-10-08 07:53:24

(SCLK)H/L使能信号7DB0H/L三态数据线8DB1H/L三态数据线9DB2H/L三态数据线10DB3H/L三态数据线11DB4H/L三态数据线12DB5H/L三态数据线13DB6H/L三态数据线

2013-11-05 11:42:20

信号7DB0H/L三态数据线8DB1H/L三态数据线9DB2H/L三态数据线10DB3H/L三态数据线11DB4H/L三态数据线12DB5H/L三态数据线13DB6H/L三态数据线14DB7H/L三态

2013-11-05 11:44:40

我有一个使用MCLR作为输入的项目。用PICTIT2 MCLR放在编程后的三态,但是用皮卡4,似乎PIN保持高。这有什么设置吗? 以上来自于百度翻译 以下为原文 I have a project

2018-10-26 16:11:59

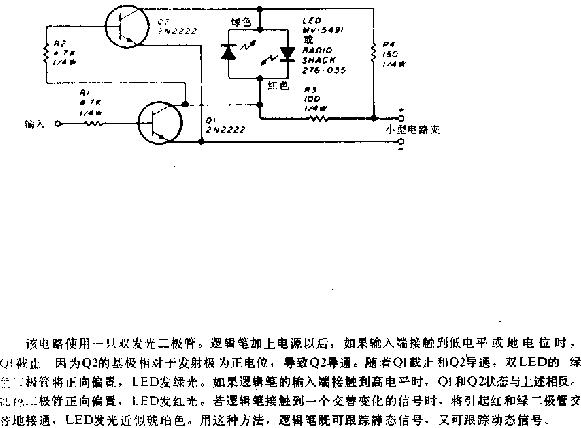

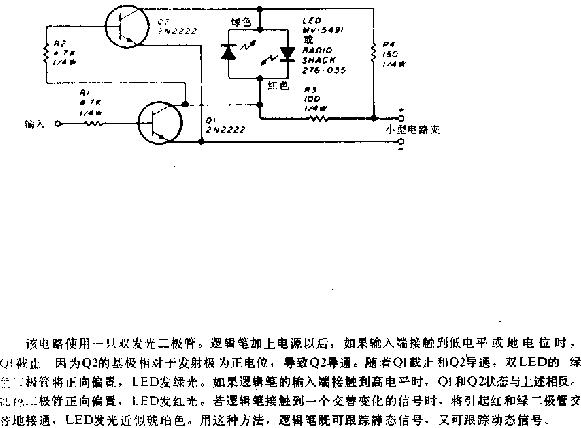

描述PCB_三态极性指示器使用 1K 电阻 (x2) 和任何硅二极管。顶部的绿色 LED 底部的红色。使用厚二极管腿作为探针和带有鳄鱼夹的接地线。

2022-08-30 07:31:27

新人在工作中经常碰到三态门与高阻态;请教技术大佬,这两个到底是什么东西 ?

2021-04-07 06:59:01

1、AD5420的SDO是否是三态输出脚2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正确

2018-12-20 09:26:31

ISIM不能处理1Mb信号)。我也测试了它,用逻辑分析仪我可以看到信号,地址和写入数据是正确的,时间也很好,但读数不对。我的猜测是它与双向数据总线有关,我知道内部三态在spartan-3上不再可用,但我

2019-06-26 10:24:04

请问这个三态门为什么不能实现非功能?它的逻辑表达式不应该是A非吗?

2023-04-26 11:49:06

请问这个三态门为什么不能实现非功能?它的逻辑表达式不应该是A非吗?

2023-05-10 17:44:20

信号的引脚出于三态,使能引脚对于这个三态(类似悬空)也有可能被开启。因此,猜想在背光芯片的输入端所使用的10uF电容是否太小,如果加大这个电容应该就可以大大延缓背光芯片的输入电压的时间,从而即便在复位

2011-07-21 08:49:22

GPIO输入具备缓冲功能,输出均具有锁存功能GPIO一般具有三态:0态、1态、高阻态启动总线:SCL保持高电平时SDA由高转为低终止总线:SCL保持高电平时SDA由低转为高数据传送时高位在前,低位

2021-12-23 07:27:59

74LS125 1块双全加器 74LS183 1块实验报告要求1. 画出实验逻辑图, 列出实验数据表格, 填入实验结果, 并写出各种门电路的逻辑函数表达式或逻辑功能。2. 叙述在与非门、或非门、异或门、三态门实验中用示波器观察方波波形的结果,并说明原因。

2008-09-25 17:28:34

:(1)门导通,输出低电平。(2)门截止,输出高电平。(3)禁止状态或称高阻状态、悬浮状态,此为第三态。一个简单的TSL门的电路如图2-15所示,它和普通与非门不同的地方是输入端多了一个控制端(又称使能端

2009-10-20 09:50:53

集成逻辑电路、组合逻辑电路实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法

2008-12-11 23:36:32

集电极开路 漏极开路 推挽 上拉电阻 弱上拉 三态门 准双向口

2016-06-02 16:22:21

高阻态和三态门高阻态 高阻态的实质:电路分析时高阻态可做开路理解。你可以把它看作输出(输入)电阻非常大。他的极限可以认为悬空。也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际

2019-01-08 11:03:07

数字电路常见术语:高阻态,三态门高阻态常用的表示方法

2021-03-01 11:09:49

悬空,顾名思义,就是不接任何器件啦高阻态:无上拉和无下拉,对外表现出电平不确定性不是所有的单片机都支持三态输出。三态输出一般由寄存器控制,需进行配置。高阻态既然无确定电平,怎么能做输出呢?把一个端口

2021-11-24 08:19:25

本文就三态电路在FPGA中的应用作了详细的说明。文章首先描述了一个调用lpm中三态电路模块的VHDL程序,这个程序会出现编译不能通过的问题。然后从这个问题出发,通过尝试三态电

2010-08-06 16:56:22 27

27 什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2008-05-26 12:48:24 42945

42945

三态逻辑笔电路图

2009-04-07 09:16:34 1614

1614

三态声光逻辑笔电路图

2009-05-19 13:42:17 705

705

三态门在数字电路上可以说是应用的非常广泛,特别是一些总线上的应用,因而,随着数字电路的发展,就避免不了用硬件描述语言在FPGA上来设计实现三态门。

2017-02-08 11:37:06 7305

7305 三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了三款三态门逻辑电路。

2018-03-01 14:03:10 73763

73763

本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与三态门电路的图形符号与真值表。

2018-03-01 14:47:41 119566

119566

电子发烧友App

电子发烧友App

评论