前言

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。时钟作为数字系统中的“心脏”,其设计的质量好坏直接关乎整个系统的稳定性,本文主要介绍了数字设计中的常见的时钟产生电路和时钟类型,并进行相关分析简介。

时钟产生电路

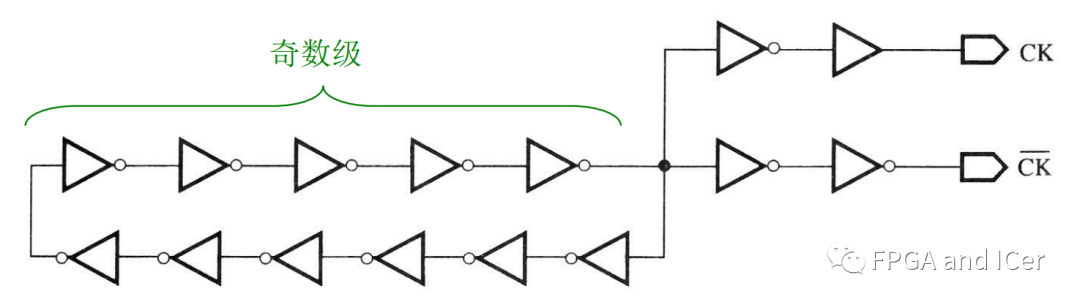

奇数个反相器首尾相连即构成环形振荡器(简称 「“环振”」 ),每个反相器两端出现周期性振荡信号。

环形振荡器

假定每个反相器都相同,所产生的时 钟周期T或频率f取决于反相器链的级数N和反相器的传播延时tp

可通过改变反相器的级数以及每个反相器的面积来改变输出的时钟频率。

「环形振荡器的优缺点如下:」

「优点:」 电路简单,无需外接元器件,完全片上集成。

「缺点:」 频率精度差,随工艺、电源电压离散的变化大;频率稳定性差,随时间、 温度的变化大。

针对该时钟的特点,因此该时钟适用于对精度和稳定度要求都不高的片上时钟产生器。

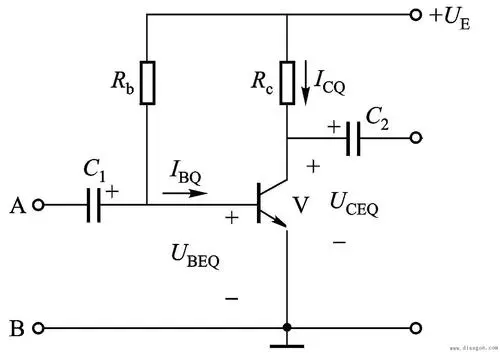

晶体振荡器

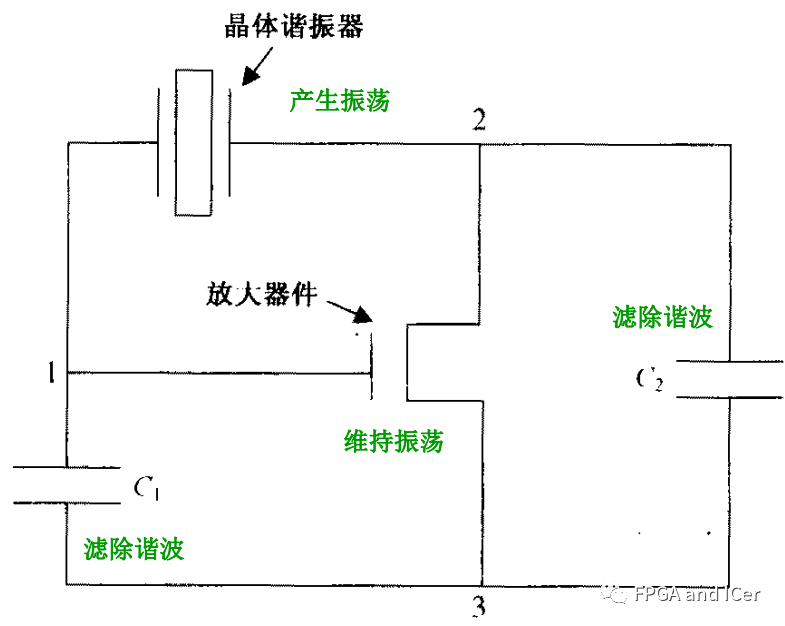

晶体震荡电路主要构成如下,主要由晶体谐振器产生震荡,电容进行滤除振荡产生的谐波,放大器将筛选出的频率进行维持并进行放大,从而产生稳定的时钟信号。

石英晶体两端加上电压后,就会产生振荡电流(机械能 电能),振荡频率由晶体的尺寸与形状决定(晶体越薄越小,频率越高)。

「晶体振荡器的优缺点如下:」

「优点:」 晶体振荡器频率稳定性高,可达10 ^ -6 (ppm), 而环形振荡器只能达到 10 ^ -2(ppm)。

「缺点:」 晶体振荡器输出频率范围一般不超过100MHz,难以满足现代高速数字IC的更高时钟频率要求;而且采用非硅工艺的石英谐振器,无法片内集成;输出频率难以调节,只能产生单一频率。

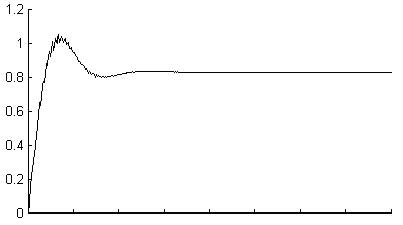

PLL锁相环电路

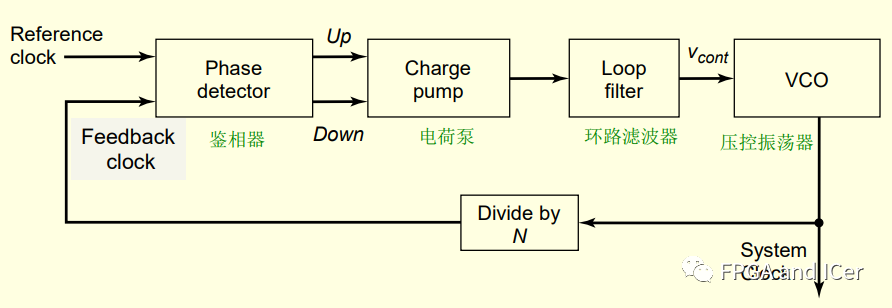

锁相环 (PLL) 是一种反馈电路,且为模拟电路,性能受工艺、电源噪声、温度等的 影响显著,设计难度较大。

PLL电路的工作原理是将外部信号的相位与压控晶体振荡器 (VCXO) 产生的时钟信号的相位进行比较。然后,电路调整振荡器时钟信号的相位以匹配参考信号的相位。因此,原始参考信号和新信号彼此是精确同相的。

PLL锁相环电路

一个锁相环PLL电路通常由以下模块组成:

「鉴相鉴频器PFD(Phase Frequency Detector):」 将分频后的反馈时钟与参考时钟的相位进行比较,若反馈时钟滞后/领先参考时钟,则发生一个Up/Down信号。该信号的大小正比于所检测到的相位差。

**电荷泵: ** 电荷泵将Up/Down信号转换为一个较大/较小的模拟控制电压Vcont,以便加速/减慢VCO, 从而消除反馈时钟与参考时钟的相位差。

「低通滤波器(环路滤波器)LPF(Low-Pass Filter、Loop Filter):」 用于滤除Vcont中的高频成分并平滑其响应,减少本地时钟的抖动。

「压控振荡器VCXO(Voltage Controlled Oscillator):」 压控振荡器产生系统时钟信号,信号的频率受输入电压Vcont的控制。利用变容二极管(偏置电压的变化会改变耗尽层的厚度,从而影响电容大小)与电感构成的LC谐振电路构成,提高变容二极管的逆向偏压,二极管内耗尽层变大,电容变小,LC电路的谐振频率提高,反之,降低逆向偏压时,二极管内电容变大,频率降低。

DLL和PLL具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。DLL即Delay Lock Loop,主要是用于产生一个精准的时间延迟,且这个delay不随外界条件如温度,电压的变化而改变。PLL利用压控振荡器调整频率来改变相位,DLL利用压控延迟线调整延时来改变相位。

DLL调整相位的方法是用压控延迟线(VCDL,Votage-Controlled Delay Line)而非 VCO,通过改变延时而非频率。

「PLL/DLL电路的优缺点如下:」

「优点:」 稳定性好,无需积分运算,极点少;锁定速度快,PLL需要先锁定频率再锁定相位,DLL直接锁定相位;抗抖动与噪声性能好,无环振VCO 那样的反馈路径,对工艺与环境波动不敏感;可直接产生多相时钟。

「缺点:」 无法改变输出频率,不能倍频,不 能产生多个时钟频率;调节范围较大时,可能产生错误锁定。

时钟类型

全局时钟

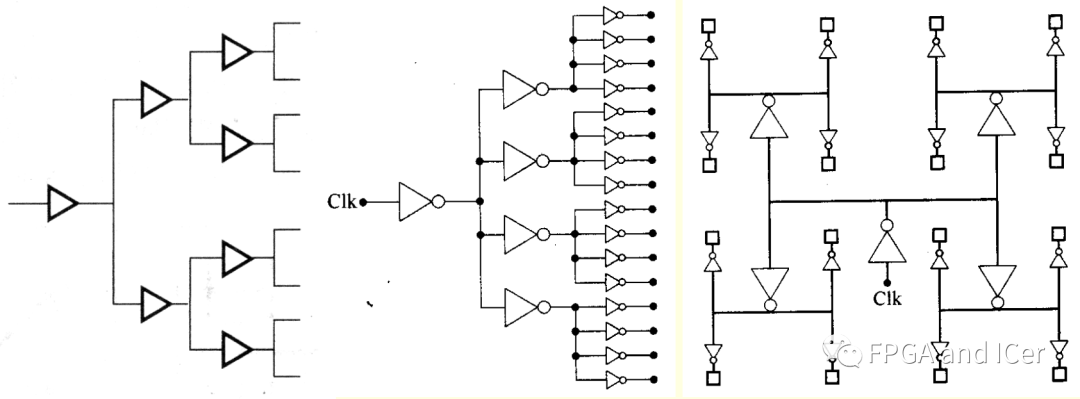

全局时钟(Global Clock)。一般的时钟都指的是全局时钟,全局时钟在芯片中的体现形式是时钟树。

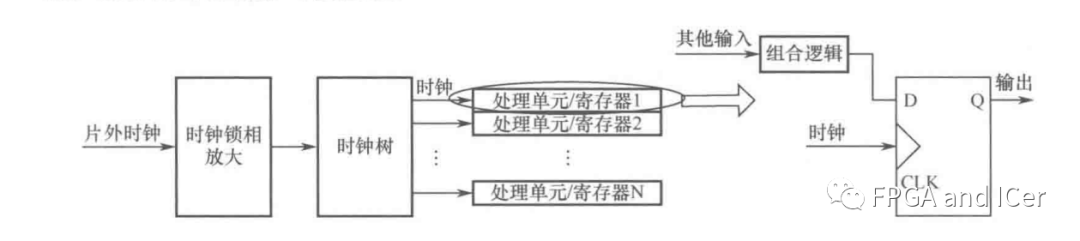

时钟树

它是由片上的时钟管脚引入,经过锁相和放大之后进入时钟树,输出给寄存器的稳定、可靠的时钟信号。这种时钟的时延通常被设计得最小,相对抖动也最小。

内部时钟

对于内部时钟最早的接触应该就是使用计数器输出的计数值的相关逻辑做分频时钟。但如果设计不当,该部分会导致设计功能和时序问题。组合逻辑电路的常见的引起设计错误的问题:毛刺和延时,同时也是组合逻辑搭建的时钟所面对的问题。往简单了说,组合逻辑的毛刺会引起功能的异常,降低系统的稳定;延时会引起在时钟进行时序分析的相关问题,下面就这两方面进行说明。

组合逻辑搭建的时钟产生器会引入毛刺,使功能出现问题,此外由组合逻辑所导致的延迟也会导致时序方面的问题。在同步设计中,数据输入端的毛刺不会引起任何问题,因为数据是在时钟边沿处捕获的,所以可以将毛刺自动滤掉。然而,如果毛刺或尖峰脉冲出现在时钟输入端(或者寄存器的异步输入端)就会产生明显的影响。

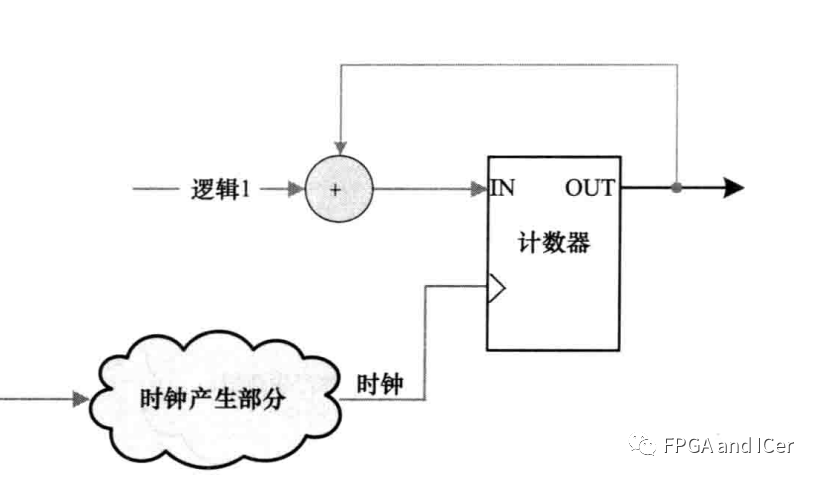

下图通过逻辑设计产生了时钟,时钟产生部分包含一些组合逻辑,而计数器的寄存器是对边沿敏感的,这就导致下图的设计毛刺会明显影响到计数器的值。

逻辑设计时钟产生

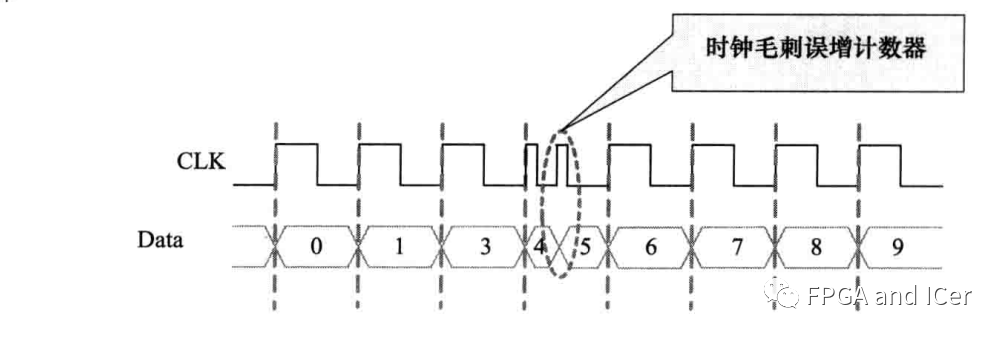

在下面这个例子中可以看到,由于时钟沿处的毛刺,计数器在所示的时钟周期上递增了两次。由于时钟毛刺的作用,计数器增加了额外的计数值,这样就可能导致功能出现问题。

毛刺导致逻辑错误

窄毛刺会违背寄存器的最小脉冲宽度要求。在毛刺到达时钟输入端时,如果寄存器的数据输入变化,会违背建立和保持时间。即使设计没有违背时序要求,寄存器也可能输出意料之外的值,使整个设计功能出现风险。

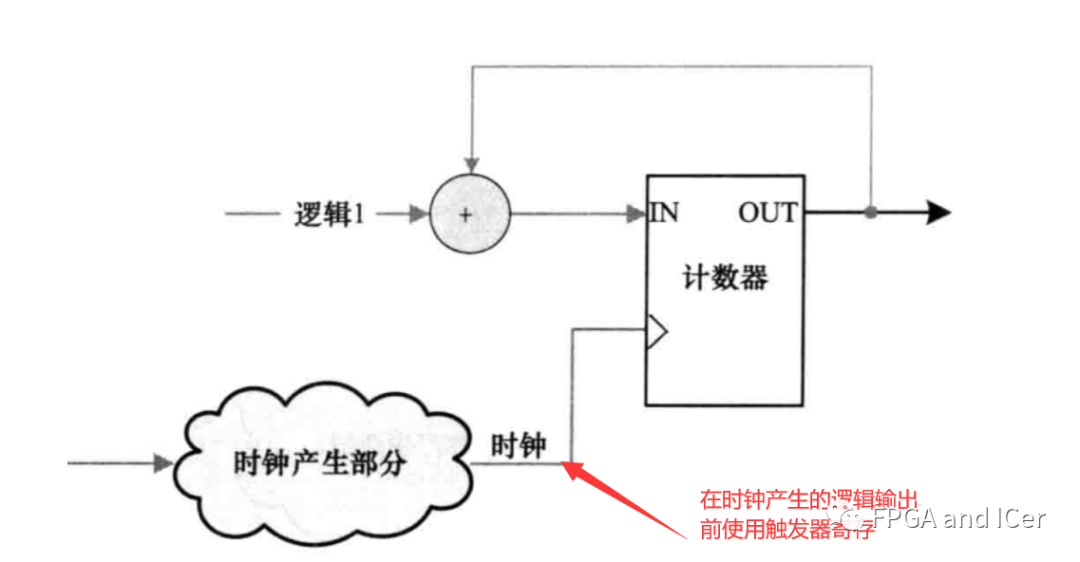

解决毛刺引发的设计功能问题,最简单的办法就是使用寄存器在时钟产生逻辑后寄存输出,这样无论前级的时钟产生部分的代码是否存在毛刺,都使用触发器做了寄存,降低了毛刺引起功能错误的风险。

解决方法

分析完毛刺的影响,下面分析下组合逻辑构建的时钟引入的延迟问题。

用来产生内部时钟的组合逻辑也会增加时钟线上的延迟。在某些情况下,时钟线上的逻辑延迟会导致时钟偏移比两个寄存器之间的数据路径延迟更大。如果时钟偏移大于数据延迟,就会违背寄存器的时序要求,设计的功能也不会正确。

因此,就需要设计时钟时尽量减少时钟偏斜,一种减少时钟偏移的方法是将产生的时钟放到SoC中高扇出且低偏移值的时钟树上。「使用低偏移值时钟树有助于减少信号整体的时钟偏移。」

分频时钟

许多设计需要来自于主时钟的分频时钟。在设计中要保证大多数时钟来自于PLL。使用PLL能避免由异步时钟分频逻辑引起的许多问题。在对主时钟进行分频时,应该始终使用同步计数器或状态机。

此外,设计应该保证总是由寄存器直接产生分频时钟信号。不要对计数器或状态机的输出进行解码,然后产生时钟信号;这种实现方式常会导致毛刺和尖峰脉冲。可参考内部时钟的举例。

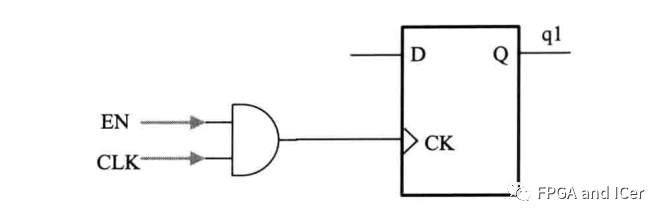

门控时钟

门控时钟的时钟线上的门控单元会导致时钟偏移,并会引入尖峰脉冲作用于触发器。但在涉及到低功耗设计时(通常ASIC中),门控时钟还是比较常用的。

门控时钟

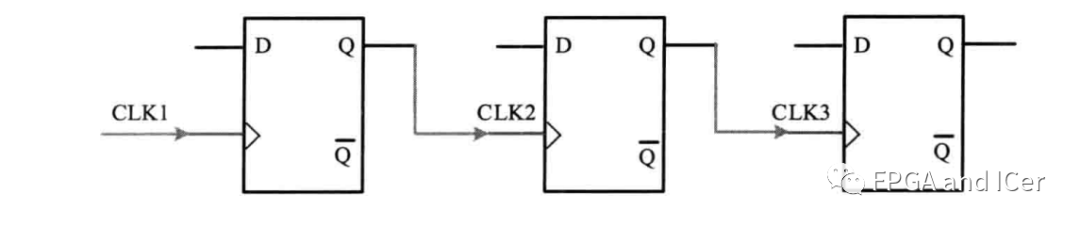

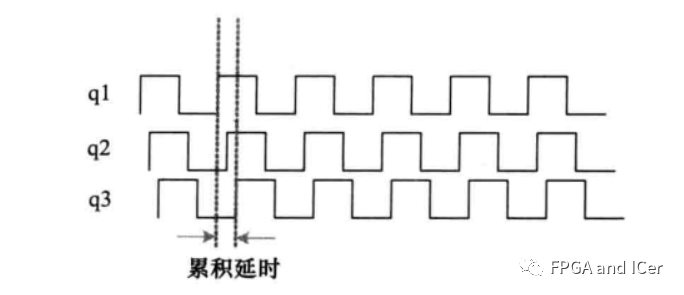

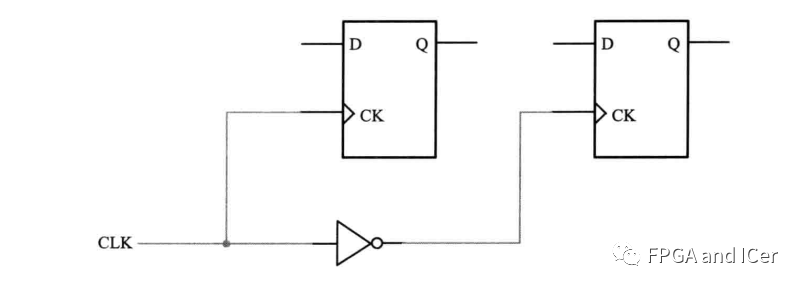

行波时钟

行波计数器:将触发器前级输入引脚连接至下个寄存器的输入引脚,依次级联。由于第一个触发器时钟到Q的延迟而使第二个触发器的时钟输入产生偏移,而且不能在每个时钟边沿都激活。此时,延时逐渐累积会在引入时序分析和综合麻烦,因此需要尽量避免使用这种结构,

行波计数器

积累延时

尽管使用行波计数器(或者行波时钟)存在各种问题,但是在功耗较高的系统中很适合使用这种计数器,因为这样能大量降低由逻辑或SoC所引起的峰值功耗。

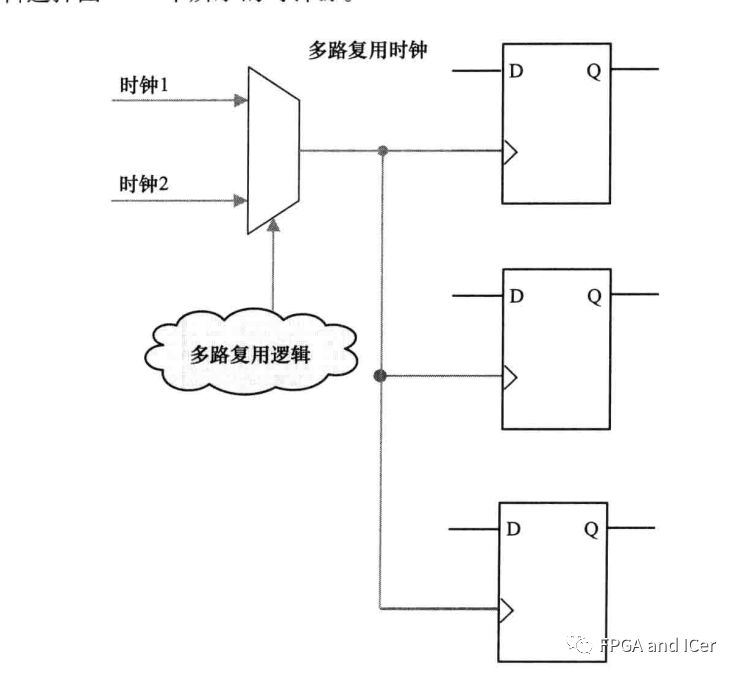

多路时钟

时钟多路器用于使同一个逻辑功能具有不同的时钟。某些类型的多路逻辑选择如下图所示的时钟源。

多路逻辑选择时钟源

例如,需要处理多个频率标准的通信应用常常使用多个时钟。虽然在时钟信号上引入逻辑上的问题,是在不同的应用中对多路时钟的要求差别很大。

在能满足下面的标准,时钟多路操作就是可接受的:

在初始化配置后,时钟多路逻辑就不再改变。

在测试时,设计会绕过功能时钟多路逻辑而选择普通时钟。

在时钟切换时,寄存器始终处于复位状态。

在时钟切换时产生的短暂错误响应没有负面影响。

如果设计中时钟切换很频繁,并且不在复位时切换,设计也不能容忍芯片中出现短暂的错误响应,就必须使用同步设计以确保寄存器没有违背时序,时钟信号上不出现毛刺同时没有竞争条件或其他麻烦。

为了实现时钟切换,在xilinx的原语中,存在CLK选择的结构以供设计者进行选择设计,按下面的原语示例,设计时需要控制信号S满足建立时间和保持时间,可实现时钟的无毛刺切换。

BUFGMUX #(

.CLK_SEL_TYPE("SYNC") // ASYNC, SYNC

)

BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

双边沿或混合边沿时钟

双边沿时钟是指在时钟的上升沿和下降沿都进行数据传输,两个触发器由两个相位相反的时钟信号控制。

双边沿或混合边沿时钟

这样操作会为使用同步复位和使用插入扫描链这样的测试方法带来麻烦,同时也会增加确定关键信号的路径的难度。

但双沿采样时钟也是有好处的。

双沿时钟使得原本一个周期输出/输入一个数据的架构,改变为一个周期输出/输入两个数据,这样在不升高时钟频率的前提下,提升了信号的吞吐率,从而带来「性能的提升」。另外一个使用双沿时钟的优势是「降低功耗」,因为时钟频率减半,所以系统的功耗只有等效同步电路的一半。

但一般情况下,不建议使用双边沿时钟,这是因为:

由于上下沿都用,要求时钟的质量很高,一般的时钟源很难达到,成本高。

由于时钟的抖动等不确定因素的存在,容易使时钟的占空比发生改变,因此容易引起建立时间和保持时间的违规。

❝

在FPGA中的通常高速传输时会用到双沿采样时钟,DDR存储同样也是使用的双沿采样,但在常规情况下不使用双沿采样时钟。

❞

编辑:黄飞

电子发烧友App

电子发烧友App

评论