ICARUS-Q:一种基于RFSoC的可扩展超导量子计算机控制系统

Park, Kun Hee ; Szen Yap, Yung ; Tan, Yuanzheng Paul ; Hufnagel, Christoph ; Hoang Nguyen, Long ; Lau, Karn Hwa ; Efthymiou, Stavros ; Carrazza, Stefano ; Budoyo, Rangga P. ; Dumke, Rainer

eprint arXiv:2112.02933,December 2021

摘要

本文基于Xilinx射频片上系统器件(RFSoC)给出了超导量子比特的控制和测量装置。装置分为四个部分:多个RFSoC FPGA板、多板DAC和ADC通道同步装置、给量子位提供偏置的低噪声直流电流源以及用于支撑远程实验的云访问能力。该系统不需要微波混频器。FPGA板的16个DAC通道在第三Nyquist区直接生成微波脉冲,八个ADC通道则在第五和第九区之间直接采样。

I. 概述

稀释制冷机中的超导量子比特需要依靠工作在室温中电子器件来控制和测量。典型的超导量子比特的跃迁能的变化频率为GHz量级,需要可变且精准的微波信号生成和检测来进行控制和测量。量子比特的数量增加时,需要的微波通道数量也线性增加。所以,必须设计一个可扩展、紧凑、有性价比,同时保有精度、速度和功能的量子比特控制系统。

除了传统的上下变频的微波电路外,基本量子比特控制系统还有由数模转换器(DAC)、模数转换器(ADC)和恒流源组成的;DAC生成的微波脉冲会进入制冷机,ADC把从制冷机出来的模拟信号数字化,电流源给量子比特提供偏置。一些早期的用于电子旋转和超导量子比特的微波控制系统选用台式的任意波形发生器(AWG)来生成微波[2-7]。而近来大家更喜欢使用现场可编程门阵列FPGA[8-15],因为它的通道数更多(即每个通道的成本更低),功能多,形态也更灵活。一般来说,每个量子比特需要两个DAC通道来驱动;五个或以上的量子比特会共享一个额外的DAC通道,用于频率复用读出方案[16-18]。

Xilinx的FPGA家族——Zynq Ultrascale+片上射频系统(RFSoC)[19]拥有很多适用于量子比特的控制和测量的特色,包括:单个芯片内多路独立DAC和ADC通道、高采样率、通道间同步能力。该器件内部还具备包含正交混频器和48位数控振荡器的数字上下变频器。出于较高的集成度,RFSoC成本低、占用空间小,特别适合雷达[20]通信[21]和量子计算[22-24]等应用。

这里,我们基于多个互相同步的XCZU29DR FPGA板开发了一个可扩展系统,每个单板拥有16个6.554GS/s的DAC通道和16个2.058GS/s的ADC通道,工作时无需模拟I/Q混频器。

II. 实现

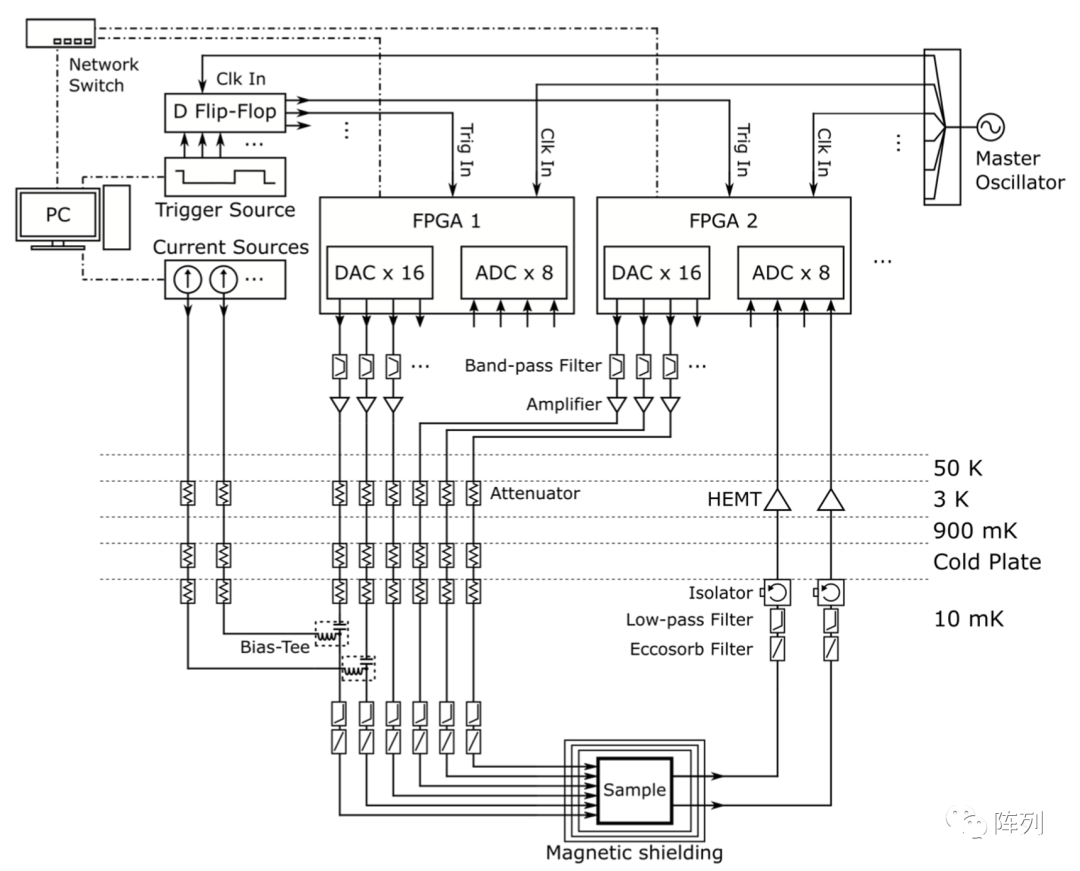

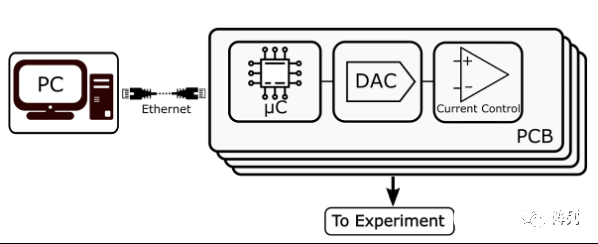

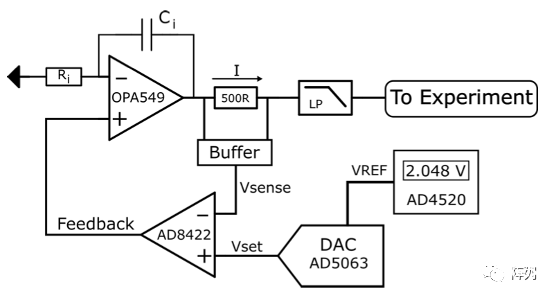

图1. 总体电路示意图

如图1所示,装置由若干部分组成。代号ICARUS-Q(可扩展量子处理器集成控制读出单元)的FPGA板,运行Linux嵌入式内核,通过以太网接收命令和收发数据。在实验中,DAC信号在高阶Nyquist区[13]的镜像实现GHz范围的量子位转换,并用ADC以较低采样率对高频信号直接采样。使用一个主振荡器和同步到该主振荡器的触发信号来让多个FPGA板相互同步。对于可调超导量子比特,约瑟夫森结用DC-SQUID环来替代。这让量子比特可用磁通量来偏置,该磁通量由靠近环路的一根电流线耦合过来的。为了支持这些特征,系统集成了低噪声DC电流源来进行量子位偏置。FPGA板、触发源和电流源都连接到计算机上。计算机上的监控程序负责与和云服务器通信以进行远程实验。

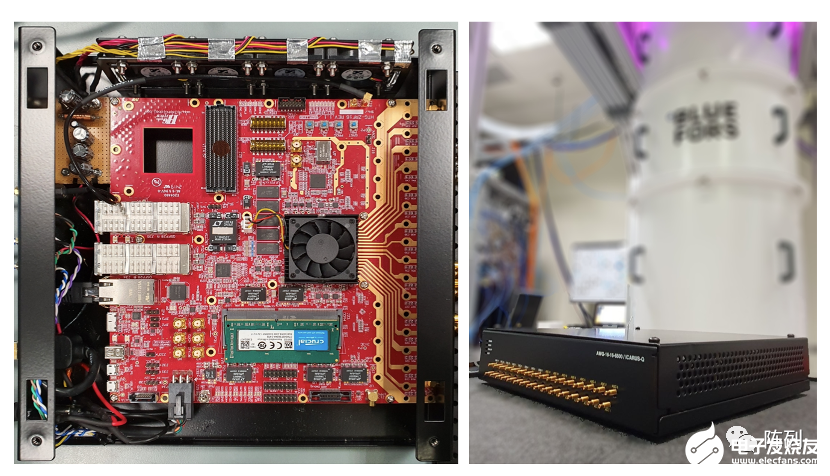

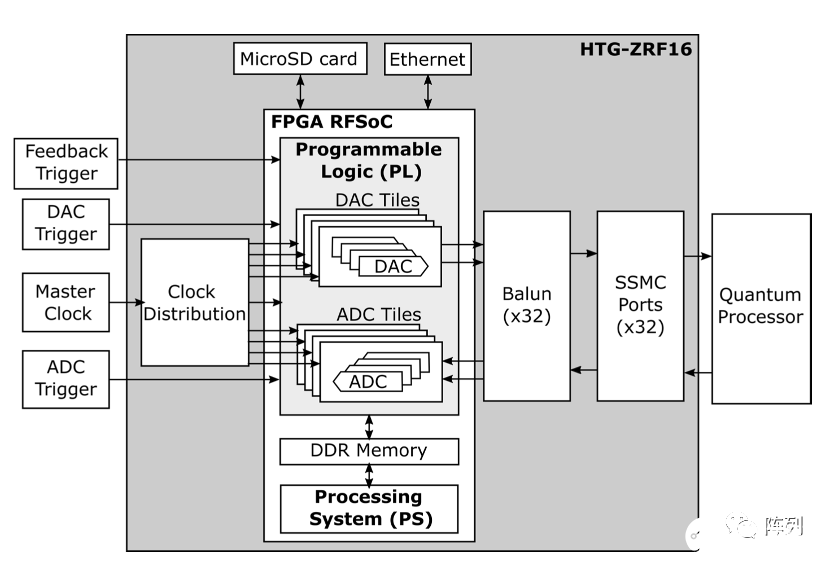

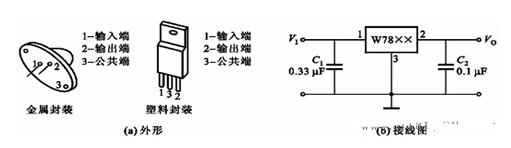

FPGA板采用货架产品,单板包含一片XCZU29DR RFSoC器件(图2)。该器件有16个十四位DAC差分接口和16个十二位ADC差分接口。所有DAC和ADC通道都使用巴伦(支持频率10MHz-8GHz)和SSMC端口(支持频率最高12.4GHz)转换成单端信号接口。

图2. ICARUS-Q的FPGA板

图3. FPGA板的框图和对外接口

在本装置中,需要的DAC通道比ADC通道多。为了把更多有限的FPGA BlockRAM资源分配到DAC,我们把ADC活跃通道的数量减少到8个。FPGA板也有固定内存(4G)和SODIMM DDR4模块(可达到16GB),在目前的设计中并没有用到。

A. FPGA逻辑

FPGA逻辑负责让数据在计算机和量子处理器之间流动(图3)。在外触发的激励下,ADC和DAC执行数据和信号之间的转换。系统中包含一个二级时钟分配逻辑,用于ADC和DAC的相位同步。FPGA还连接到以太网、micro-SD卡、板上的DDR内存等设备和接口。

1. DAC波形生成的FPGA逻辑

任意波形产生依靠RFSoC DAC实现(见图4)。芯片内的四个DAC片(DAC tiles)提供了总共16个DAC通道。为了在单个板内确保所有DAC的同步输出,利用RFSoC内的多片同步逻辑来校准片间传输斜移。

波形数据载入PL-DDR内存后,开始产生DAC数据流。PL-DDR内存是一个硬件SODIMM内存模块,和PL-FPGA相连。波形数据会进入每个DAC通道的AXI流型FIFO。由于内部BlockRAM的容量限制,单个FIFO能储存的每通道波形样本是65536个采样点。

DAC波形回放支持环回功能。启动后,它不需要从主机再次载入波形数据就能让波形重新载入到FIFO,从而减少了一下次DAC回放重启的时间。

波形数据载入到每个通道的FIFO后,系统会等待外部控制逻辑的外部触发事件,然后开始DAC波形回放。外部控制逻辑的触发信号适用所有DAC通道,所以所有信号可以从SSMC连接器同步输出。外部控制逻辑同样支持波形数据交换,8个上部通道的波形能交换到8个下部通道,以支持更高级的脉冲序列。

图4. DAC波形生成的FPGA逻辑

2. ADC波形获取的FPGA逻辑

波形获取系统由RFSoC的8个ADC通道构成(图5)。模拟输入通过SSMC连接器注入RFSoC的ADC。ADC持续地把输入波形数字化,并在外部触发信号驱动下流入AXI流型FIFO。

图5. ADC波形获取的FPGA逻辑

每当外部触发信号到达, 每个ADC通道的65536个数字化波形数据就会储存在FPGA的FIFO中。储存在FIFO中的数据会被转移到外部DDR4 SODIMM,等待ZYNQ处理器系统(PS)的后续处理。根据后续分析的设置,数据可以以HEX或ASCII的文件格式储存。获取的数据完全转移到ZYNQ处理器系统后,ADC会重新待命等待下一次触发。

B. 微波的生成和检测

DAC输出的任意波形由65536个样本以最大6.144GS/s的可变采样率生成。在最大采样率下,该数据量相当于波形时间长度约10μs。ADC会储存同样数量的样本,但是采样率为1.96608GS/s,相当于波形时长33μs。触发DAC通道后,会有最小30μs的延迟,然后再触发下一个脉冲。为了进一步评估DAC和ADC的性能,我们进行了相关的测试,以下是一些分析结果。

1. 任意波形生成

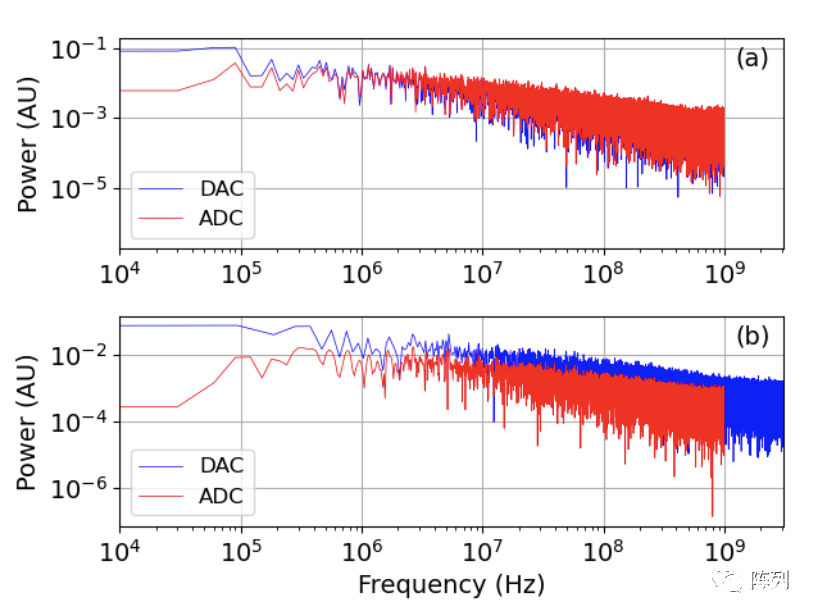

在一个典型的量子计算机实验装置中,通常会使用矩形或高斯形脉冲,但任意相位和振幅信号[27,28]的脉冲也会经常使用。一些量子信息处理应用要求使用无门控信号,比如最优控制理论[29-31]、绝热量子计算、持续可变量子计算等[32]。为了验证真实的任意波形生成能力,我们用粉红噪声测试了DAC,并把生成的信号和计算出来的波形数据点进行了比较(图6)。粉红噪声波形是用Voss算法[33]生成的,DAC以两个不同的采样率1.96608GS/s、6.144GS/s生成信号。两种波形都由ADC以1.96608GS/s进行采样。

图6. 粉红噪声的DAC生成和ADC采样效果

在图6(a) (b),DAC样本和ADC数据分别在频域内标出。除了1MHz以下,两个频谱包络基本吻合。这主要是因为电路中巴伦器件的支持频率范围是10MHz-8GHz,低于10MHz的频率都减弱了,类似于高通滤波器。在图6(b)中,当DAC以6.0144GS/s运行时,DAC噪声谱会达到3.072GHz的Nyquist频率,而ADC因为欠采样,其噪声谱只能达到983.04MHz。此外,以6.144GS/s生成的信号只持续10μs左右(其余的ADC数据都接近0),这让ADC频域幅度偏低。

2. 高Nyquist区的性能评估

Shannon-Nyquist采样理论指出可以在频率低于一半采样率的情况下正常生成或采样一个信号。这个频率阈值叫做Nyquist频率。离散时间生成或采样信号会产生镜像,这些镜像会在Nyquist频率的倍数范围重复反射展开[13,34]。频域的每一段通常被叫做一个Nyquist区。经过精心设计,可以在不升级现有器件的情况下利用第一区以上的频率区间[13,23,35]。

然而,其中会有一些掣肘因素。设时域内的电压为:

受到重建波形r(t)的影响[13],v(t)的傅里叶变换是:

其中,R(ω)是一个由DAC运行模式决定的sinc函数[36]。这里使用的RFSoC支持两个模式:非归零(NRZ)模式和混合模式。傅里叶空间中相应的重建波形是两个不同的sinc函数:

和

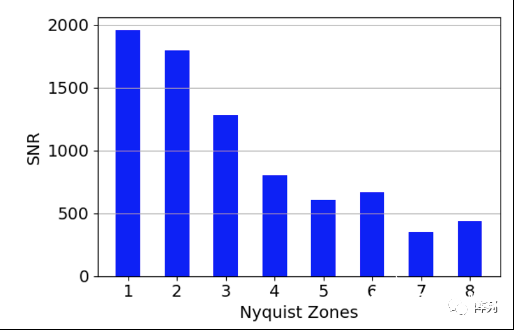

所以,使用ADC的高Nyquist区时,我们认为信噪比(SNR)会有一定程度的降低。为了研究这个问题,我们用ADC以1.96608GS/s去采样高频率区的各种信号,并在ADC的第一区内生成800MHz的镜像。我们比较了微波合成器生成信号和RFSoC DAC发出信号的SNR。在这些测试中,DAC模式被设为普通模式(NRZ)。

RFSoC DAC的800MHz信号在ADC采样率的第一Nyquist区,测得SNR≈2×10³(见图7)。7.06432GHz的信号,800MHz的第八Nyquist区镜像,在典型量子比特跃迁频率的相似范围。在这个频率下,测出的SNR约为4×10²,第一区800MHz低5倍左右。

图7. 用ADC测得的SNR

3. 功率和频率的关系

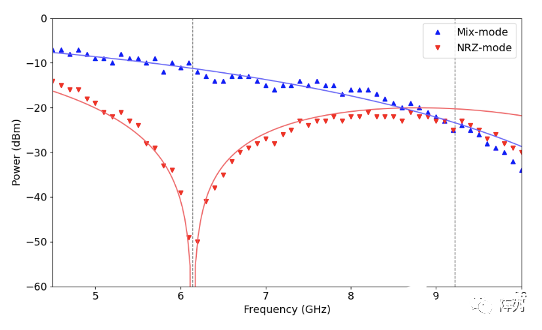

使用高Nyquist区的方法会导致信号功率与频率之间有关联。超导量子比特需要在特定的频率下控制和读出的。我们需要研究DAC Nyquist区之间的功率变化关系。我们使用谱频分析器测量了DAC输出功率,谱频分析器的范围是4.5GHz到10GHz,这是超导量子比特及其谐振器的典型范围[37,38]。结果如图8。虚线是实测结果,实线是理论参考值。

图8. 不同DAC工作模式的跨区间功率/频率特性

对于普通模式(NRZ),如我们所预料,输出功率在6.0144GHz时开始明显下降。在7-10GHz之间,平均功率是-24.1±2.4dBm;在7-9GHz之间(按照标准偏差),会略微上升到-23.1±1.5dBm。与微波合成器或高端任意波形发生器相比,这样的功率变化有点大,然而这种误差幅度不会造成很大问题,因为量子比特会在固定频率下周期性的被测量和校准。对于混合(Mix)模式,功率下降发生在12.288GHz(采样率的两倍)。这个模式的平均功率是7-10GHz之间-20.4±5.7dBm,7-9GHz之间-16.9±2.3dBm。输出功率实测值在高频率比理论值有明显下降,主要原因是板上巴伦的支持频率范围(10MHz-8GHz)较低。

C. 反馈控制

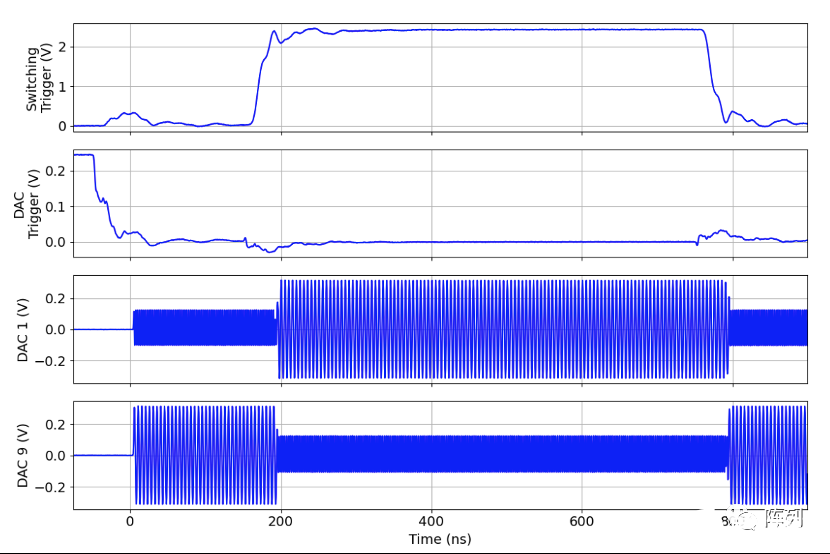

如果能实时切换波形(纳秒级别),就能在量子电路运行时纠正量子比特状态。RFSoC整合了硬件触发信号切换波形的能力。收到切换触发信号后,上部(0-8)DAC通道的输出会在几纳秒内切换到下部(9-16)DAC通道(图9)。使用快速读出系统来激活切换触发信号,纠正脉冲能根据量子比特状态发送到合适的通道。

图9. 用硬件触发信号进行DAC回放切换

D. 多通道和多板操作

多个DAC和ADC通道需要在时间和相位同步的情况下输出波形。我们必须做到两种同步:(1)板内、通道间同步;(2)板间同步。

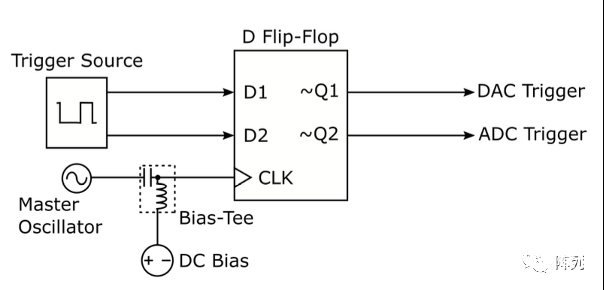

在板内,通道间同步是通过固件中的多片同步逻辑实现的,利用板上锁相环把通道输出锁到外部基准时钟。板间同步是通过把单个主振荡器分配给所有板,这样它们就有相同的基准时钟信号来进行同步。用DAC和ADC同步生成和采样波形,会用到硬件触发器。使用D型触发器把触发信号同步到基准时钟信号,这样,收到触发信号后,DAC(ADC)输出波形的时间是一致、可预测的。

图10. 同步电路

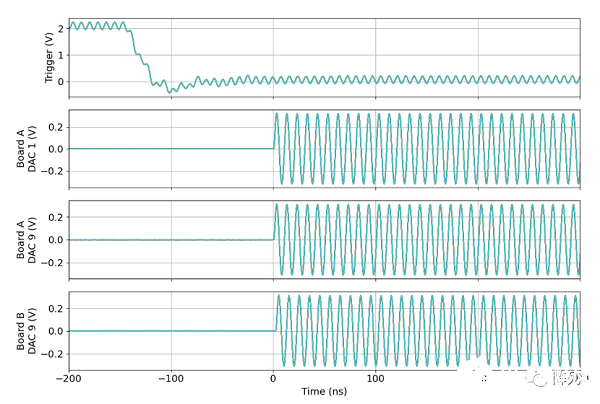

通过D触发器驱动多片同步逻辑和触发信号,两块RFSoC板上的DAC输出是同步的(图11)。触发信号中的振荡是时钟信号从触发器漏出造成的,但不影响RFSoC板的触发接收。板B的微延迟是触发分配路径的长度不同造成的——通过精确匹配缆线长度就能纠正(或者在软件中引入延迟)。

图11. 示波器测得的同步触发信号和多路DAC输出

E. 低噪声直流偏置电路

为了驱动用于调谐量子比特空闲频率的偏置电流,我们开发了一个低噪声双极性电源,可通过主计算机的软件控制。设计过程中我们考虑了这些因素:(1)超低噪声:电流中的任何噪声都会直接影响量子比特的相干性,电源的噪声应该尽可能小。(2)超低电流漂移:电流中的任何漂移都会直接改变量子比特的特性,所以应该抑制漂移。(3)电流带宽:基于设计,通过SQUID环的单位磁通量变化基本上会造成电流亚毫安到几毫安之间的变化。电流源的电流范围需要能够支持生成至少一个单位的磁通量。此外,电流源应该是双极的。(4)自动化:通过USB或以太网这样的标准协议能控制电流源,这样才能把它整合到软件工作流程中。

图12. 电流源的工作机理

1. 电流控制电路

在设计中,我们按照了文献39,并作了一些修改。图13是装置的简化图,为了表达更清楚,供电电源、去耦电容、连接器等都省略了。

图13.电流控制电路

电流控制器的核心是一个设置为积分器的运算放大器。使用取样电阻Rsense来取样放大器的输出电流,把电流转换成电压Vsense。电压Vset减去Vsense得到反馈信号,用于对电流的积分控制。此处,放大器自身就是一个积分器。电路的每个部分都必须低噪声、低漂移。为了取样电流,我们选择500Ω温度系数为±2ppm/℃的金属箔电阻。为了获取Vsense,首先使用零漂移运算放大器缓冲感测电阻的两端。

为了生成设定电压Vset,我们使用了分辨率为16位的串行接口DAC。并在双极模式下运行该DAC,可把输出电压设定为-Vref到+Vref。这里Vref是提供给DAC的基准电压。Vref要低噪声、低漂移,这非常重要,因为它直接影响输出电流。

2. 电流供给性能

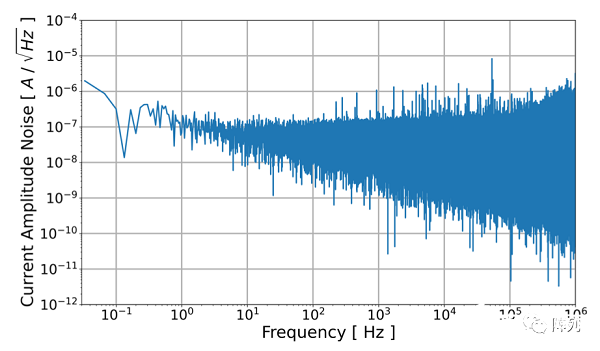

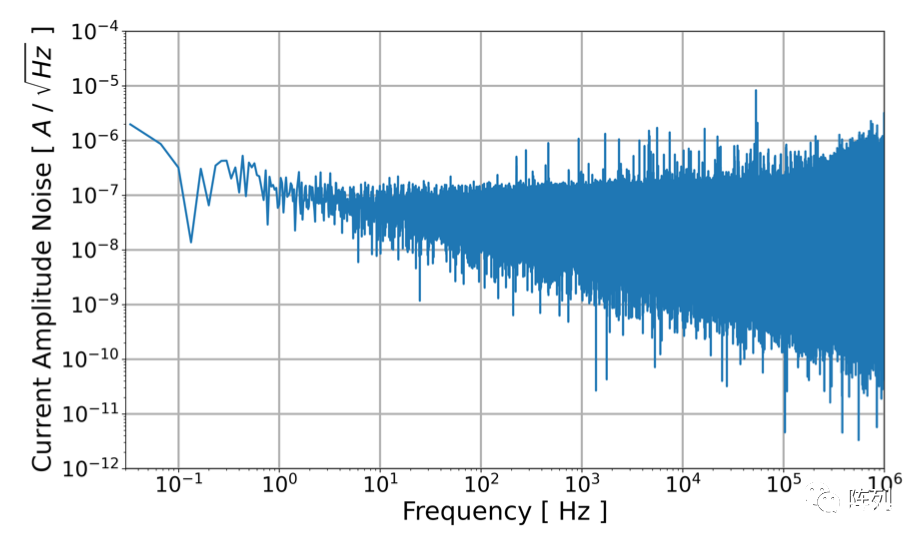

图14. 电流源的高频幅度噪音

为了确定电源的噪音和稳定性,对电流幅度噪音进行了测量,并通过测量电源的艾伦偏差来观察其长期表现。进一步的,我们通过调节超导量子比特的频率验证了电源性能。

把1mA的电流DC耦合到12位数字示波器的50Ω输入端,以此来评估电流噪音和艾伦偏差。为了确定电流噪音,测得电压以2MS/s的采样率和30s的测试时间数字化。示波器的幅度范围设为80mV,对应的电流分辨率为390nA。我们根据时域数据用快速傅里叶变换(FFT)计算了电流幅度噪音。图14显示了一个典型的电流幅度噪音频谱。

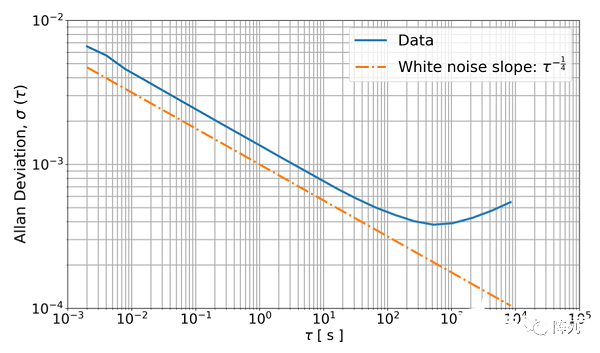

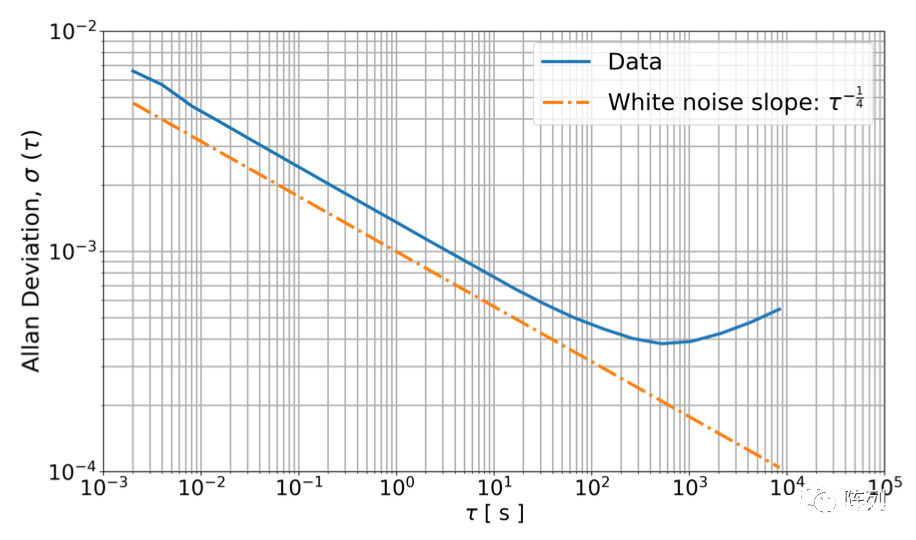

图15. 电流源的稳定性

为了评估电源的稳定性,我们以500S/s的采样率对电流进行了长期测量。示波器的满幅度范围设为40mV,对应的电流分辨率为195nA。根据时域数据计算了分数重叠阿伦偏差。图15(蓝线)显示了18小时长期测量的电流阿伦偏差。可以看出来,平均500s的时间,源的零偏稳定性约为4×10-4。为了比较,我们还绘出了白噪音源斜线(点划线)。对于较小的平均时间,电流源的阿伦偏差和白噪音是一致的。

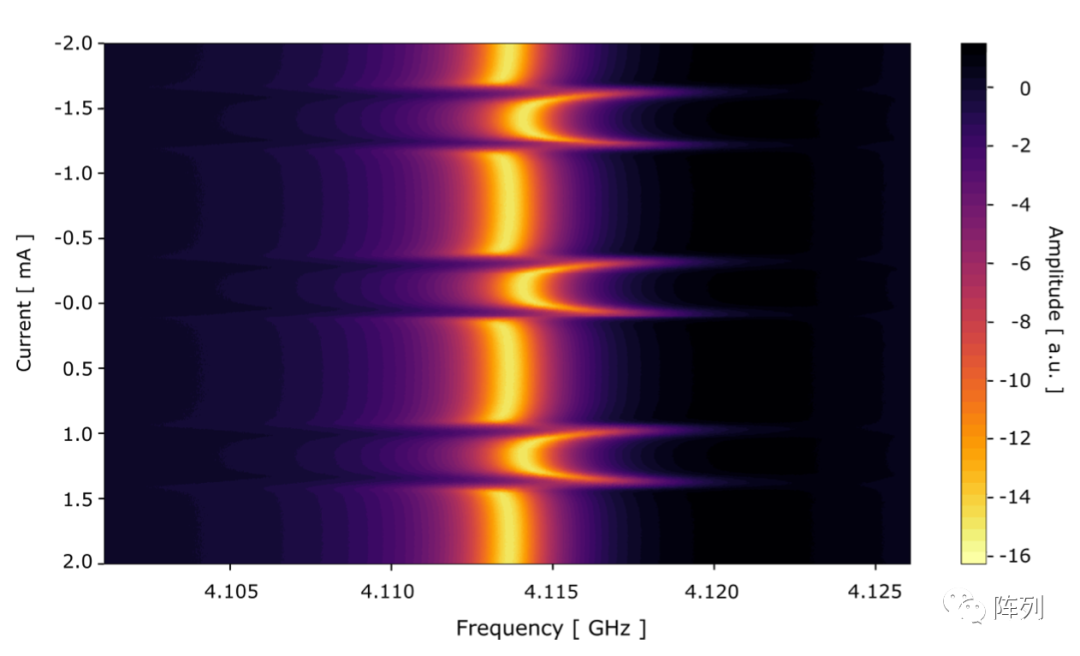

图16. 超导Transmon量子位在不同偏置电流下的透射谱

确定了电源的噪声表现后,我们测试了其偏置超导电路的能力。此例中,我们测量了一个腔的传输,这个腔被分散耦合到一个可调超导transmon量子位。由于是分散耦合,量子位频率的变化会直接造成腔共振频率的变化。我们测试了各种量子位偏置电流的腔透射谱。图16是电流范围-2.0mA到+2.0mA的腔透射2D图。可以看到,共振器的频率随施加的偏置电流而发生变化[40]。在测试的电流范围,我们观察到大概有3个量子位频率振荡周期。这说明该电源适用于线性偏置超导量子位,而且噪音很低。

F.软件控制和云访问

本节介绍基于云端的RFSoC脉冲序列控制软件的实现。

1. 软件控制

如第II部分所述,本项目中的RFSoC板具有板卡配置、外时钟锁定、通道同步、FPGA启动等命令。

这些命令由一台中央计算机通过SSH协议执行。我们定义一个叫IcarusQ的Python类来完成用户自定义波形数据的注入RFSoC、处理来自ADC的数据以及执行其它命令。这个类就成为了远控端与RFSoC之间的接口。因为是Python写的,所以可以与Python下的各种仪器包,例如PyVISA[41]、QCoDeSp[42]和PythonIVI[43]等,一起使用。

工作软件与其它设备,例如RFSoC板的触发源,通过特定的接口连接,能够触发ADC和DAC工作。在其上有定义了一个Python函数IcarusQ-Executor来运行脉冲实验。该函数先设置用户自定义触发时序、重复次数和脉冲序列。然后,它启动设备工作并且发出脉冲序列。最后,它返回FPGA ADC的数据。

2.云访问

IcarusQ-Executor的输入输出被妥善定义后,我们就可以将其运行为云服务以实现远程实验。图17中展示了云平台远程控制实验装置的方式。我们使用了Flask服务器[44]和Redis数据库[45]作为用户与工作机之间的媒介。当前的软件部署还用到了Qibo框架[48]。

图17. 云访问软件部署

III. 结论

我们的超导量子比特控制和测量装置基于如下的设计思想:可扩展、尽量减少微波元件和仪器、可远程控制。最终,我们选用了RFSoC器件,基于其16通道ADC和DAC实现高采样率下的5-8GHz微波信号直接产生和检测。这使得我们避免使用模拟IQ混频器并省去了对混频器的反复校准工作。我们还设计了一套将多个FPGA板同步在一个主时钟并触发所有ADC和DAC通道的电路。远程访问能力依靠服务器上的数据库API实现,使得用户可以远程发送命令和获取结果。

在短期内,有若干项改进正在被考虑。RFSoC上更多的功能将被用起来。随着大量功能被集成入单芯片中,可以开始考虑将设备从室温环境移入稀释制冷机中[48]以获得更好的信噪比并简化与室温系统的连接关系。为了获得更多的采样数据,我们还将研究内存优化技术,尝试更快的DDR RAM。这些工作将在下一代更先进的器件发布后开展。

参考文献

该文共列出48篇参考文献,此处略。

——————————————————————

译文就是这样,聊聊感想。相信不少朋友会一拍大腿,哎呀这不就是一台冲着冰箱发功的雷达嘛。

除了低噪声电流源以外,这套装置本质上是一个多通道的高速射频信号播放和采集系统,而类似的技术在雷达、通信、仪器仪表等领域中是普遍用到的。文中提到的RFSoC器件当下就在各种阵列化高速信号采集播放和处理的相关领域中被广泛用到,货架产品形态层出不穷。

从学习和研究的角度看,通过本文,我们发现一台量子计算的控制和测量装置中除了量子本身相关的理论以外基本都是电子工程师耳熟能详的概念,ADC、DAC、FPGA、奈奎斯特采样定理、傅里叶变换、功率谱、白噪声、阿伦偏差、恒流源、运算放大器、巴伦、偏置器等等。如果回望大学时所学,那不就是模拟电路、数字电路、可编程逻辑、数字信号处理、概率和统计等等课程嘛。所以,如前所说,科学是结构化的体系,先进的装置和前沿的研究终究都会落实到各项成熟且具体的技术和工具。可以相信,我们过去和现在所学所想在未来也必有其价值。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论