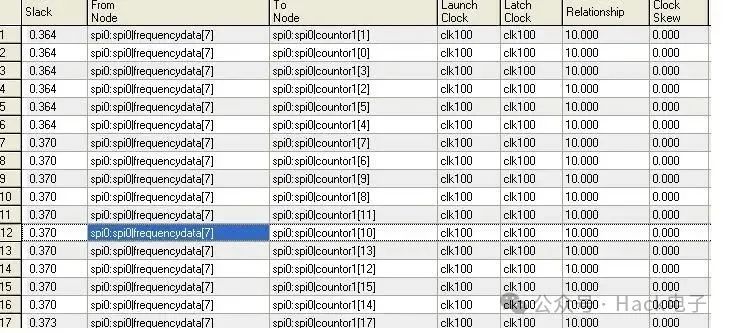

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

2020-11-19 11:44:00 5226

5226

是指FPGA与外部器件共用外部时钟;源同步(SDR,DDR)即时钟与数据一起从上游器件发送过来的情况。在设计当中,我们遇到的绝大部分都是针对源同步的时序约束问题。所以下文讲述的主要是针对源同步的时序约束。 根据网络上收集的资料以及结合自

2020-11-20 14:44:52 6859

6859

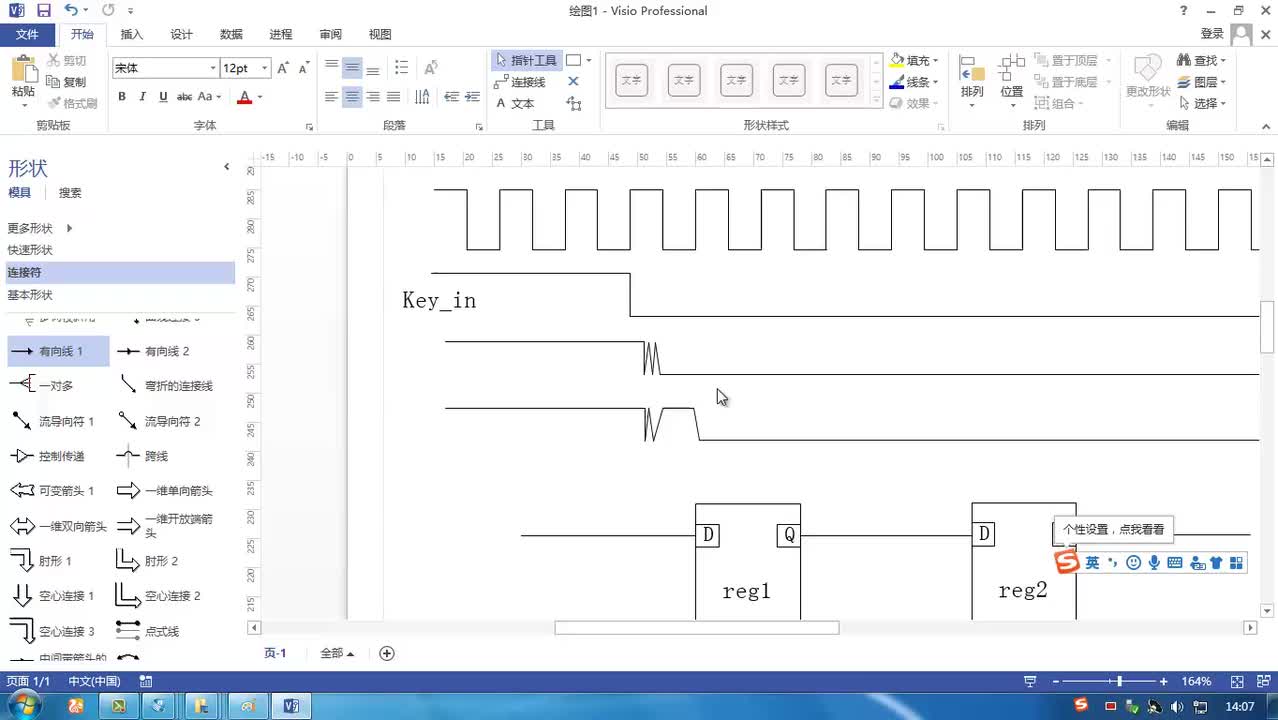

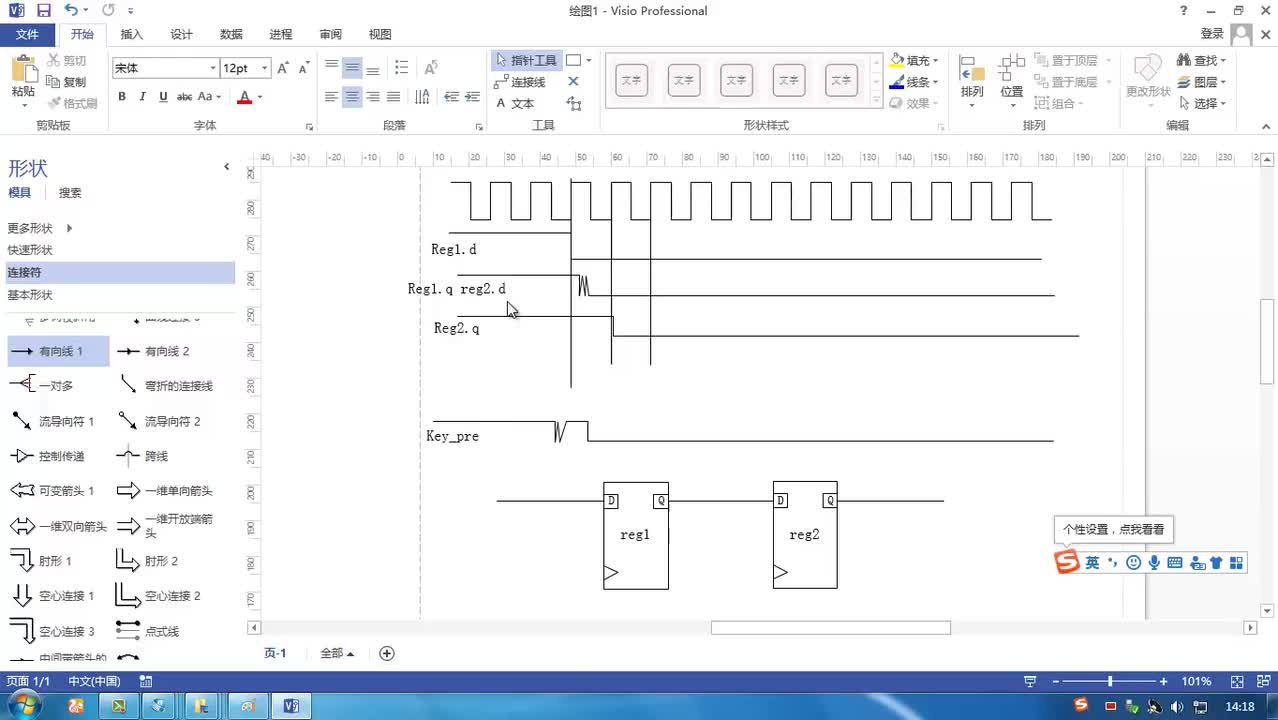

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01 3278

3278

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 4067

4067 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

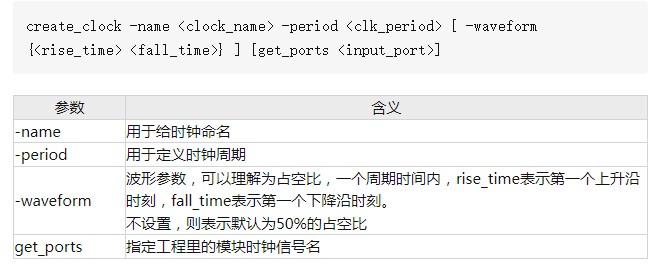

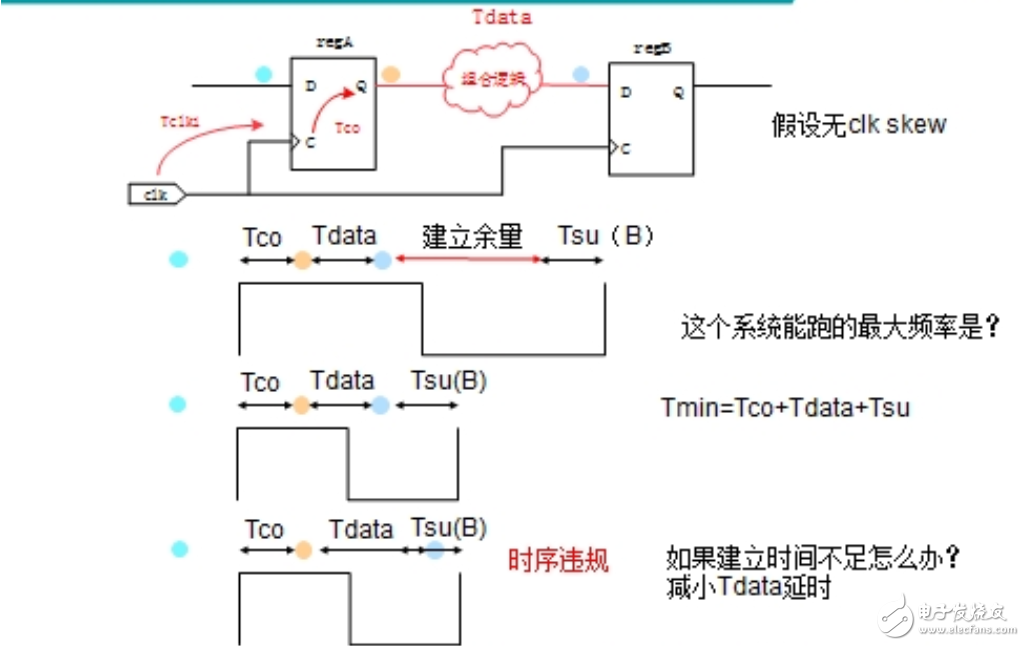

1382 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。

2023-06-26 14:47:16 923

923

FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

2023-08-14 17:49:55 712

712

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

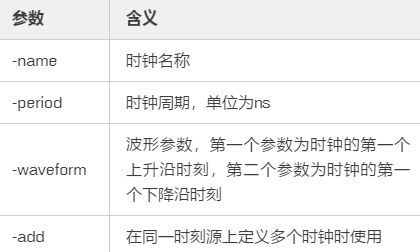

时钟周期约束是用于对时钟周期的约束,属于时序约束中最重要的约束之一。

2023-08-14 18:25:51 472

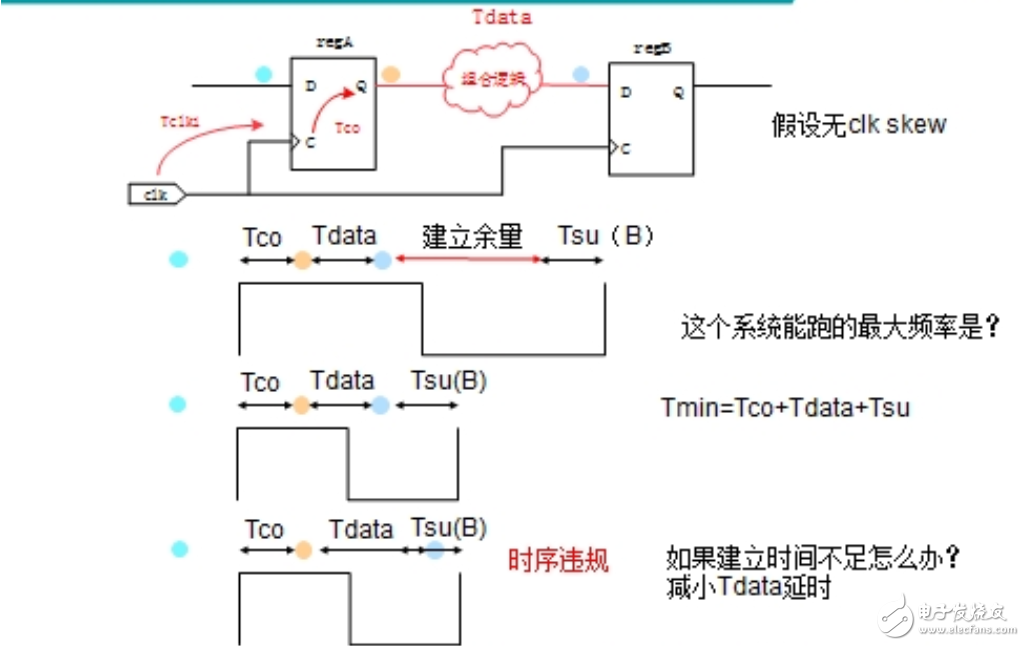

472 在设计以太网中继器时,因为没有配置时钟约束,导致中继器工作不正常。后面根据手册配置时钟约束解决了此问题。

2016-10-07 18:51:24

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束

2017-05-25 15:06:47

本帖最后由 qzq378271387 于 2012-8-15 16:56 编辑

FPGA_DSP_解决方案

2012-08-15 16:44:32

嗨,我是初学者,在FPGA上设计系统。我检查了我的输出没有生成,所以我想要。我有5个子模块,它们具有来自相同输入的时钟。据我所知,考虑到不同金属与时钟输入的不同延迟,应对每个子模块进行时钟缓冲。但在

2020-05-22 09:22:23

(30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2022-02-23 06:32:02

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

FPGA典型应用领域以及解决方案

2012-08-20 13:36:46

引言针对需要切换多个FPGA配置码流的场合,Xilinx公司提出了一种名为System ACE的解决方案,它利用CF(Compact Flash)存储卡来替代配置用PROM,用专门的ACE控制芯片

2019-06-10 05:00:08

VGA驱动接口时序设计之3时钟约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 如图8.26所示

2015-07-30 22:07:42

直接就连接到了驱动FPGA内部模块的时序产生时钟信号,所以它的偏斜其实就是PLL输出的这个时钟信号到引脚的延时值。因为这个路径其实也应该算在了reg2pin的时序路径中,如果不做约束系统不会对其进行

2015-08-06 21:49:33

FPGA应用领域及解决方案

2012-08-20 11:23:55

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

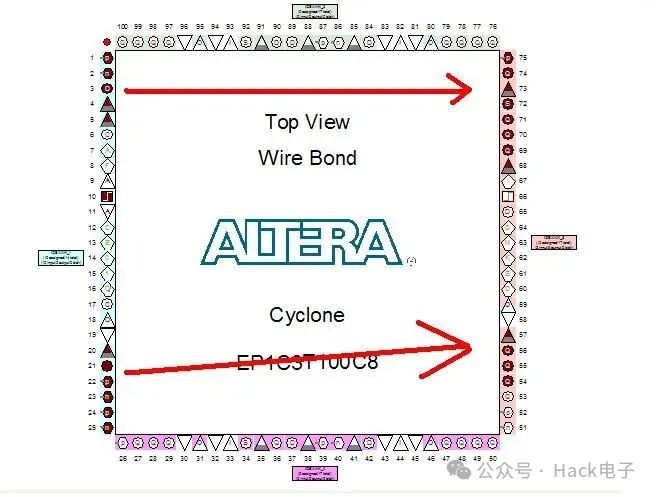

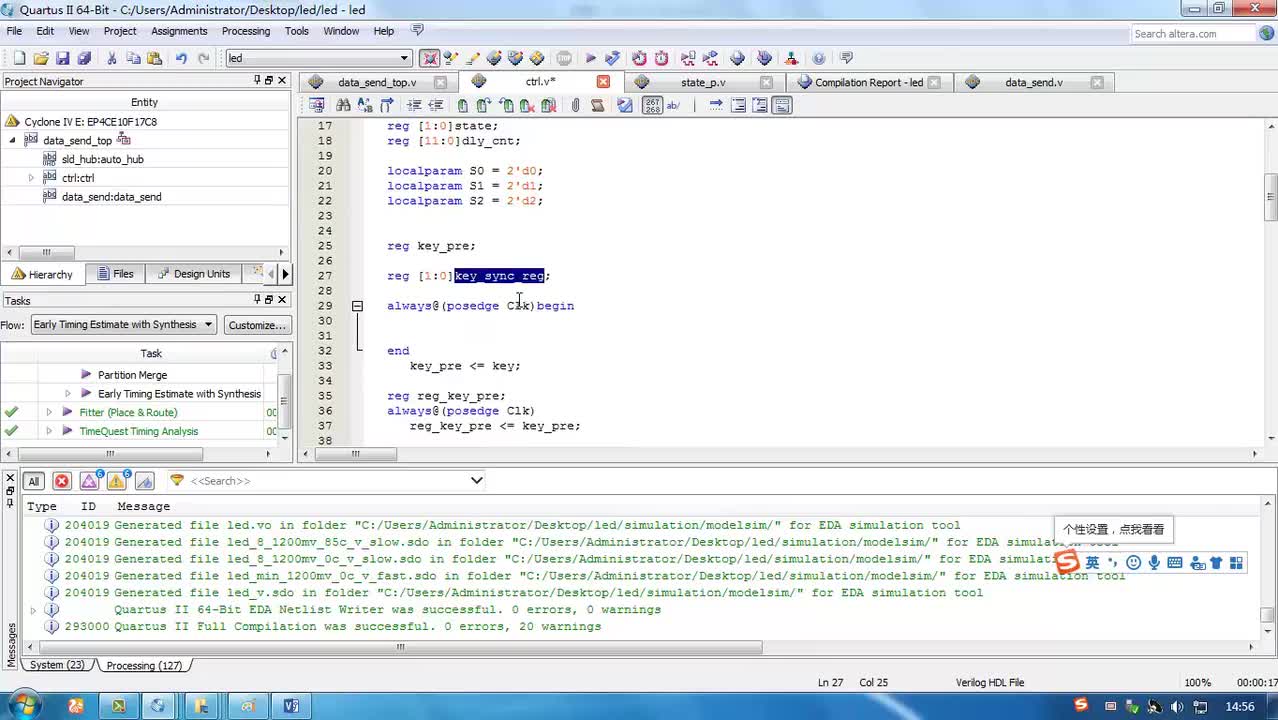

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

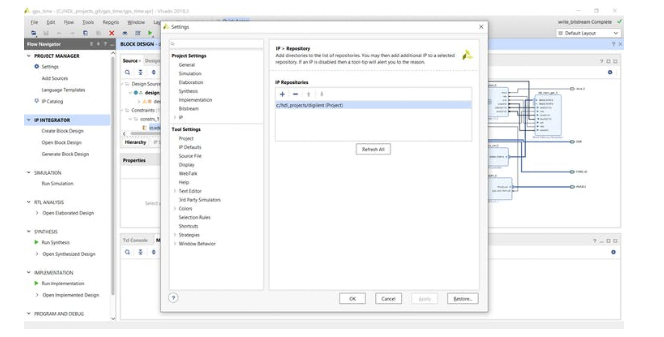

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-09-21 07:45:57

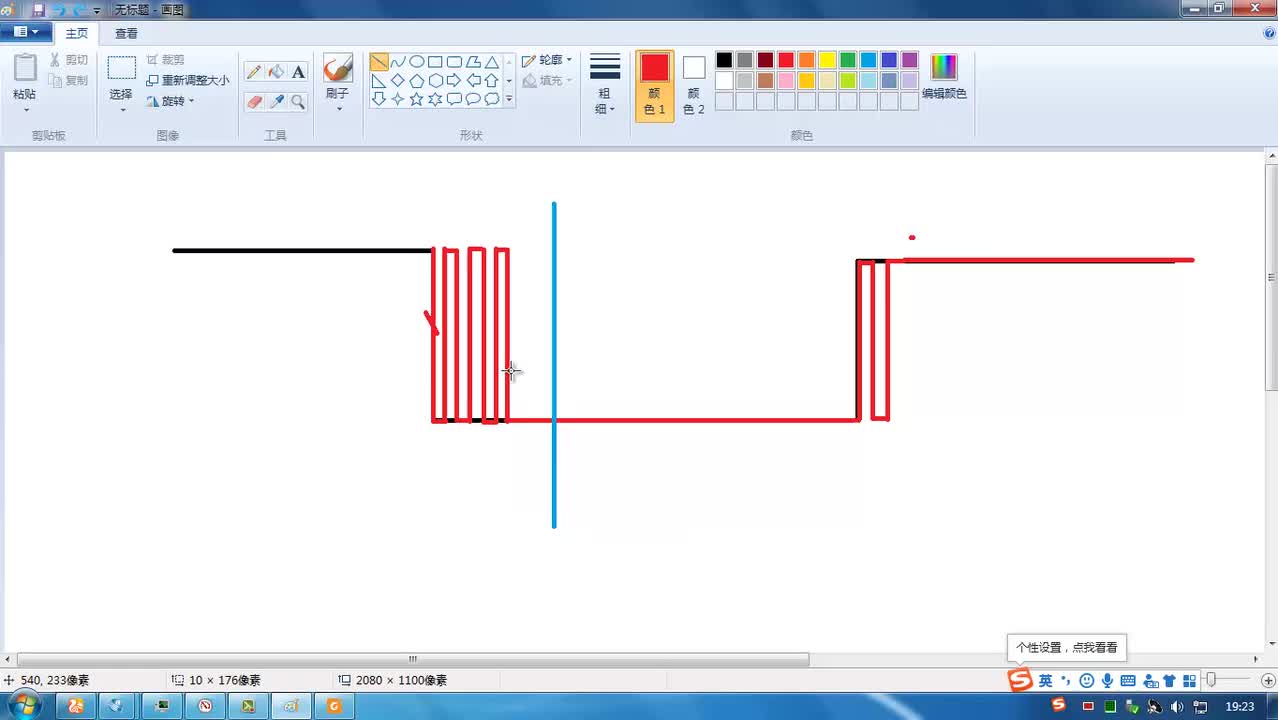

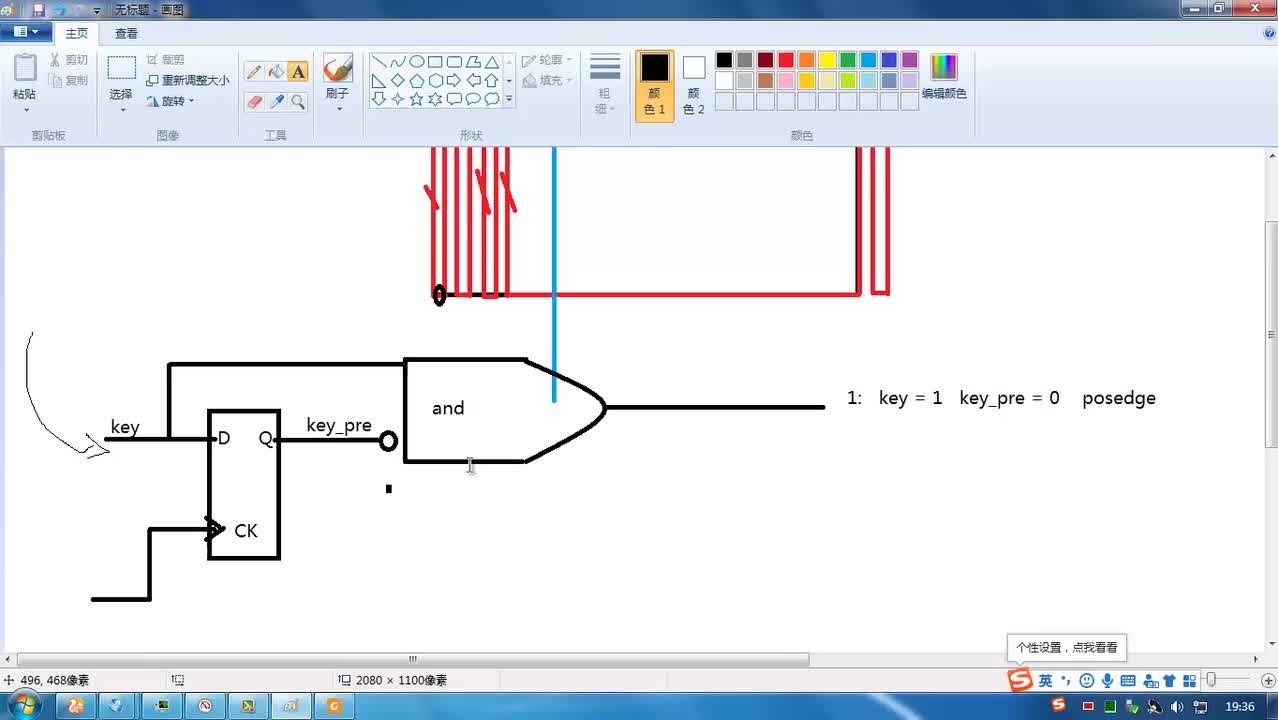

,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约束以满足设计要求。因为时钟周期是预先知道的,而触发器之间的延时是未知的(两个触发器之间的延时等于一个时钟周期),所以得通过约束来控制触发器之间的延时。当延时小于一个时钟周期的时候,设计的逻辑才能稳定工作,反之,代码会跑飞。

2018-08-29 09:34:47

,clk_p是输入,clk_n是负差分对。我已经分配了一个引脚,通常在约束文件中只有一个输入引脚。我认为时钟限制必须像这样#create_clock -name clock_in -period 5

2020-08-05 09:56:08

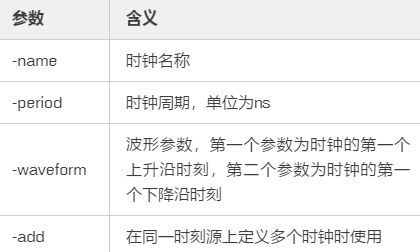

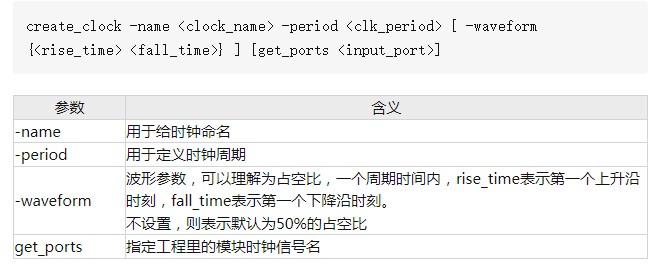

文章目录1、时钟约束的概念2、 DC中的时序约束参考文章时间又拖拖拖,随着追寻DFT的进度,DC的进度在经历了.dynopsys_dc.setup后,就停滞不前了,接下来本文就来介绍DC的约束篇目

2021-11-17 06:56:34

时钟信号从普通IO管脚输入怎么进行处理,时钟从普通IO管脚进入FPGA后能进入全局时钟网络吗?因为只有全局时钟管脚后面连接有IBUFG/IBUFGDS缓冲单元,如果差分时钟信号从普通IO管脚进入后

2012-10-11 09:56:33

在设计中想用上AD9254作为ADC,在设计过程中发现datasheet内部提供了多种时钟设计方案,由于设计的限制,想要省去所有方案中均推荐使用的AD951x芯片,请问是否有曾经使用过该款AD的同仁,使用直接从FPGA差分时钟引脚引出的时钟信号,是否能够满足设计的要求?

2018-11-02 09:14:32

您好,我正在分析使用Xilinx ISE 9.2 Service Pack 4为Spartan 3 FPGAT合成的现有设计的时序约束。该设计具有20 MHz的单时钟输入(sys_clk),用于

2020-05-01 15:08:50

JS-500时钟抖动解决方案

2019-10-14 11:26:07

输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到 FPGA 的信号。约束名称:input delay。约束条件的影响主要有 4 个因素:外部芯片的 Tco,电路板上信号

2012-03-05 15:02:22

cy时钟解决方案,中文的

2012-11-22 17:06:57

为FPGA应用设计优秀电源管理解决方案不是一项简单的任务,相关技术讨论有很多。本文一方面旨在找到正确解决方案并选择最合适的电源管理产品,另一方面则是如何优化实际解决方案以用于FPGA。找到合适的电源

2019-12-11 16:56:30

为什么推出Virtex-5LXT FPGA平台和IP解决方案?如何打造一个适用于星形系统和网状系统的串行背板结构接口FPGA?

2021-04-29 06:18:31

为什么要提出一种超视V8”银行视频监控系统?介绍一种“超视V8”银行视频监控系统的解决方案

2021-06-02 06:07:06

SDRAM数据手册有如张时序要求图。如何使SDRAM满足时序要求?方法1:添加时序约束。由于Tpcb和时钟频率是固定的,我们可以添加时序约束,让FPGA增加寄存器延时、寄存器到管脚的延时,从而使上述

2016-09-13 21:58:50

本文一方面旨在找到正确解决方案并选择最合适的电源管理产品,另一方面则是如何优化实际解决方案以用于FPGA。找到合适的电源解决方案寻找为FPGA供电的最佳解决方案并不简单。许多供应商以适合为FPGA

2019-05-05 08:00:00

5406D这样一种新兴的可编程逻辑器件,提供了灵活、超低抖动和低成本的解决方案来驱动SERDES参考时钟。这些器件和低成本的CMOS振荡器能够满足FPGA、SoC和ASSP的SERDES参考时钟所需的严格

2019-05-21 05:00:13

安捷伦公司数字测试资深技术/市场工程师 冀卫东为满足日益复杂的数字化系统的设计要求,FPGA的密度及复杂性也在急速增长,越来越多的系统或子系统功能在FPGA内部实现,其先进的功能和高集成度使FPGA成为极具吸引力的解决方案,进而也使得基于内核的FPGA测试方案浮出水面。

2019-07-11 06:15:12

你好我正在使用ML605板,差分时钟输入产生一个全局使用的时钟。但是当试图约束时钟时,我不知道如何设置它。有什么建议么?谢谢

2019-10-28 07:21:01

`作者:Frederik Dostal为FPGA应用设计优秀电源管理解决方案不是一项简单的任务,相关技术讨论有很多。本文一方面旨在找到正确解决方案并选择最合适的电源管理产品,另一方面则是如何优化实际

2018-08-13 09:29:10

1. 基本时钟约束create_clock-period 40.000 -name REFCLK [get_ports ref_clk] 创建时钟周期ns命名 名字连接端口

2018-09-21 11:51:59

请教一下,FPGA由晶振输入的时钟,只是作为DCM输入,在其他各模块中没有用到,自己最简单的程序,时序约束报最高工作时钟也是100MHz,查资料这款FPGA最快可跑四五百M,请教一下,为什么我最简单的一个程序只能跑100MHz,是否是晶振输入时钟的延时所限制了?十分感谢

2017-08-11 10:55:07

,即将AD的数据转换传入FPGA内,没有其他模块。时钟约束后可跑的最快的时钟为100MHz

2017-08-14 15:07:05

求一款基于IPTV系统中的FPGA供电问题的解决方案。

2021-04-29 07:03:13

我不得不承认,随着时间的推移为 FPGA 供电变得越来越复杂,本文提供一些建议,希望可以帮助简化 FPGA 的电源解决方案,使用户能够创建出快速便捷的解决方案。在为 FPGA 供电时需要考虑若干电源

2022-11-23 07:14:47

DCMl输出: clkfx = 100MHz和clkfx_180=100MHz不过相位差180度.FPGA输出到DAC中,DAC需要FPGA提供data[11:0]和写入时钟. 我用clkfx作为

2012-03-29 09:51:36

比如FPGA输出一个50M的差分时钟,DDS用这做参考,里面做8倍频得到400M的系统时钟这样可行么,请大家赐教以前的方案都是按AD的demo板做的

2018-11-19 09:13:45

一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 内容提纲 FPGA的最初应用及延伸 基于FPGA的原型验证与结构化ASIC 基于FPGA的数字信号处理 基于FPGA的嵌入式处理 基于FPGA的物理层通信 基于FPGA的可重构计算技术 主流FPGA厂商的解决方案

2011-03-15 13:05:25 90

90 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 时序约束可以使得布线的成功率的提高,减少ISE布局布线时间。这时候用到的全局约束就有周期约束和偏移约束。周期约束就是根据时钟频率的不同划分为不同的时钟域,添加各自周期约束。对于模块的输入输出端口添加

2017-02-09 02:56:06 605

605 ,您经常需要定义时序和布局约束。我们了解一下在基于赛灵思 FPGA 和 SoC 设计系统时如何创建和使用这两种约束。 时序约束 最基本的时序约束定义了系统时钟的工作频率。然而,更高级的约束能建立时钟路径之间

2017-11-17 05:23:01 2417

2417

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要

2017-11-17 19:01:00 6665

6665

本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-24 19:59:29 2671

2671

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 6374

6374 ”列可以容易的辨别出同步时钟。下面是3个场景,你需要使用合适的时钟约束处理异步时钟之间的关系。1. 如果时钟互联报告有很多(或者一个)红色的"Timed (unsafe)" 或者还有

2019-07-15 15:35:23 6003

6003 FPGA在与外部器件打交道时,端口如果为输入则与input delay约束相关,如果最为输出则output delay,这两种约束的值究竟是什么涵义,在下文中我也会重点刨析,但是前提是需要理解图1和图2建立余量和保持余量。

2019-11-10 10:06:23 3618

3618

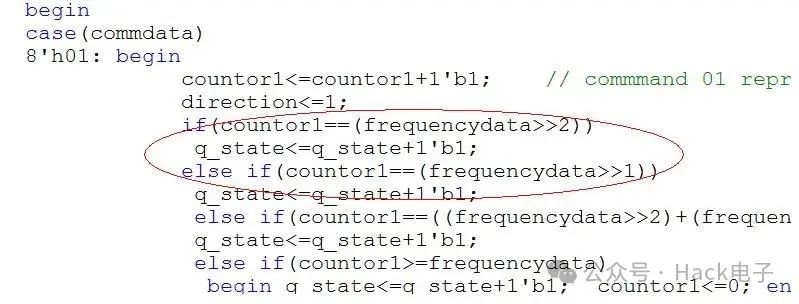

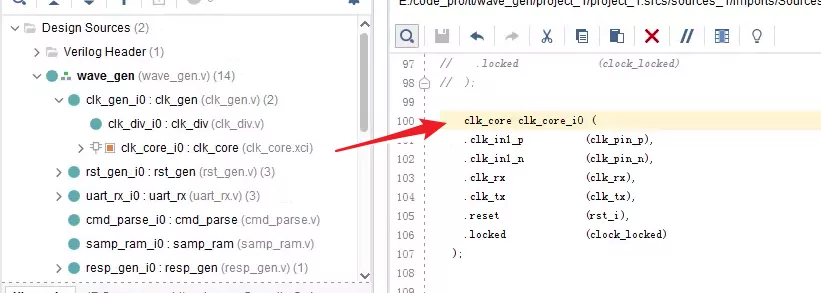

伪路径约束 在本章节的2 约束主时钟一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径

2020-11-14 11:28:10 2636

2636

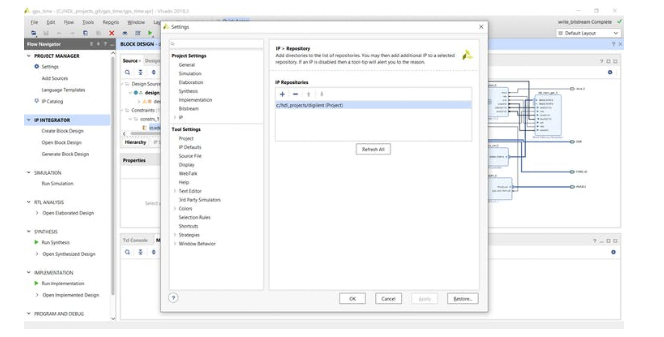

约束衍生时钟 系统中有4个衍生时钟,但其中有两个是MMCM输出的,不需要我们手动约束,因此我们只需要对clk_samp和spi_clk进行约束即可。约束如下

2020-11-17 16:28:05 2023

2023

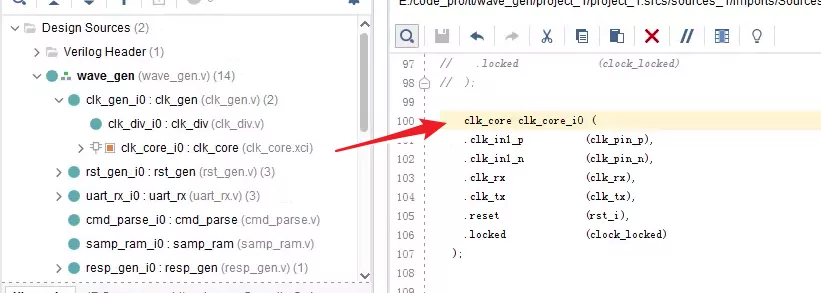

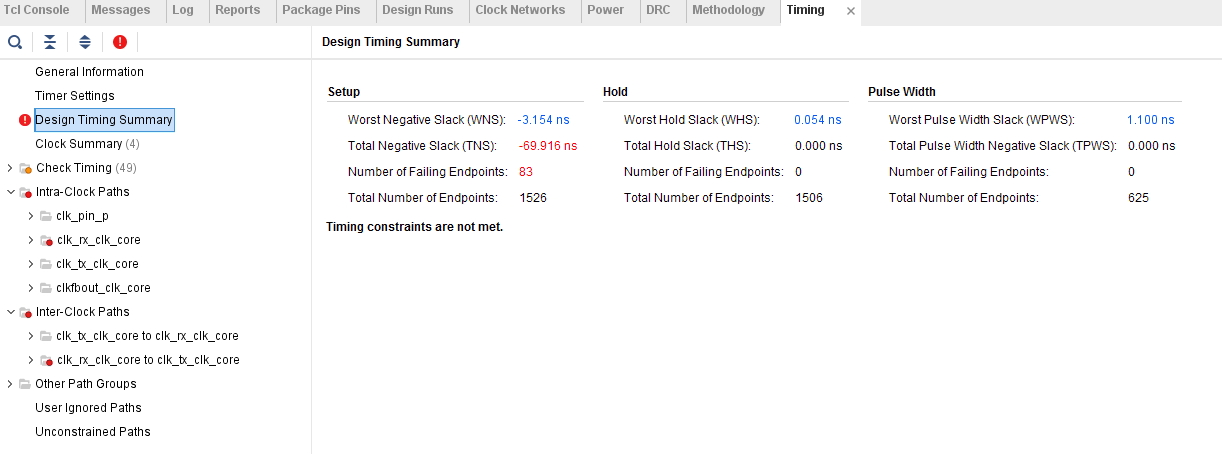

约束主时钟 在这一节开讲之前,我们先把wave_gen工程的wave_gen_timing.xdc中的内容都删掉,即先看下在没有任何时序约束的情况下会综合出什么结果? 对工程综合

2020-11-16 17:45:06 3094

3094

有人希望能谈谈在做FPGA设计的时候,如何理解和使用过约束。我就以个人的经验谈谈: 什么是过约束; 为什么会使用过约束; 过约束的优点和缺点是什么; 如何使用过约束使自己的设计更为健壮

2021-03-29 11:56:24 4379

4379

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 3126

3126

在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。 第一:换一个速度更快点的芯片,altera公司

2021-10-11 14:52:00 2878

2878

对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

2022-02-16 16:21:36 1229

1229

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

本方案是一个基于FPGA的二进制时钟,使用GPS作为时间参考。

2022-05-13 17:41:31 1786

1786

FPGA端挂载DDR时,对FPGA引脚的约束和选择并不是随意的,有一定的约束规则,一般可以通过利用vivado工具中的pin assignment去选择合适的位置辅助原理图设计。

2022-07-03 17:20:44 3186

3186 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

时钟周期约束: 时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

2022-08-05 12:50:01 2716

2716 数字设计中的时钟与约束 本文作者 IClearner 在此特别鸣谢 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的时钟(与建模)吧。主要内容如下所示

2023-01-28 07:53:00 2107

2107

上一篇《XDC 约束技巧之时钟篇》介绍了 XDC 的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。我们知道 XDC 与 UCF 的根本区别之一就是对跨时钟域路径(CDC

2023-04-03 11:41:42 1135

1135 当设计存在多个时钟时,根据时钟的相位和频率关系,分为同步时钟和异步时钟,这两类要分别讨论其约束

2023-04-06 14:34:28 886

886

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-04-27 10:08:22 768

768 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

FPGA设计中,时序约束对于电路性能和可靠性非常重要。

2023-06-26 14:53:53 820

820

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

2023-07-12 11:17:42 794

794

电子发烧友App

电子发烧友App

评论