1 概述

HDL(VHSIC Hardware Description Language)是一种硬件描述语言,主要用于描述数字电路和系统的结构、行为和功能。它是一种用于硬件设计的标准化语言,能够帮助工程师们更好地描述和设计数字电路,并且广泛应用于FPGA和ASIC设计中。

在VHDL中,一个设计被描述为一个实体(entity),它包含了输入输出端口的描述。实体也包含了该设计的行为(behavior)的描述。 此外,VHDL还包括了标准库(standard library)和数学运算库(numeric package)等。

VHDL的基本语法包括关键字、标识符、注释、数据类型(如std_logic、integer等)、变量声明、信号声明、过程语句、并行操作符等。

以下是VHDL的一些基本特性和语法:

实体声明(Entity Declaration):实体(entity)是一个设计的接口和规范,描述了设计的输入和输出信号。在实体声明中,可以指定设计的接口和端口类型。

架构(Architecture):架构是实体的行为和功能描述。它包括了组件实例化、信号声明、过程语句等。在架构中,可以描述设计的逻辑和数据流动。

信号(Signal)和变量(Variable):在VHDL中,信号用于描述设计中的数据传输,而变量通常用于描述局部的数据存储。信号和变量的作用在于描述设计中的数据流动和数据处理。

过程(Process):过程描述了设计中的行为和逻辑。过程可以包括对信号和变量的操作、时序逻辑的描述等。

循环(Loop):VHDL中也包括了循环语句,用于描述设计中的重复操作。

总的来说,VHDL是一门强大的硬件描述语言,能够帮助工程师们进行数字电路的设计和描述。通过VHDL,工程师们可以更好地理解和描述设计的结构和行为,从而实现复杂的数字系统设计。虽然VHDL的语法可能对初学者来说有一定的复杂性,但一旦熟悉了其基本特性和语法,将会成为非常有用的工具。

library IEEE; use IEEE.std_logic_1164.all; entity ExampleModule is port( clk, reset : in std_logic; input1, input2 : in std_logic_vector(7 downto 0); output1 : out std_logic_vector(7 downto 0) ); end ExampleModule; architecture Behavioral of ExampleModule is component SubModule is port( a, b : in std_logic_vector(7 downto 0); c : out std_logic_vector(7 downto 0) ); end component; signal intermediate : std_logic_vector(7 downto 0); begin SubModule_inst : SubModule port map( a => input1, b => input2, c => intermediate ); process(clk, reset) begin if reset = '1' then output1 <= (others => '0'); elsif rising_edge(clk) then output1 <= intermediate; end if; end process; end Behavioral;

2 样例

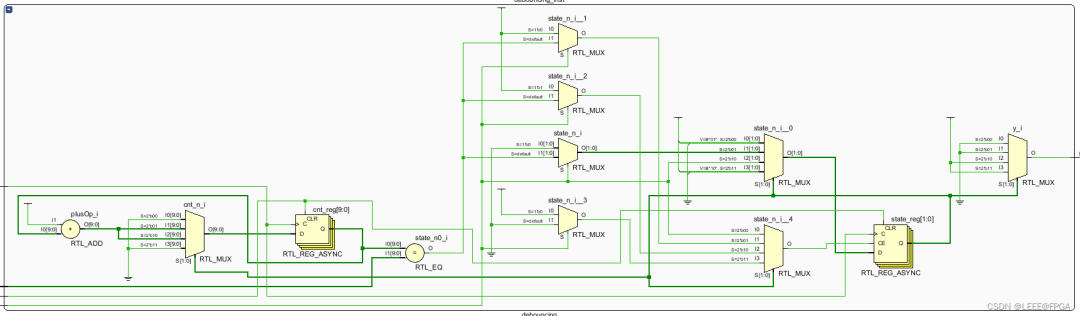

按键消抖

设计文件:

library ieee;

use ieee.std_logic_1164.all;

use IEEE.NUMERIC_STD.ALL;

entity debouncing is

generic(N: integer := 10);

port(clk: in std_logic;

rst: in std_logic;

u: in std_logic;

delay : in std_logic_vector(N-1 downto 0);

y: out std_logic);

end debouncing;

architecture arch of debouncing is

type state_type is (zero, wait0, wait1, one);

signal state, state_n: state_type;

signal cnt, cnt_n: unsigned(N-1 downto 0);

begin

-- state register

process(clk,rst)

begin

if (rst='1') then

state <= zero;

cnt <= (others => '0');

elsif (rising_edge(clk)) then

state <= state_n;

cnt <= cnt_n;

end if;

end process;

-- next-state/output logic

process(state,u,cnt,delay)

begin

state_n <= state;

cnt_n <= (others => '0');

case state is

when zero =>

y <= '0';

if u= '1' then

state_n <= wait0;

end if;

when wait0 =>

y <= '0';

-- check next state

if u = '0' then

state_n <= zero;

elsif cnt = unsigned(delay) then

state_n <= one;

end if;

-- increment counter

cnt_n <= cnt + 1;

when wait1 =>

y <= '1';

-- check next state

if u = '1' then

state_n <= one;

elsif cnt = unsigned(delay) then

state_n <= zero;

end if;

-- increment counter

cnt_n <= cnt + 1;

when one =>

y <= '1';

if u= '0' then

state_n <= wait1;

end if;

end case;

end process;

end arch;

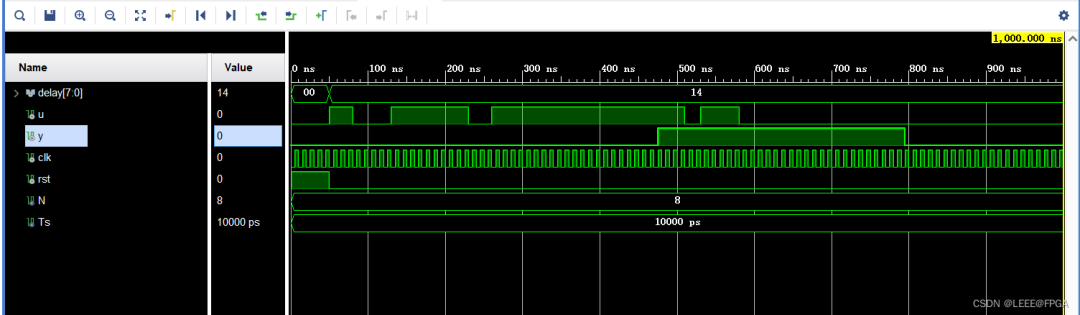

按键消抖仿真文件:

ibrary ieee;

use ieee.std_logic_1164.all;

use IEEE.NUMERIC_STD.ALL;

entity debouncing_tb is

end debouncing_tb;

architecture tb of debouncing_tb is

constant N: integer := 8;

signal delay: std_logic_vector(N-1 downto 0);

signal u, y,z : std_logic;

signal clk, rst : std_logic;

-- Clock period definitions

constant Ts : time := 10 ns;

begin

db0 : entity work.debouncing

generic map(N => N)

port map (clk => clk,

rst => rst,

delay => delay,

u => u,

y => y);

-- Clock process definitions

process

begin

clk <= '0';

wait for Ts/2;

clk <= '1';

wait for Ts/2;

end process;

stimuli : process

begin

rst <= '1';

u <= '0';

delay <= (others => '0');

wait for 5*Ts;

rst <= '0';

delay <= std_logic_vector(to_unsigned(20,N));

u <= '1';

wait for 3*Ts;

u <= '0';

wait for 5*Ts;

u <= '1';

wait for 10*Ts;

u <= '0';

wait for 3*Ts;

u <= '1';

wait for 25*Ts;

u <= '0';

wait for 2*Ts;

u <= '1';

wait for 5*Ts;

u <= '0';

wait for 25*Ts;

wait;

end process;

end tb;

3 常用编写

时序逻辑:

在 VHDL 中,时序逻辑指的是描述在特定时钟信号的边沿或状态变化下发生的操作。时序逻辑可以包括使用 rising_edge 或 falling_edge 函数来检测时钟信号的上升沿或下降沿,以及使用 wait for 语句来控制时序行为。下面是一个简单的示例,说明了时序逻辑的基本用法:

architecture Behavioral of ExampleModule is

begin

process (clk)

begin

if rising_edge(clk) then

-- 在时钟上升沿执行的操作

-- 例如,更新寄存器、执行状态转移等

end if;

end process;

end architecture Behavioral;

在这个例子中,我们定义了一个处理时钟信号 clk 的过程。使用 if rising_edge(clk) then 表示当检测到时钟信号的上升沿时执行操作。在这个逻辑块中,你可以更新寄存器、执行状态转移等与时钟相关的操作。这种时序逻辑的描述允许你根据特定时钟信号的变化来控制设计的行为。

时序逻辑在数字电路设计中非常重要,因为它能够确保设计在特定时钟信号的控制和同步下正确运行。通过使用时序逻辑,可以将设计的行为明确地与时钟信号进行关联,从而实现可靠的同步逻辑。

VHDL组合逻辑:

在 VHDL 中,组合逻辑是指在不涉及时钟信号的条件下,根据输入直接计算输出的逻辑部分。通常,组合逻辑描述了在给定输入条件下的输出行为,而且输出立即对输入进行响应,不依赖于时钟的边沿。以下是一个简单的示例,说明了组合逻辑的基本用法:

-- 一个简单的 2:1 多路选择器的组合逻辑

entity Mux2x1 is

port (

sel: in std_logic;

a, b: in std_logic;

y: out std_logic

);

end entity Mux2x1;

architecture Behavioral of Mux2x1 is

begin

process (sel, a, b)

begin

if sel = '0' then

y <= a;

else

y <= b;

end if;

end process;

end architecture Behavioral;

在这个例子中,我们创建了一个名为 Mux2x1 的实体,该实体具有三个输入端口 sel、a 和 b 以及一个输出端口 y。在 Behavioral 架构中的处理过程中,我们使用 if 语句来根据输入信号 sel 的值选择输出的值。这是一个典型的组合逻辑,因为输出 y 的值是仅仅依赖于当前输入信号的状态而计算出来的,不涉及时钟或者时序控制。

组合逻辑在数字电路设计中很常见,它描述了电路在给定输入下的输出行为,没有涉及时钟控制或时序逻辑。

case语句:

当需要根据输入的不同值采取不同的操作时,可以使用VHDL中的case语句。下面是一个简单的VHDL case语句的示例:

process (input)

begin

case input is

when "00" =>

-- 对输入为 "00" 执行的操作

output <= "0000";

when "01" =>

-- 对输入为 "01" 执行的操作

output <= "0011";

when "10" =>

-- 对输入为 "10" 执行的操作

output <= "1100";

when others =>

-- 对其他输入情况下执行的操作

output <= "1111";

end case;

end process;

在这个例子中,我们在一个process中使用了case语句来根据输入的不同情况执行相应的操作。当输入信号input的值满足某个条件时,对应的输出output会被赋予相应的值。 “when others” 表示当输入值不满足前面列举的情况时执行的操作。

这个例子展示了VHDL中使用case语句进行条件判断和执行不同操作的方法。

状态机:

在 VHDL 中实现状态机(state machine)通常是通过组合逻辑和时序逻辑相结合的方式来完成的。状态机描述了一个系统在不同状态下的行为,通常会随着输入信号的变化而转换状态。下面是一个简单的示例,说明了一个基本的有限状态机在 VHDL 中的实现:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity SimpleFSM is Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; input : in STD_LOGIC; output : out STD_LOGIC); end SimpleFSM; architecture Behavioral of SimpleFSM is type state_type is (s0, s1, s2, s3); signal state, next_state : state_type; begin process (clk, reset) begin if reset = '1' then state <= s0; -- 在复位时将状态设置为初始状态 elsif rising_edge(clk) then state <= next_state; -- 在时钟的上升沿根据下一个状态进行状态更新 end if; end process; process (state, input) begin case state is when s0 => if input = '1' then next_state <= s1; -- 根据输入信号转移至下一个状态 else next_state <= s0; -- 如果输入信号不满足条件,保持在当前状态 end if; when s1 => if input = '0' then next_state <= s2; else next_state <= s1; end if; when s2 => if input = '1' then next_state <= s3; else next_state <= s2; end if; when s3 => next_state <= s0; when others => next_state <= s0; end case; end process; end Behavioral;

在这个例子中,我们创建了一个名为 SimpleFSM 的实体,该实体包括了时钟信号 clk、复位信号 reset、输入信号 input 和输出信号 output。状态机的行为由 state 和 next_state 信号来描述。在第一个 process 中,我们根据时钟信号和复位信号来更新 state 的值,以此来控制状态的转移。在第二个 process 中,我们根据当前的状态和输入信号来计算下一个状态 next_state。这个状态机描述了一个简单的输入序列检测过程,根据输入序列的不同,状态机将在不同的状态间转移。这是一个基本的有限状态机的例子,通过状态的转移来实现不同的行为。

时钟信号编写:

a)占空比为50%

constant PERIOD : time :=; --定义时钟周期 --使用after语句 CLK <= not CLK after PERIOD/2; --使用wait语句 constant PERIOD : time := ; CLK <= '0'; wait for PERIOD/2; CLK <= '1'; wait for PERIOD/2;

b)非50%占空比

constant DUTY_CYCLE : real :=; --定义占空比系数 constant PERIOD : time := ; --定义时钟周期 --使用after语句 CLK <= '1' after (PERIOD - (PERIOD * DUTY_CYCLE)) when CLK = '0' else '0' after (PERIOD * DUTY_CYCLE); --使用wait语句 CLK <= '0'; wait for (PERIOD - (PERIOD * DUTY_CYCLE)); CLK <= '1'; wait for (PERIOD * DUTY_CYCLE);

c)差分端口占空比为50%

constant PERIOD : time :=; --设置时钟周期 --使用after语句 CLK_P <= not CLK_P after PERIOD/2; CLK_N <= not CLK_N after PERIOD/2; --使用wait语句 CLK_P <= '0'; CLK_N <= '1'; wait for PERIOD/2; CLK_P <= '1'; CLK_N <= '0'; wait for PERIOD/2;

延时:

constant SIM_TIME : time := 10 ms; --设置仿真时间SIM_TIME, 时间为10ms<= after SIM_TIME; --信号在SIM_TIME后进行赋值 wait on ; --延时到信号有变化 wait until falling_edge( ); --延时到信号的下降沿到来 wait until rising_edge( ); --延时到信号的上升沿到来 wait until = ; --延时到信号变化到指定值

循环:

a) loop语句

loop CLK <= not CLK; wait for PERIOD/2; ifthen exit; end if; end loop;

b) for语句

forin to loop ; ; end loop;

c)while语句

whileloop ; ; end loop;

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论