这里给出一种利用MCU自带 ADC 和DAC,并结合运放、电容、电阻等元件搭建外围硬件电路,实现10~20位测量精度可调的ADC的方法。 1 高精度ADC设计原理 输入电压经过电阻分压产生电压U入

2011-10-17 11:49:32 3830

3830

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。

2024-02-22 16:15:03 1624

1624

目录 第一章 ADC与DAC概念 第二章 ADC与DAC原理 第三章 ADC与DAC基础知识详解 第四章 ADC与DAC 实用设计问答 .....

2011-08-03 11:42:34

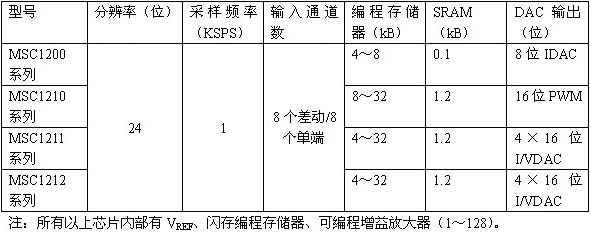

Sigma Delta(ΣΔ)转换器ADC 流水线转换器ADC 二进制加权DAC 串DAC R-2R DAC 逐次逼近寄存器,SAR 最受欢迎 经常使用I2C或SPI接口(有时并行) 名称来自于

2018-11-01 15:54:53

(1)ADC、DAC选型时候的有个data input format 是lvds和cmos什么意思啊?1. lvds是不是那个DCO+和DCO-?。这两个信号是不是必须要从时钟专用引脚输入

2017-01-23 15:17:38

ADC与DACADC与DAC的原理参考电压 ADC与DAC都是基于参考电压工作的,以百分数的形式进行工作。例如,参考电压为3V时,ADC测定电压为0.5就是1.5V,DAC输出0.5就是输出

2021-08-18 06:32:30

ADC与DAC的原理是什么?

2021-11-23 06:52:56

与 ADC 相反。在常见的数字信号系统中,大部分传感器信号被化成电压信号,而 ADC 把电压模拟信号转换成易于计算机存储、处理的数字编码,由计算机处理完成后,再由 DAC 输出电压模拟信号,该电压

2021-08-09 07:32:37

描述该参考设计和相关的示例 Verilog 代码可用作将 Altera FPGA 连接到德州仪器 (TI) 高速 LVDS 接口模数转换器 (ADC) 和数模转换器 (DAC) 的起点。其中说明

2018-07-24 07:38:13

介绍整个方案实现的原理主要是将PDM输出到FPGA管脚然后经过低通滤波接到比较器负端,Digital Filter换成累加器,就变成了真正的1-Bit ADC。可以量化模拟比较器正端电平。参考见下

2022-10-17 15:20:28

1.1 FPGA双沿发送之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿发送之Verilog HDL实现;5)结束语。1.1.2 本节

2021-07-26 06:20:59

1.1 FPGA双沿采样之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿采样之Verilog HDL实现;5)结束语。1.1.2 本节

2021-07-26 07:44:03

那位高手用fpga驱动过DAC7724,或者是多通道的数模转换IC也可以,指导一下他们控制的时序是怎么样的。要是有Verilog就好了

2011-11-13 12:21:02

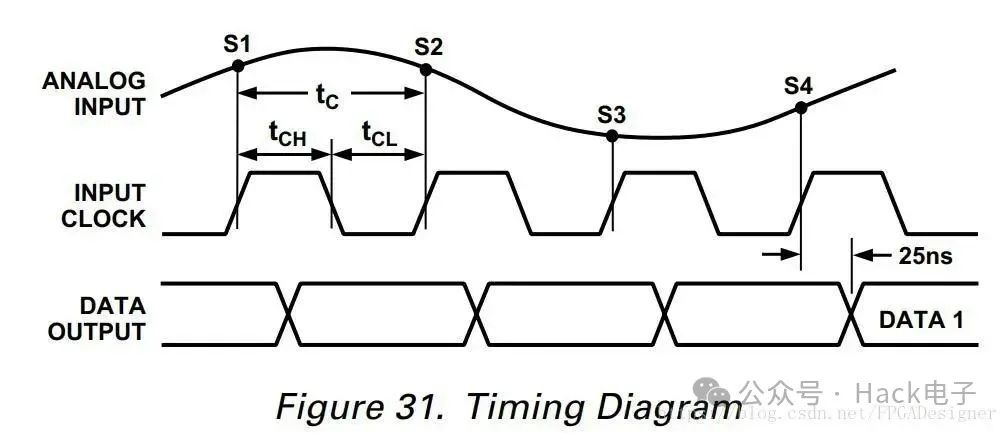

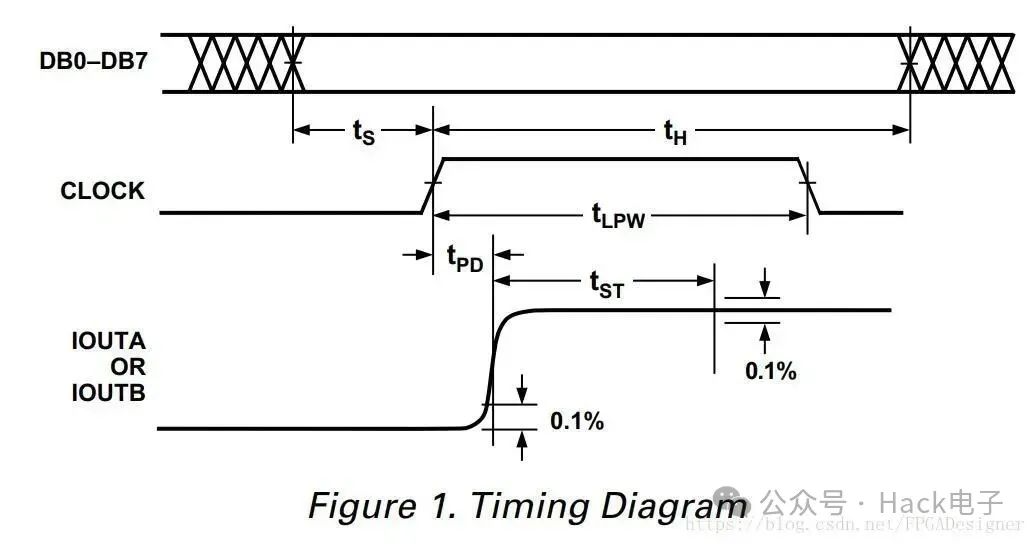

概述ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA

2020-09-27 09:40:08

Verilog并行CRC校验

2012-08-20 21:52:15

`我在一个小练习中需要处理图像数据,一帧的图像是并行进来的,如下图所示:一帧总共有几千个pixel。假设说我想给每一个pixel乘上一个不同的系数(使用乘法器实现),乘法器是流水线结构。请问有没有

2017-11-10 14:03:48

本帖最后由 eehome 于 2013-1-5 10:03 编辑

fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点

2012-08-11 18:27:41

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

型结构FIR,实现时可以采用并行结构、串行结构、分布式结构,也可以直接使用Quartus和Vivado提供的FIR IP核。本篇先介绍并行FIR滤波器的Verilog设计。设计参考自杜勇老师

2020-09-25 17:44:38

等串行总线接口只能实现FPGA 和ARM 之间的低速通信 ;当传输的数据量较大.要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输.

2019-09-17 06:21:10

使用Verilog实现基于FPGA的SDRAM控制器

2012-08-20 19:35:27

请问怎么实现ADC采集DAC引脚处的电压并串口打印我已经实现ADC采集引脚处的电压串口打印和DAC串口打印设定的电压值(如下图)我想进一步实现ADC采集DAC引脚处的电压并串口打印 而不是ADC和DAC打印出的电压毫无联系

2022-08-23 10:23:21

大家好,我需要一个具有以下规格的FPGA:-ADC和DAC。 DAC输出应为直流耦合。我可以为此目的买一张子卡。-FPGA应具有MHz范围内的内部时钟。 - 闪存或在开机时从用户设置初始化的能力

2019-09-25 12:53:23

在pcb设计中FPGA与高速并行DAC的布线应该注意什么?

2023-04-11 17:30:54

FPGA数字信号处理——基于FPGA和高速DAC的DDS设计与频率调制(一)——X现如今,随着高速模数-数模转换技术和FPGA的发展。FPGA的高速性、并行性、高数据吞吐量与高速数模-模数转换技术

2021-07-23 08:06:59

混合信号测试的特点和测试要求是什么如何实现对ADC/DAC的静态和动态特性的测试?基于DSP的混合信号测试方案

2021-04-09 06:18:19

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

将具有信号处理功能的FPGA与现实世界相连接,需要使用模数转换器(ADC)或数模转换器(DAC)一旦执行特定任务,FPGA系统必须与现实世界相连接,而所有工程师都知道现实世界是以模拟信号而非数字信号

2019-09-19 07:51:05

嗨,我是SPI DAC的新手,所以我发布了解决问题的方法。我正在使用FPGA实现4-PAM生成。流程如下。我已经在我的硬件中使用并行DAC生成了4-PAM但是我也试图在FPGA中对我的设计进行原型

2019-08-05 10:41:06

有没有具有1个通道12位的ADC,4个通道14位DAC的模块,板子上有FPGA的板子;或者有没有具有1个通道12位的ADC,4个通道14位DAC的模块

2016-12-08 15:10:45

, 双向数据端下图为DAC7621的时序:并行的DA还是蛮容易写的,直接送数即可,下面是FPGA Verilog HDl的部分代码:s1: begin cs

2016-01-16 14:57:23

怎么实现基于FPGA的dac控制?

2021-11-02 07:32:32

大家好!!!我有一个virtex-6 Xc6vlx240T fpga和一个FMC150卡。 。我也是FMC150的mmcx / ssmc连接器。我无法找到访问DAC和ADC的解决方案以及此卡的接口

2020-06-15 09:57:34

嗨,大家好!我正在使用FPGA Spartan 6评估套件,我需要将其与我设计的包含ADC和DAC的不同电路板连接。通过研究,最常用的接口是并行LVDS,串行SPI接口和JESD204B。所以,我

2019-08-05 07:38:33

最近在做个课题,需要用FPGA中的verilog语言实现BPSK调制,fpga不是很会,望大神指导下,急求代码啊!谢谢

2013-03-06 18:12:36

我急需一款FPGA和可以连接的ADC和DAC模块,FPGA不需要太高端,ADC要求至少12位,采样率几MHz都可以,DAC要求至少4通道,14位的。主要用于数字信号处理方面的FFT运算和数值比较。求大神推荐,谢谢!

2016-12-07 12:42:57

的用户指南中找到详细说明。这是我的问题。1. ADC / DAC能否在8通道模式下同时工作?如果可以的话,这种模式下可实现的最大采样率是多少?2.根据用户指南,ADC和DAC分别具有12位和14位分辨率

2019-10-23 09:15:22

如图所示,ADC采集被测电压,到FPGA在FPGA中进行运算之后,再输出运算后的电压,由DAC完成数模转换如果我的ADC的吞吐率和DAC的吞吐率不一致,比如ADC吞吐率为1.5MSPS,而DAC的吞吐率为1MSPS,会出现什么情况?怎么解决?

2017-04-12 19:55:12

嗨,我正在使用Spartan 3E入门套件,我正在尝试同时使用板载ADC和DAC。我试图从ADC获取样本并通过一个样本向DAC提供一个样本。 ADC工作正常,但我无法启动DAC。有人可以给我一些建议

2019-05-31 07:52:46

嗨,您能指定哪种ADC / DAC适合Spartan 3AN入门套件吗?是否有任何生产(由任何公司)并行ADC或并行DAC接口卡,我可以使用FX2 FMC连接器连接到FPGA板?TI认为Virtex

2019-06-20 14:07:24

本人在研究所工作多年,从事了大量高端ADC和DAC的研制工作,有多种现成的板卡,欲寻合作者,非诚勿扰!主要产品有:(1)DAC产品:(a) 基于Euvis公司 MD662H的高性能任意信号产生器

2013-06-08 09:51:31

。我们从时钟发生器的不同端口提供FPGA,ADC和DAC。 ADC接口以源同步模式运行,数据相对于DCO信号锁存,来自ADC和数据。在FPGA内部,我们使用FIFO交叉时钟域。到目前为止ADC部分还不

2020-03-12 11:12:21

采用 Verilog HDL 语言在Altera 公司的FPGA 芯片上实现了RISC_CPU 的关键部件状态控制器的设计,以及在与其它各种数字逻辑设计方法的比较下,显示出使用Verilog HDL语言的优越性.关键词

2009-08-21 10:50:05 69

69 ADC和DAC基础:ADC和DAC基础第一部分,ADC和DAC基础第二部分,ADC和DAC基础第三部分,ADC和DAC基础第四部分,ADC和DAC基础第五部分。

本系列文章分为5个部分,第一部分介绍采样的

2009-09-23 19:08:24 0

0 ADC及DAC的历史进程概况

本文以ADC的分辨率及采样频率,超高速、高性能DAC,便携式的需要,AV系统中的ADC及DAC及微系统这几个方面介绍ADC及DAC的一些

2010-02-26 15:06:57 1930

1930

ADC/DAC,ADC/DAC的原理是什么?

产生原因 随着现代科学技术的迅猛发展,特别是数字系统已广泛应用于各种学科领域及日常生活,微型计

2010-03-26 10:34:07 21474

21474 本站提供的fpga实现jpeg Verilog源代码资料,希望能够帮你的学习。

2011-05-27 15:09:53 200

200 本文介绍的基于PCI总线的FPGA计算平台的系统实现:通过在PC机上插入扩展PCI卡,对算法进行针对并行运算的设计,提升普通PC机对大计算量数字信号的处理速度。本设计采用5片FPGA芯片及

2011-08-21 18:05:31 1970

1970

adc: Analog-to-Digital Converter的缩写,意思是模/数转换器。实现把模拟信号转变为数字量的设备称为模数(A/D)转换器,简称ADC 实现把把数字量转变为模拟量的设备称为数模(D/A)转换器,DAC(Di

2012-09-18 10:21:10 51695

51695

基于EP1C3的FPGA程序之seg7_verilog

2016-01-20 15:22:50 11

11 FPGA_52_I2C_ADC_DAC,好东西,喜欢的朋友可以下载来学习。

2016-02-22 15:55:17 0

0 FPGA_51_I2C_ADC_DAC,好东西,喜欢的朋友可以下载来学习。

2016-02-22 15:55:23 0

0 FPGA_Verilog学习资料 part1。

2016-03-14 14:28:54 47

47 FPGA_Verilog学习资料 part2。

2016-03-14 14:27:50 36

36 FPGA_Verilog学习资料 part3。

2016-03-14 14:24:16 29

29 FPGA_Verilog学习资料,part4。

2016-03-14 14:23:30 9

9 关于fpga和LCD方面的知识,verilog实现的LCD显示的设计

2016-05-16 18:04:33 47

47 (ebook) Chu - FPGA Prototyping Using Verilog Examples

2016-06-03 16:16:53 14

14 Xilinx FPGA工程例子源码:在FPGACPLD中实现AD或DA的文章(英文Verilog)

2016-06-07 15:07:45 17

17 用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 基于EP1C3的FPGA程序之seg7_verilog

2016-11-18 16:05:02 0

0 许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能的ADC和DAC进行接口,比如

2017-02-09 05:45:01 1621

1621

基于FPGA Verilog-HDL语言的串口设计

2017-02-16 00:08:59 35

35 FPGA verilog 相关设计实践

2017-09-06 11:19:34 32

32 本文介绍了FPGA电源设计并行工程的合理性,讲解了并行工程(CE)技术及其作用,讨论了FPGA电源系统设计的复杂性和不确定性。

2017-10-13 13:00:35 5

5 许多数字处理系统都会使用FPGA,原因是FPGA 有大量的专用DSP 以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA 都要和高性能的ADC和DAC 进行

2017-10-18 14:41:17 43

43 将具有信号处理功能的FPGA与现实世界相连接,需要使用模数转换器(ADC)或数模转换器(DAC) 一旦执行特定任务,FPGA系统必须与现实世界相连接,而所有工程师都知道现实世界是以模拟信号而非

2017-12-12 11:19:17 2

2 许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能的ADC和DAC进行接口,比如e2v

2018-10-31 17:24:08 10818

10818 FPGA开发和数字IC设计十分相似,而两者最基础是verilog代码设计,verilog是硬件描述语言,实现的数字电路具备硬件并行处理的优点,

2021-03-10 14:31:33 2012

2012 提出了一种基于FPGA实现的全并行结构FFT设计方法,采用XILINX公司最新器件VirtexII Pro,用硬件描述语言VHDL和图形输入相结合的方法,在ISE6.1中完成设计的输入、综合、编译

2021-03-31 15:22:00 11

11 FPGA设计中DAC控制的Verilog实现图文稿(ltspice 放置电源)-该文档为FPGA设计中DAC控制的Verilog实现图文稿资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-26 12:17:02 10

10 FPGA设计中DAC控制的Verilog实现(单片机电源维修)-该文档为FPGA设计中DAC控制的Verilog实现资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-26 12:18:48 18

18 FPGA设计中DAC控制的Verilog实现修订稿(空调电源芯片)-该文档为FPGA设计中DAC控制的Verilog实现修订稿资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-26 13:13:56 10

10 ADC0809驱动FPGA实现的verilog程序(通讯电源技术杂志封面)-该文档为ADC0809驱动FPGA实现的verilog程序总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-08-31 18:33:38 60

60 FPGA CPLD中的Verilog设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的Verilog设计小技巧

2021-09-18 16:49:18 35

35 的完整 Verilog 代码 。 在这个FPGA Verilog项目中,一些简单的处理操作都是在Verilog中实现的,比如反相、亮度控制和阈值操作。图像处理操作由“parameter.v”文件选择

2021-09-23 15:50:21 5111

5111 ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和并行DAC芯片。

2022-04-21 08:55:22 5774

5774 FPGA需要良好的数电模电基础,verilog需要良好C语言基础。

2023-05-11 17:30:07 1308

1308

FPGA需要良好的数电模电基础,verilog需要良好C语言基础。

2023-05-22 15:04:29 484

484

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 653

653

本文详细描述了FPGA实现图像去雾的实现设计方案,采用暗通道先验算法实现,并利用verilog并行执行的特点对算法进行了加速;

2023-06-05 17:01:45 862

862

点击上方 蓝字 关注我们 许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能

2023-07-13 12:00:02 2809

2809

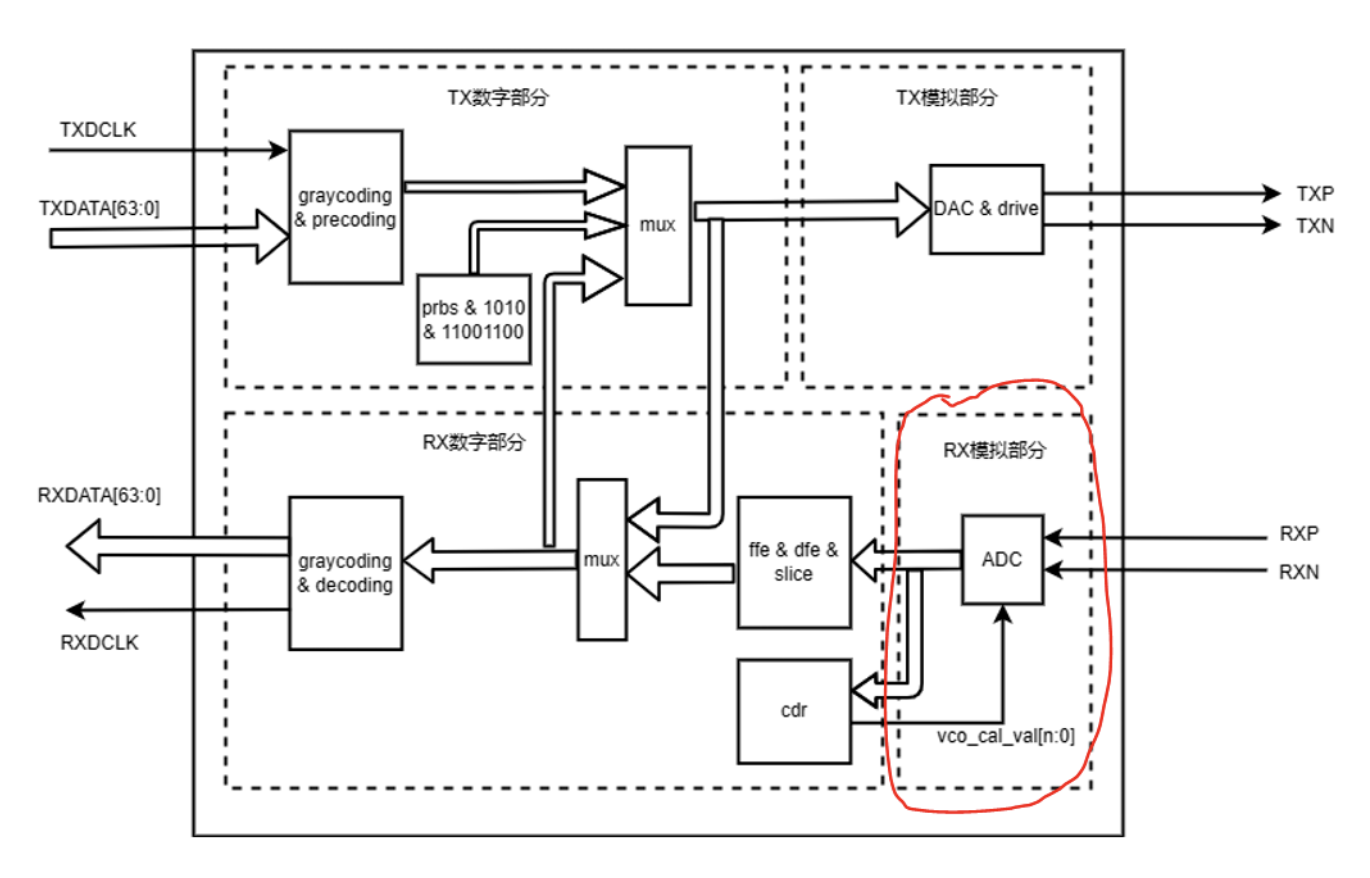

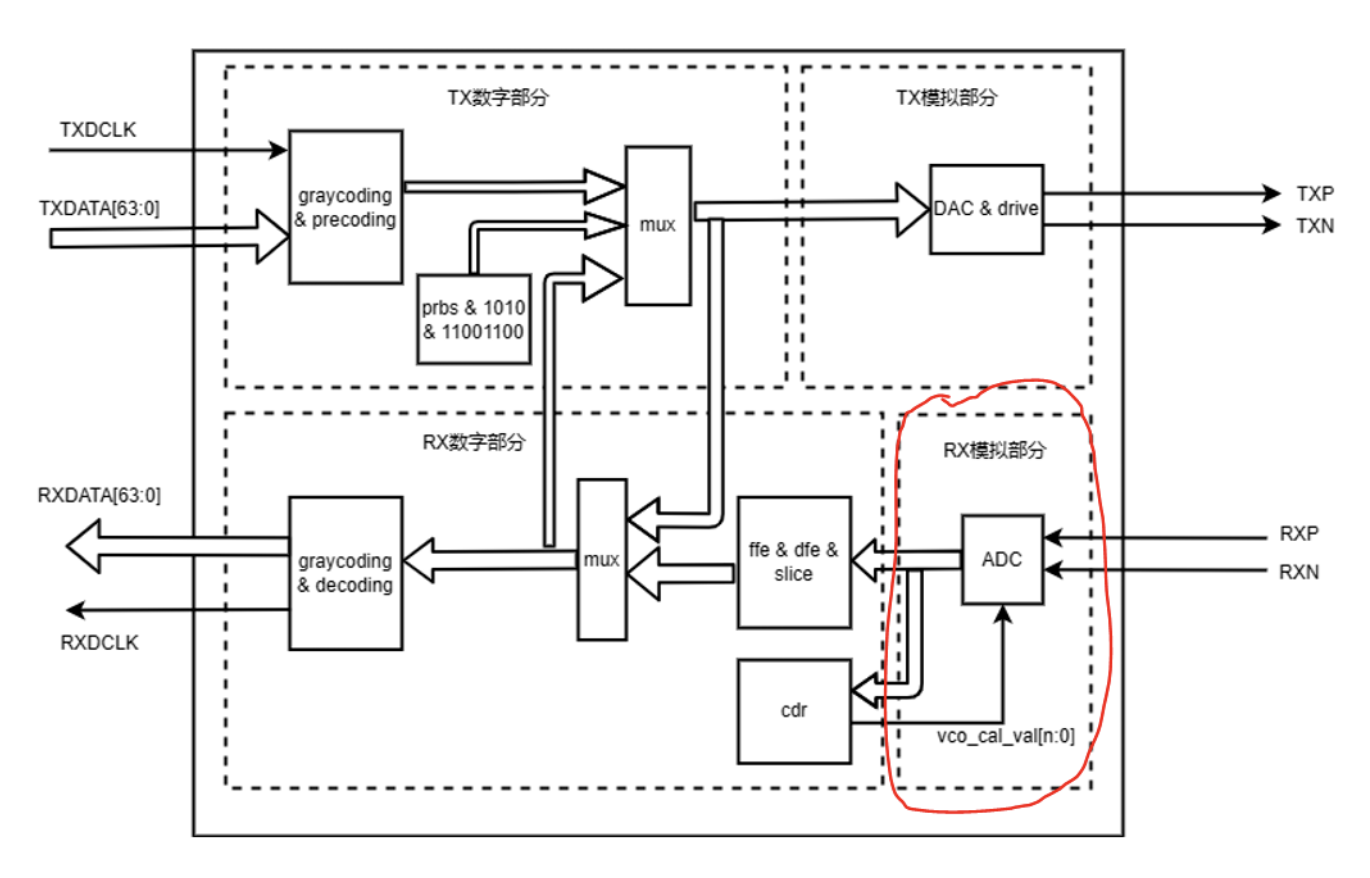

对于图1所示TX/RX模拟部分的实现方式,大家是不是一直有这样的疑问: Serdes在将并行data通过DAC串行发出去的时候,或者在接收端通过ADC进行串行data采样的时候,是怎么实现的?比如56G的serdes就是用56G的ADC和DAC吗?

2023-09-08 15:59:59 891

891

并行接口的ADC、DAC的测试方法 ADC和DAC是两种最常见的数据转换器,用于模数(ADC)和数模(DAC)转换。在进行并行接口的ADC和DAC测试之前,我们需要了解并行接口的工作原理以及测试

2023-11-07 10:21:45 857

857 中的for循环也是并行执行的。 Verilog中的for循环可以用来实现重复的操作,例如在一个时钟周期中对多个电路进行操作。在循环内部,多个语句可以同时执行,而不受循环次数的限制。这种并行执行的机制使得Verilog在硬件设计中非常高效和灵活。 在Verilog中,for循环有两

2024-02-22 16:06:23 307

307

电子发烧友App

电子发烧友App

评论