本文将对源同步定时如何优化高速接口时序裕量进行讨论。时序预算是对系统正常工作所需时序参数或时序要求的计算。

2012-03-20 10:46:32 2449

2449

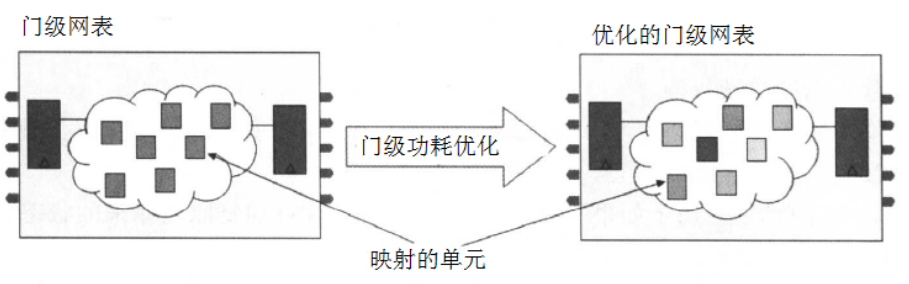

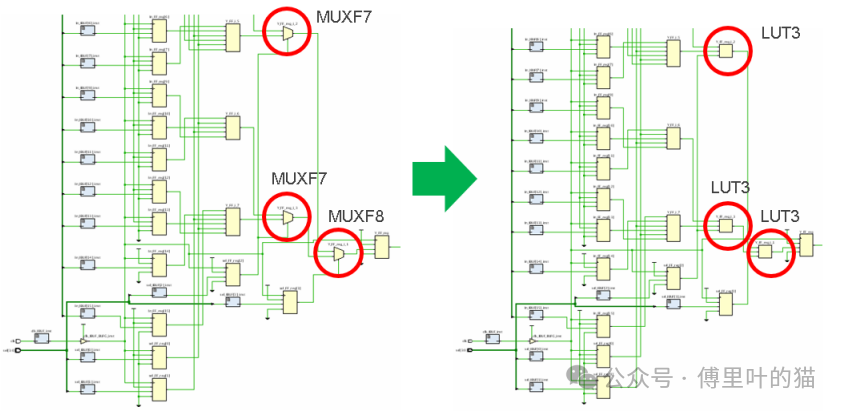

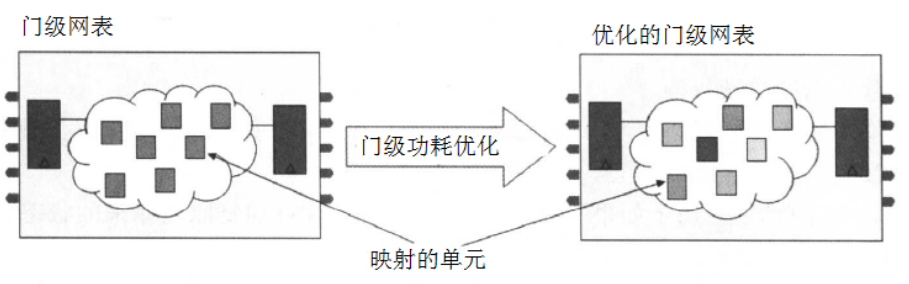

门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时设计保持其性能,即满足设计规则和时序的要求。

2020-07-02 16:28:31 4954

4954

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2783

2783

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1408

1408 引言:本文分享一篇技术PPT,该PPT主要介绍如何将算法映射到FPGA或ASIC硬件架构。

2023-01-30 17:37:11 1900

1900 在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1271

1271 前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 862

862

在单片机开发中,内存优化是至关重要的,它不仅能够降低成本,还可以提高性能。本文将深入讨论如何在STM32单片机和C语言的环境中实施内存优化策略,以确保项目的顺利进行。

2023-08-21 09:21:45 1062

1062

这篇文章是探讨对接收端进行时序优化(即ready打拍,或称backward打拍)的方式。

2023-12-04 10:20:55 243

243

FPGA系统设计实质上是一个同步时序系统的设计,理解时序概念,掌握代码优化与综合技术,正确完整地进行时序约束和分析是实现高性能系统的重要保证。很多同学在设计中都会碰到时序方面的问题,如何解决时序难题

2018-06-07 15:52:07

时间,降低了制造成本。直观的逻辑合成环境包括先进的优化技术、屡获殊荣的时序分析和先进的推论技术,适用于与供应商无关的设计中,可加快产品上市时间、消除设计缺陷以及提供极佳的结果质量 (QoR)。 FPGA

2018-09-20 11:11:16

如今,FPGA 功能强大且管脚数目极大,可为工程师提供大量机会来提升特性和功能,同时还能降低产品成本。随着复杂度增加,将这些器件集成到印刷电路板也成为了一项严峻的挑战。数百个逻辑信号需映射到器件

2019-10-09 07:15:30

,所以测不出来2 时序频率太高了,FPGA已经Hold不住了,应该降低频率请有经验的同志们帮我看看可能是什么原因。在此献出我的积分了。。。

2016-09-14 17:36:45

起点(即时钟触发器输入端口)

(2)路径终点(即输出端口的寄存器或查找表单元)

(3)逻辑电路和逻辑器件

有了这些元素,就可以构建完整的时序路径。在实践中,我们可以使用FPGA工具来分析、优化

2023-11-15 17:41:10

FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束

2016-06-02 15:54:04

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

同步复位,可以降低资源的使用和功耗,有助于时序收敛。由于FPGA的初始状态是确定的(可以在定义说明中指定),为了更快地时序收敛,官方文档认为,能不用复位是最好的,尤其数据路径和移位寄存器的设计中。不过

2020-12-23 17:42:10

VGA驱动接口时序设计之7优化本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt最后,再次编译系统,查看时序

2015-08-10 15:03:08

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

FPGA 设计优化主要分为编码风格、设计规划和时序收敛三大部分,这 些因素直接决定了 FPGA 设计的成败。 编码风格直接影响 FPGA 设计的实现并最终影响设计的性能。尽管综合 工具集成

2022-09-29 06:12:02

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

速度优化是指在充分掌握软硬件特性的基础上, 通过应用程序结构调整等手段来降低完成指定任务所需执行的指令数。在同一个处理器上, 经过速度优化的程序比未经优化的程序在完成指定任务时所需的时间更短,即前者比

2011-07-07 11:06:42

人工智能大热之前,Cloud或Data Center已经开始使用FPGA做各种加速了。而随着Deep Learning的爆发,这种需求越来越强劲。本文主要讨论Cloud巨头Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

近年来,世界上许多大软件公司纷纷推出各种Linux服务器系统及Linux下的应用软件。目前,Linux 已可以与各种传统的商业操作系统分庭抗礼,在服务器市场,占据了相当大的份额。本文分别从磁盘调优,文件系统,内存管理以及编译优化等方面来论述 Linux系统的优化调优策略。

2019-07-16 06:23:35

上次我发过一个帖子已经得到解决,目前的情况是FPGA的时序有问题。板子是VGA转HDMI的,经过CAT9883C芯片下游到Sil9134,出来的高清图像一直有水波纹。查资料说是FPGA,有的说要改代码。有的说改板子上东西。有没有大佬看一下我的板子帮个忙。。。

2017-10-31 16:54:41

InTime 利用大数据分析和人工智能,建立时序数据库,无需修改源代码即可优化设计,为工程师推荐最佳工具参数组合。了解更多>>

2017-04-18 14:53:40

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

整体对这软件评价是,优化功耗的时候不能有很大提升,但优化时序还是不错的,这款软件不仅可以优化时序,还可以对工程进行工作频率的适当提升。很感兴趣他们的private cloud编译方式。收到

2017-06-30 15:28:28

解决FPGA时序优化问题的软件。InTime 内嵌学习引擎,可以智能分析FPGA设计,为综合和布局布线提供更优的策略组合。同时,根据对器件、设计和工具特点的了解,以及独有的算法,InTime 可以生成最能满足

2017-07-05 11:00:48

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2019-08-11 08:30:00

映射后需要对一个设计的实际功能块的延时和估计的布线延时进行时序分析;而在布局布线后,也要对实际布局布线的功能块延时和实际布线延时进行静态时序分析。从某种程序来讲,静态时序分析可以说是整个FPGA设计中最

2021-05-27 09:28:40

提出有效的PPA优化方案。其实这一条经验是并不特指高频设计,是做好设计的基本功,缺陷率高同学往往问题就出现在这里。2.建立把代码通过人脑转化成电路的能力。verilog描述的就是电路,时序优化也是在电路

2022-06-23 15:43:18

特定模块划分到不同的时钟域里;但异步时钟域不宜太多。综合时使用retiming,duplication;physical synthesis优化,现在的综合器这方面已经足够聪明了。预算允许可使用速度更快的芯片;这个也许是实现 “不修改RTL又时序收敛” 的最可能的方式。

2018-06-07 17:55:37

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2021-05-18 15:55:00

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重

2012-05-23 19:59:34

。掌握分析和确定关键路径时序的方法,并通过分析找出关键路径的时序问题,再对关键路径进行优化,通过RTL层面的不断优化,不断修炼自己的设计能力,让设计出来的电路更为靠谱有效!本资料属大西瓜FPGA开发团队,在此开源,与大家一起学习FPGA!

2017-02-26 09:42:48

您好,如果我想为我的设计获得最佳时序收敛,我应该使用什么实施策略?例如,如果我想改善设置和保持的松弛度,我应该选择哪种最佳策略?以上来自于谷歌翻译以下为原文Hello,If i want

2018-11-05 11:40:14

Hi,以前在学校的时候就经常遇见时序收敛的问题,尤其是改RTL好麻烦啊。工作以后和朋友们一起做了个时序优化的软件,叫InTime,希望可以帮助有相同问题的朋友。^_^我们搞了免费试用的活动,有兴趣

2017-05-11 10:55:17

本帖最后由 alasga 于 2016-1-30 15:56 编辑

附件有3部分:1、时序分析基本模型;2、如何设计好的时序;3、整体的时序策略。

2016-01-30 15:52:57

设计一个高性能的HLS, 可以用任何优化策略,在保持函数功能的同时尽可能提高性能。希望论坛里的大神给予具体优化的指导,最近几天调试太费劲了,希望大神给予保罗loop unroll, pipeline

2016-08-27 21:11:26

虚拟同步发电机双机并联系统的参数自调节优化控制策略有哪些?

2021-11-04 07:20:27

触摸屏知识及软件优化策略

2012-08-20 10:04:54

1. FPGA时序的基本概念FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是

2019-07-09 09:14:48

新手,需要对一个工程时序优化,现在只能到110MHZ, 需要到150MHZ以上,跪求时序优化资料或例程。。

2015-12-05 11:22:54

设计保持其性能,即满足设计规则和时序的要求。功耗优化前的设计是已经映射到工艺库的电路,如下图所示: 门级电路的功耗优化包括了设计总功耗,动态功耗以及漏电功耗的优化。对设计做优化时,...

2021-11-12 06:14:26

变则通,通则久。事物都有其运行的规律,把握好规律,就能更好的实现人的目的。在数字后端设计中,时序优化一直是关键问题,尤其追求高频高性能的设计中,时许问题常常贯穿始终。大大小小二十几个项目模块后端工作

2020-12-10 07:37:31

在基于相似度计算的本体映射中,相似度计算量大的主要原因是待映射概念和待计算属性过多。该文采用过滤策略,利用候选映射策略和信息增益策略减少待映射概念和待计算属性

2009-04-14 09:15:23 29

29 本文分析了传统名称策略在本体映射中的不足。针对此问题,提出了一种新的基于WordNet 名称策略算法,该算法实现名称核心词汇的WordNet 定位用以消除词义模糊性,从而提高词相似

2009-07-08 09:09:43 13

13 如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单

2009-04-15 14:19:31 663

663

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1170

1170 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 很好的FPGA资料,基础的资料,快来下载吧

2016-09-01 16:40:07 34

34 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 低成本BIST映射电路的设计与优化_张玲

2017-01-07 21:39:44 2

2 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2017-02-09 01:59:11 266

266 fpga时序收敛

2017-03-01 13:13:34 23

23 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2333

2333

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2970

2970 作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4908

4908

在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑

2017-11-24 20:12:54 1523

1523 摘要:基于云环境下的科学工作流,以提高处理机利用率、降低费用为目标,提出了一种基于聚簇的执行优化策略。该策略首先基于合理的任务复制和分簇,以实现关键任务的尽早调度;在此基础上,对任务簇再次进行聚集

2018-01-08 11:06:11 0

0 合理的电力网架恢复策略对大停电后电力系统的快速恢复具有重要意义。采用时序恢复策略进行电力网架恢复,分步进行机组启动顺序优化和路径恢复顺序优化。第一步以网架恢复时间内系统发电能力最大为目标优化机组启动

2018-01-14 11:10:57 17

17 传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

2018-02-26 10:09:04 0

0 FPGA时序收敛让你的产品达到最佳性能!

2018-04-10 11:38:48 18

18 FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4161

4161

FPGA设计中,层次结构设计和复位策略影响着FPGA的时序。在高速设计时,合理的层次结构设计与正确的复位策略可以优化时序,提高运行频率。

2019-02-15 15:15:53 851

851 万幸的是,当今FPGA工具(比如Xilinx的 Vivado)都有很多开关和设置选项来帮助时序收敛。InTime的方法,就是通过调整FPGA工具的编译过程来解决用户的时序问题和其他性能问题。

2019-07-26 15:56:23 3210

3210

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 17

17 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 19

19 ,分别设计 Simple、 Multiple(k)、M(u)和 Relation算法,以此构建任务映射虚拟机选择的数学模型基于 Cloudsim模拟器的实验结果表明,通过该策略优化虚拟机选择与放置过程,可减少云数据中心的能量消耗和虚拟机迁移次数,节省云服务提

2021-05-25 14:29:18 17

17 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 4424

4424 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-10-11 10:23:09 4877

4877

索引使用策略及优化 MySQL的优化主要分为结构优化(Scheme optimization)和查询优化(Query optimization)。本章讨论的高性能索引策略主要属于结构优化范畴。本章

2021-11-02 15:13:42 1435

1435

设计保持其性能,即满足设计规则和时序的要求。功耗优化前的设计是已经映射到工艺库的电路,如下图所示: 门级电路的功耗优化包括了设计总功耗,动态功耗以及漏电功耗的优化。对设计做优化时,...

2021-11-07 11:05:59 19

19 1、如何降低功耗?

(1) 优化方向:

组合逻辑+时序逻辑+存储

(2) 组合逻辑:

(a)通过算法优化的方式减少门电路

(b)模块复用、资源共享

(3) 时序逻辑:

(a)尽量减少无用

2022-02-11 15:30:36 2

2 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3264

3264

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1329

1329

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2107

2107 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 3499

3499

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 3011

3011

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2409

2409

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 793

793 STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 372

372

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 357

357

FPGA时序不收敛,会出现很多随机性问题,上板测试大概率各种跑飞,而且不好调试定位原因,所以在上板测试前,先优化时序,再上板。

2023-06-26 15:41:31 1182

1182

FPGA高级时序综合教程

2023-08-07 16:07:55 3

3

电子发烧友App

电子发烧友App

评论