初始化时存入数据。那在IP核rom中存放大量数据对FPGA有什么影响,比如我想存65536个16位的数,然后在64M或者128M的时钟下读出来。会不会导致FPGA速度过慢?

2013-01-10 17:19:11

有某试验数据,用matlab求fft之后再求得的功率谱密度是这样的:图1但是用fft ip核,取前4096个数据,得到fft之后的结果是这样的:图2求功率谱密度得到的是这样的:图3试验数据都是零点几

2016-04-21 20:36:18

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA嵌入8051单片机 IP核编程,编写的c语言矩阵键盘程序可以在stc89c54单片机上正常工作,但是下载到FPGA中8051单片机ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

设计早期系统规划 365.3.综合和仿真技巧 375.3.1 综合工具XST的使用 375.3.2 基于ISE的仿真 425.3.3 和FPGA接口相关的设置以及时序分析 455.3.4 综合高手揭秘

2009-04-09 18:28:46

的封装355.1.7 器件的价格355.2 如何进行FPGA设计早期系统规划365.3.综合和仿真技巧375.3.1综合工具XST的使用375.3.2 基于ISE的仿真425.3.3 和FPGA接口相关

2012-02-27 15:44:02

本帖最后由 jf_25420317 于 2023-11-17 11:10 编辑

FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

当我们面对使用新IP核

2023-11-17 11:09:22

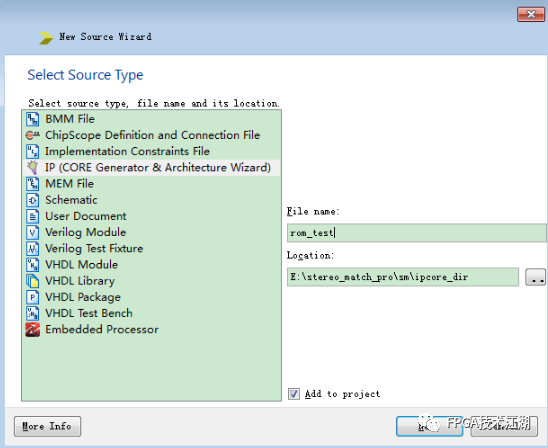

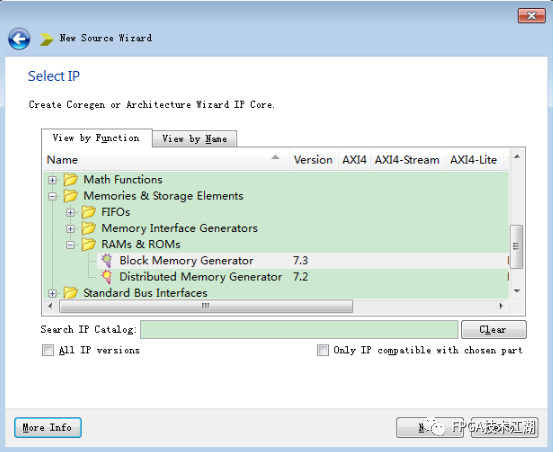

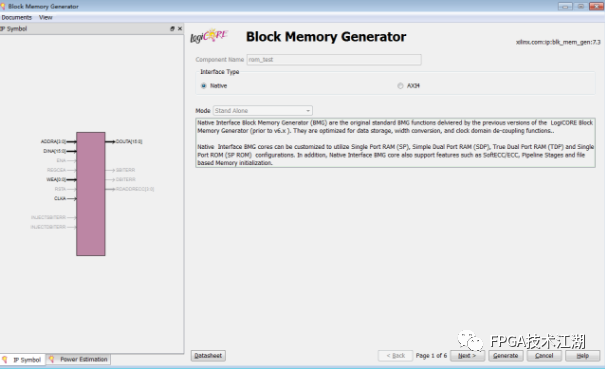

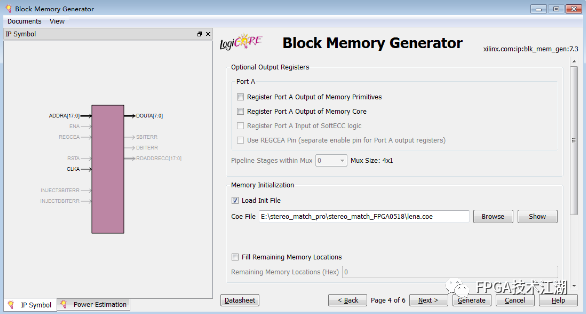

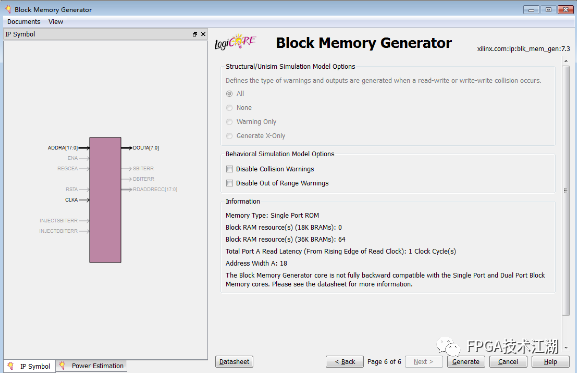

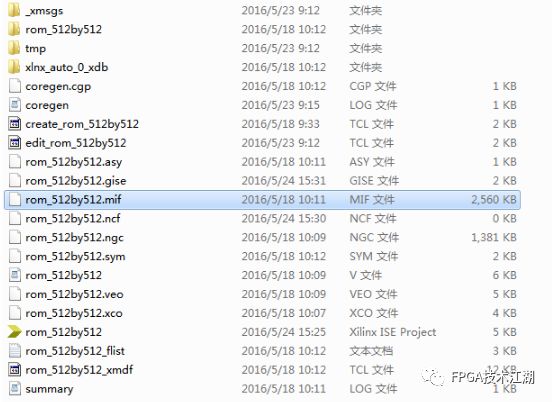

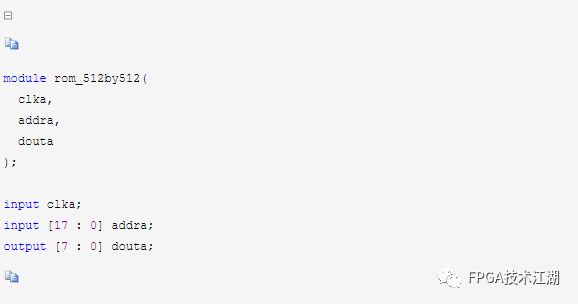

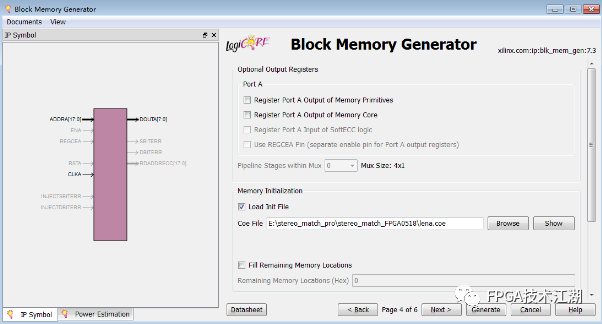

文档创建既然是ROM,那么我们就必须实现给它准备好数据,然后在FPGA实际运行时,我们直接使用这些预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配置。如图所示,我们可以创建一个名为

2019-04-08 09:34:43

说,上货。

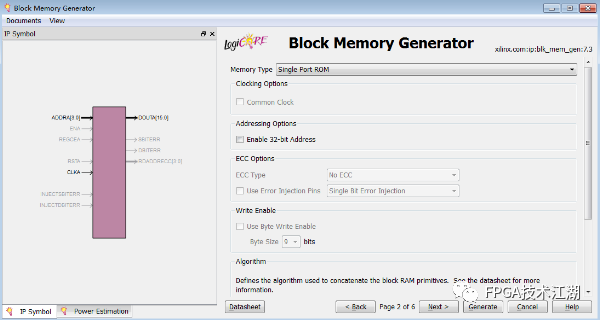

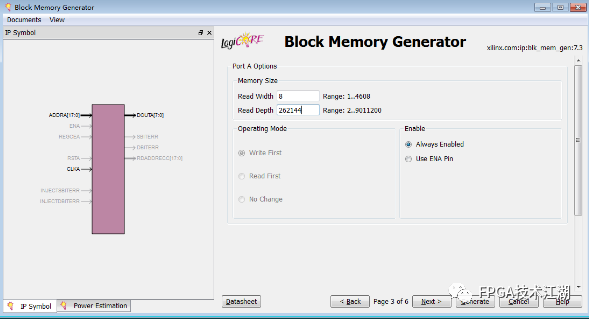

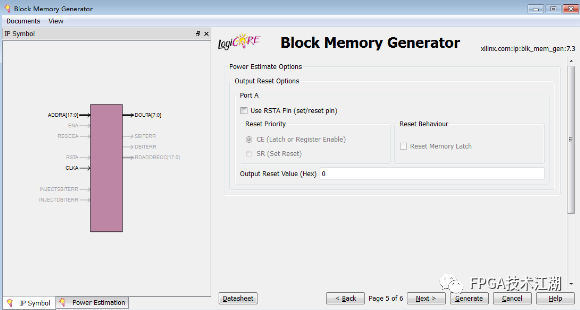

ROM使用教程

ROM的英文全称为Read-Only Memory,即只读存储器。可以从任意地址上读取数据,但是不能写入。那么我们ROM中的数据,就需要我们提前存放进去,在IP核中

2023-06-15 16:57:22

是利用FPGA片内嵌入的M9K构成的,所以不能够实现掉电不丢失。 由于设计ROM深度为256,故而地址的宽度为8位。 本次构建为ROM,所以在构建ROM之前应当首先设计好初始化文件(mif文件

2023-03-13 15:46:42

不多说,上货。IP CORE 之 ROM 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频

2023-04-07 20:09:59

本帖最后由 elecfans跑堂 于 2015-9-7 13:54 编辑

一个项目里有IP核rom,想改其中的参数重新生成,结果打开失败,然后我把它移除了,在项目里边新添加不了,提示如下错误

2015-09-07 12:21:59

创建test.vhd 和test_tb.vhd文件并添加到工程中,这里不细说如何创建HDL源代码。然后配置ISE的仿真器,右键选中FPGA芯片,点击properTIes,然后在Simulator选择

2019-06-03 09:11:11

ise FFT ip核的datasheet文档打不开什么原因

2015-08-27 14:46:45

请问哪位高手有ise软件中的各个ip核的功能介绍

2013-10-08 16:41:25

大家好,我正在寻找AWGN IP核,AWGN IP核似乎自2009年起停产。我相信在2009年之前下载早期版本的ISE应该有AWGN IP核,但在ise 9.1i它不存在。谁有任何建议可以找到已停产

2019-02-26 11:11:59

这次利用Xilinx公司的芯片做FPGA开发的时候用到了ROM,肯定要对ROM做仿真,经过了一天的努力,总算可以做仿真了,现在把过程写出来,供大家参考一下。1.首先需要编译XINLINX的库文件

2012-02-29 10:44:56

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

文件HRV_top。通过测试文件对设计文件进行功能仿真,仿真结果正确。但是当我对设计完成布局布线之后,没有其它错误,接着进行时序仿真,见图2. 在图2中,测试文件调用的RAM IP核(也就是RAM_fangzhen)怎么找不到啊??求高手解答。

2015-08-29 16:55:16

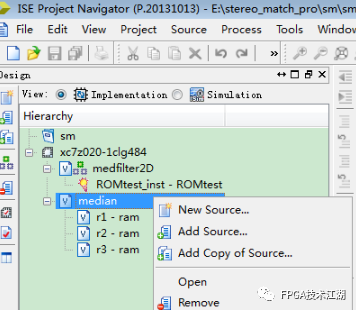

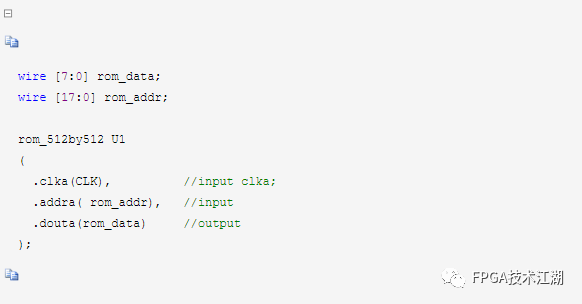

如图所示。●Pll_controller.v模块产生FPGA内部所需时钟信号。●Rom_test.v模块例化FPGA片内ROM,并产生FPGA片内ROM读地址,定时遍历读取ROM中的数据。●Chipscope_debug.cdc模块引出ROM的读取信号总线,通过chipscope在ISE中在线查看ROM读取时序。

2016-01-06 12:22:53

文档创建既然是ROM,那么我们就必须实现给它准备好数据,然后在FPGA实际运行时,我们直接使用这些预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配置。如图所示,我们可以创建一个

2016-01-08 13:12:44

路径。设定完成后点击“OK”回到ISE主界面。 2 功能仿真如图所示,双击“Simulate Behavioral Model”开始仿真。接着,Modelsim中我们可以查看读ROM的波形。这里需要

2016-01-11 12:17:28

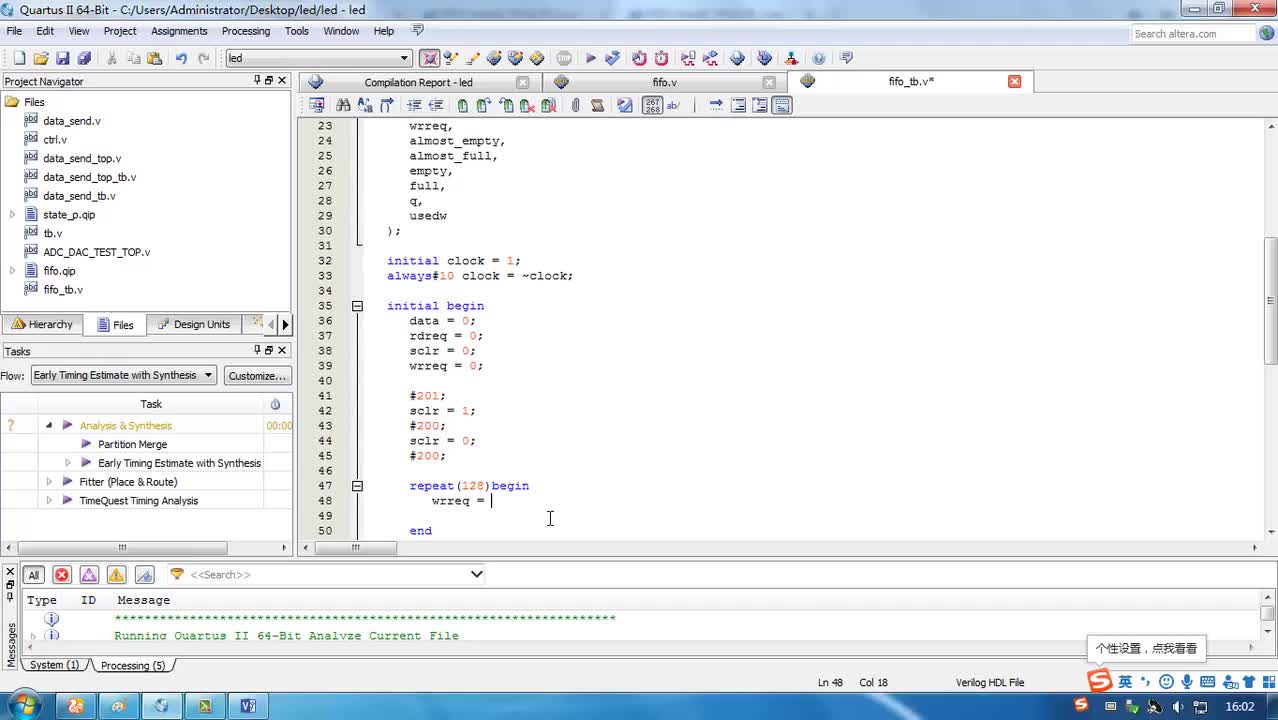

/1jGjAhEm 1 功能概述该工程实例内部系统功能框图如图所示。我们通过IP核分别例化了ROM、FIFO和RAM,ROM有预存储的数据可供读取,将其放入FIFO中,随后再读出送到RAM供读取。通过ISE集成

2016-03-16 12:43:36

`Xilinx FPGA入门连载60:FPGA 片内ROM FIFO RAM联合实例之功能仿真特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-18 09:20:25

`Xilinx FPGA入门连载74:波形发生器之IP核CORDIC(正弦波)功能仿真特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-25 08:33:11

1 功能概述该工程实例内部系统功能框图如图所示。我们通过IP核分别例化了ROM、FIFO和RAM,ROM有预存储的数据可供读取,将其放入FIFO中,随后再读出送到RAM供读取。通过ISE集成的在线

2019-01-10 09:46:06

文档创建既然是ROM,那么我们就必须实现给它准备好数据,然后在FPGA实际运行时,我们直接使用这些预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配置。如图所示,我们可以创建一个名为

2019-01-09 16:02:21

在仿真fft ip核时 输出信号一直为0,检查了输入波形,应该没有问题,大家帮忙看看吧输入是由rom里面的mif文件产生的信号。

2017-11-21 10:44:53

我用quartus II调用modelsim仿真fft ip核,仿真结束后我想验证下数据是否正确,结果是:我用matlab生成同样的整形数据,然后用modelsim仿出的结果txt文件与用

2012-09-20 12:48:37

modelsim 仿真 altera IP核(ROM,RAM实例)急求大神们ROM和RAM 的综合仿真代码

2015-11-19 21:02:57

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

本帖最后由 lee_st 于 2017-11-2 15:01 编辑

《FPGACPLD设计工具──Xilinx+ISE使用详解》第 1 章 ISE 系统简介

2017-11-02 10:02:32

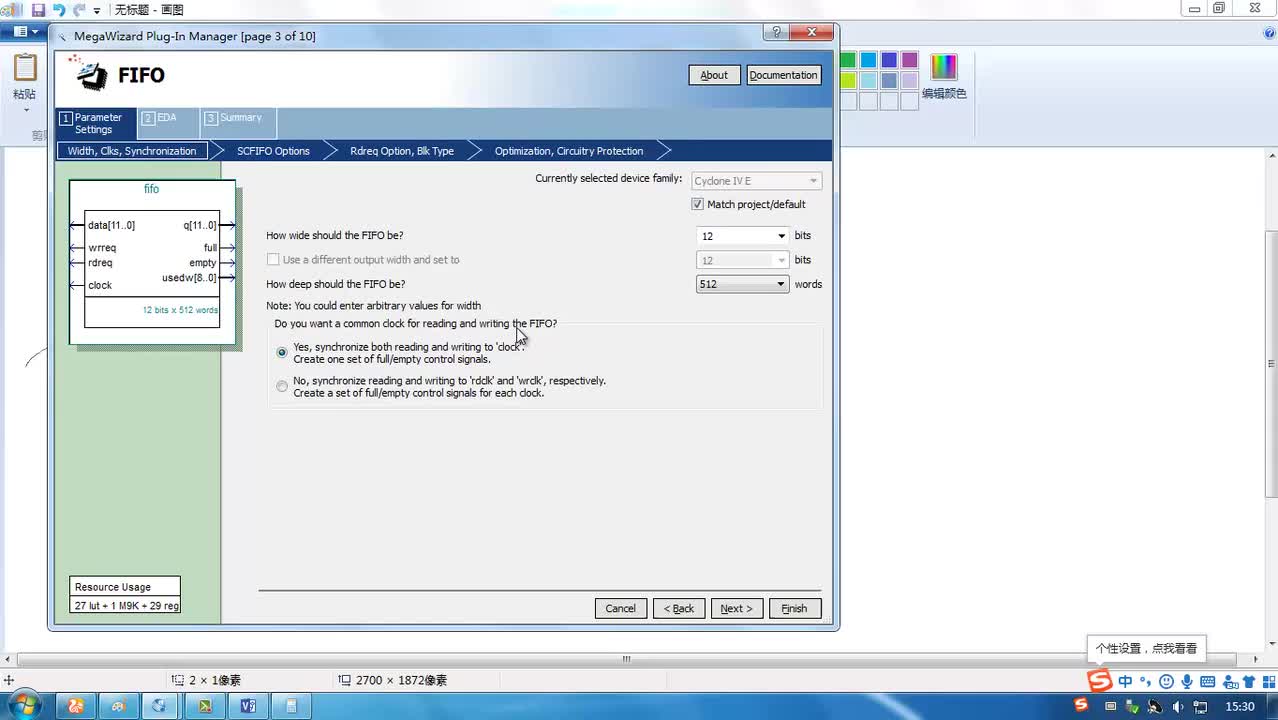

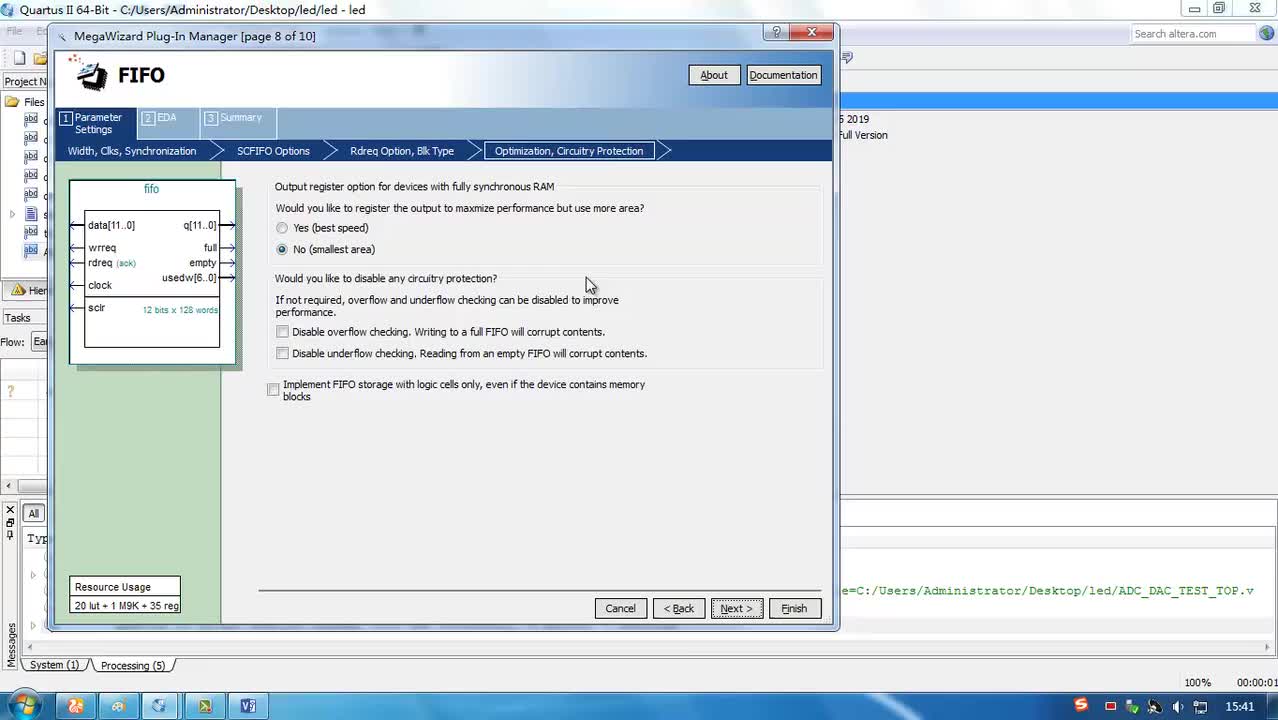

和创建包含定制IP核的设计文件,然后在设计文件中例化IP核。在Mega Wizard插件管理器中可以创建、定制和例化Altera IP核、参数化模型库(LPM)模块以及在Quartus II软件、EDA

2016-12-22 23:37:00

的使用4.5.3 Synplify Pro、ModelSim和ISE的联合开发流程4.5.4 ISE与MATLAB的联合使用4.6 Xilinx FPGA芯片底层单元的使用4.6.1 Xilinx全局时钟网络

2012-04-24 09:23:33

增加1,所以此时的mif文件中存放的是0到255)。在右侧的IP核搜索的编辑区,输入rom,在菜单栏找到并双击rom(在这里我们使用单端口的rom,双端口的rom,自己感兴趣的话,可以自己调用试一试

2019-12-16 17:18:30

,手把手演示工程创建,IP核调用、Testbench编写以及仿真验证,让每一个0基础的朋友都能快速跟上节奏。另外,有一定基础的朋友,其实也可以观看,因为在设计中,我已经将很多的设计小技巧穿插在视频中了。请

2015-09-22 14:06:56

的存储单元中,然后系统正常工作时,读出其中存储的数据。配置一人ROM的IP核,有三个步骤:参数设置、电子设计自动化、总结。理论的内容可以再仔细研读其他资料,这里以实践为主。新建一个mif文件,mif文件就是

2016-09-24 23:36:31

or negedge RST_N)beginif(!RST_N)addressRun Simulation Tool-- > RTL Simulation可以看到,数据的读取在第0ns时就读取,这是由于在配置ROM IP核时的Regs/Clken/Aclrs页面把q outputport.设置去掉了。

2016-09-25 09:58:23

前面建好了mif文件,下面就要创建ROM IP核了。首先,我们新建一个工程。菜单栏:Tools --> MegaWizardPlug-InManager ,点击“Next”选择ROM的IP核

2016-09-25 09:38:33

内建的示波器。SignalTapⅡ的使用要新建一个仿真调试文件。SignalTapⅡ可以设定信号的触发方式。其他请补充。另,FPGA的IP核并不是只有这几种,从新建IP核的界面可以看到,IP核还有很多。

2016-10-11 22:24:16

总是出来后几个地址的结果。。。如图,图一是ise仿真结果,addr为242时的结果为-1400(ip核有时延),但在matlab里看rom的内容242对应的是-1408(图二),-1400是后面3位

2018-12-08 11:37:00

和创建包含定制IP核的设计文件,然后在设计文件中例化IP核。在Mega Wizard插件管理器中可以创建、定制和例化Altera IP核、参数化模型库(LPM)模块以及在Quartus II软件、EDA

2019-03-04 06:35:13

新手见谅使用IP核设计了一个10阶3级的CIC滤波器,输入数据位宽12位,输出最大22位但是仿真出来的结果有种溢出的感觉,想不通是怎么回事,求各位前辈帮忙分析~~贴出来IP核设置界面,还有matlab处理的结果{:4_108:}

2013-10-13 16:56:12

本例程主要使用Vivado 调用ROM IP核,用含有正弦曲线的.coe文件初始化ROM,最终通过仿真实现波形的显示 一、首先建立工程 二、选择芯片的型号 我

2021-01-08 17:16:43

刚刚接触IP核做FFT,现在用的是FFTV9.0,已经建立了一个IP核,但是如何仿真呢?是用quartus自带软件,还是要用MATLAB?抑或其他?我用的自带软件,但是什么也没有出来。正确的办法应该怎样呢,谢谢指点。

2011-04-21 10:22:31

现在在做一个任意波形发生器的设计,先是用正弦波波形数据初始化的rom,能够显示出正弦波,后来用锯齿波的数据,再次初始化rom,仿真出来的波形还是正弦波。不知道为什么???

2015-09-29 11:46:35

利用system generator将ISE和MATLAB关联,但是打开simulink的过程中出现如下图情况 求问为何?过程中完全按照流程,分别给MATLAB以管理员权限,而且版本匹配,ISE14.7和MATLAB13a。

2017-12-26 21:51:55

quartus ii9.0创建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)这些文件都有用吗,想在其他工程里调用这些IP核,这几个文件全部要添加吗?

2013-07-02 17:20:01

用quartus ii 中自带的ip核创建了一个rom,并加载了初始的hex数据。当我从rom中读出数据的时候,发现前面两个地址(0000,0001)的输出数据不正确,0002输出数据是地址0000对应的数据,即地址偏移了2位,请教给位大虾这是怎么回事?应该如何解决?

2013-05-14 14:38:21

我在电子发烧友上看了小梅哥的fpga学习视频。看到rom那一节时,我按照视频讲解的方式调用了一个rom的ip核,编写了testbench文件。但是,得到的仿真结果rom中的数据全是0,mif文件没有问题,已经设置好了,请问问题出在哪里?求各位大神指教

2018-03-07 11:31:24

`最近做仿真需要用到Quartus ii里的ROM IP核,为了验证功能,我新建了工程,生成IP核,数据深度512,位宽8bit,用MATLAB产生512个随机整数,新建hex文件,将512个随机数

2015-12-22 23:14:53

本帖最后由 Laputa_fly 于 2013-11-23 13:46 编辑

用quartus9.0调用了altera FFT IP 核 生成了modisim 和 matlab 的仿真文件。用modelsim 仿真有结果。但是按照官方的使用说明用matlab仿真时出现问题。请大家帮忙解决一下。谢谢!

2013-11-23 13:43:41

最近在做一个FIR低通滤波器,利用Matlab 产生滤波系数,导入到Quartus中,再利用其中的FIR IP核进行滤波器设计,在采用分布式全并行结构时,Modelsim 仿真有输出;如果改为分布式

2018-07-05 08:33:02

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

FPGA片内ROM,并产生FPGA片内ROM读地址,定时遍历读取ROM中的数据;此外,图中未示意,该工程实例还包括了SignalTapII的IP核模块,该模块引出ROM的读取信号总线,可以在线查看ROM读取时序。 图9.20 ROM实例模块互联接口 `

2018-06-16 19:39:24

嗨,我想在EDK中使用ISE中提供的PCI Express IP核,这意味着我应该将所有ISE IP核的verilog模块导入EDK。这是可能的,如果可能的话请发送相关文件。谢谢&问候,Madhu.B

2020-03-24 08:14:50

飞舞,这里就不赘述了,以免有凑字数的嫌疑。下面我们就Matlab和FPGA两个工具双管齐下,比对Vivado的FFT IP核生成的数据。2 Matlab产生测试数据,绘制cos时域和频域波形

2019-08-10 14:30:03

基于FPGA的FIR滤波器IP仿真实例 AT7_Xilinx开发板(USB3.0+LVDS)资料共享 腾讯链接:https://share.weiyun.com/5GQyKKc 百度网盘链接

2019-07-16 17:24:22

受到业内人士的青睐。本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2019-07-04 06:02:19

过程2-参考代码解读Xilinx 仿真库编译FFT_Ip核数据手册解读FFT_IP核设计与调用Matlab设置ISE FIR滤波器系数FIR_Ip核数据手册解读FIR_IP核设计与调用[td]通过一个

2018-08-09 21:32:52

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

现有基于candence的AD的模拟电路,还有在ISE上用Verilog写的51单片机的IP核,怎样将AD挂载到51上进行仿真呀,谢谢各位大虾!!!

2012-07-13 15:45:11

入RAM。本实验将为大家介绍如何使用FPGA内部的ROM以及程序对该ROM的数据读操作。1.实验原理Xilinx在VIVADO里为我们已经提供了ROM的IP核, 我们只需通过IP核例化一个ROM,根据

2021-01-07 15:48:39

本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2021-05-08 06:22:32

本人现在有基于candence的10位AD模拟电路,怎样能转换成类似IP核的东西,整合到ISE工程中,给点思路,谢谢各位大神!

2012-07-13 20:40:36

本帖最后由 tony欧 于 2016-6-3 13:36 编辑

我用ISE编写的工程,如果涉及ROM IP核,第一次仿真时是完全好使的,输出端能输出波形。但是当我关电脑,重启再次打开这个工程时,仿真输出端就变成了ZZZZZ,请问这个是什么原因啊。。很急很急。。

2016-06-03 13:17:15

ISE中自带的乘法器IP核如何设置延时2个时钟周期?为什么我生成的时候没有latency这个选项,生成后的xco文件中貌似也没有延时,但是生成的vhd文件中却有这么一句“c_latency =>

2015-03-28 12:16:31

创建项目,然后create block,然后将ad7616核添加之IP核仓库并添加到design中后,开始validate design的时候出现了IP核被lock的问题(错误截图见附件),一直没法解决,各位大神帮帮忙!

2018-07-31 09:47:33

Vivado的FFT IP核生成的数据。 2 Matlab产生测试数据,绘制cos时域和频域波形使用projectzstar_ex67matlab文件夹下的Matlab源码fft_1line.m,运行产生1组

2020-01-07 09:33:53

没用过ISE,不知道生成的IP核文件夹中 ,哪些是需要添加到modelsim中用于仿真的文件 。拿ram举例,仿真库文件还应该添加哪些内容。希望大神们指导下 多谢

2018-12-18 17:58:32

如题,调用altera公司的FFT IP核,用的是13.1版本,将modulsim仿真的结果输入到matlab画出频谱图,功能仿真结果没有问题,但门级仿真中除了原频率信息外,出现了很多不存在的频率

2018-08-28 20:43:56

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

FPGA设计开发软件ISE使用技巧

本章目标熟悉 ISE 软件的安装与启动掌握 ISE 下FPGA的设计流程掌握 ISE 下创建工程的方式掌握 ISE 下如何编译和仿真掌

2010-02-09 09:32:29 121

121 本文讨论FPGA的ROM初始化问题,详细介绍mit文件的创建与使用。利用FPGA实现的ROM只能认为器件处于用户状态时具备ROM功能。使用时不必要刻意划分,而ROM单元的初始化则是设计人员必须面

2012-02-08 14:24:48 5265

5265

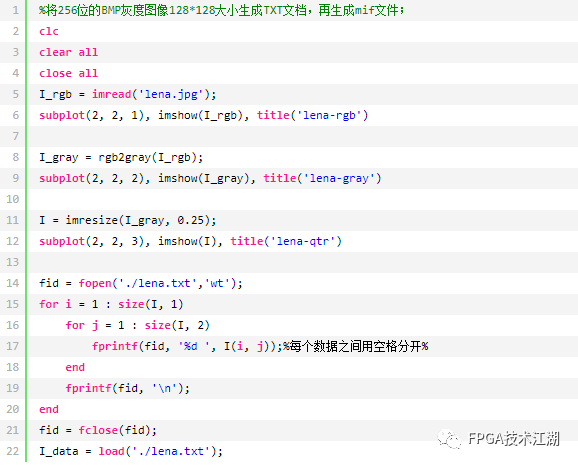

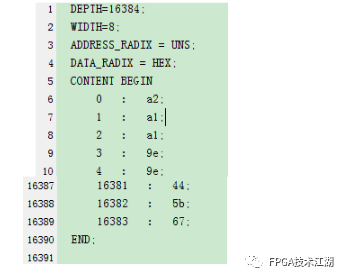

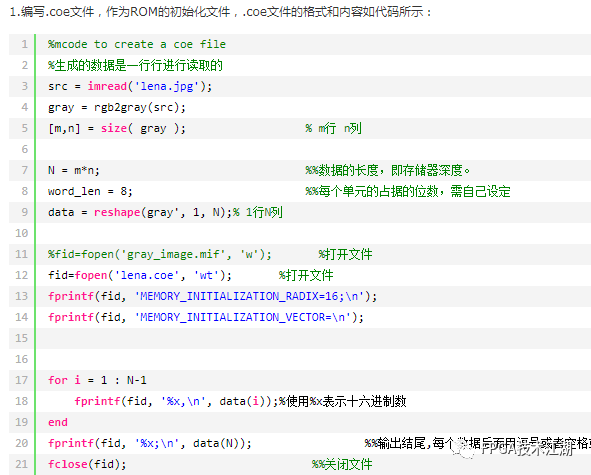

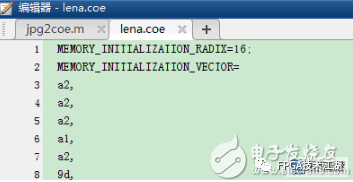

大家好,又到了每日学习的时间了,今天我们来聊一聊使用matlab和ISE 创建并仿真ROM IP核。本人想使用简单的中值滤波进行verilog相关算法的硬件实现,由于HDL设计软件不能直接处理图像

2018-10-25 20:20:35 3525

3525

大家好,又到了每日学习的时间了,今天我们来聊一聊使用matlab和ISE 创建并仿真ROM IP核。本人想使用简单的中值滤波进行verilog相关算法的硬件实现,由于HDL设计软件不能直接处理图像

2018-10-25 20:20:35 4870

4870

电子发烧友App

电子发烧友App

评论