本款带LDO架构的15 W无线充电接收器参考平台采用我们MWPR1516接收控制器IC,能够管理和执行实施无线充电接收器解决方案所需的全部功能。该解决方案经过高度优化,采用内部LDO控制器,能够以

2018-06-25 17:42:44

将LVDS信号传输给液晶面板。液晶面板的LVDS接收器再对信号做转换处理并显示。

另外需要给液晶面板提供液晶的背光,背光电路一般放在驱动板,主控通过PWM信号对面板背光进行调节。若液晶面板带触摸功能

2023-06-05 17:31:08

)。从这些产品的数据表中我可以看出,对于大多数上述FPGA来说,这应该是可行的。然而,该设计可以使用比标准1.25V共模低的共模电压。这可能是600mV的共模电压。当共模电压从标称值1.25V降低时,FPGA上LVDS接收器的速度是否会降低?

2020-06-16 08:44:15

同步LVDS时钟对。接收方接收到该串行LVDS数据,对其进行反序列化,并将其对齐到原始单词边界,生成7个并行LVTTL数据位。7:1发送器将7个LVTTL并行数据位串行化为一个LVDS数据位,并将

2019-12-11 09:51:59

的目的是为点对点拓扑中的驱动器和接收器提供通用电气层规范。点对点拓扑是一种半双工链路,包含支持差分端接的单个驱动器及接收器。下图 1 是一个点对点配置:图 1:点对点下一种架构是多支路拓扑。LVDS

2022-11-22 07:43:47

管脚悬空,所有未使用的LVDS和TTL输出管脚悬空,将未使用的TTL发送/驱动器输入和控制/使能管脚接电源或地。2.6 媒质(电缆和连接器)选择2.7 在噪声环境中提高可靠性设计LVDS 接收器在内部

2011-02-23 09:55:17

那位老师可以帮我开发一个调频调幅同步接收器,有意者加微信***有报酬最少5000人民币。

2022-11-16 14:23:46

接收器子系统的电路是怎样组成的?接收器子系统有哪几个主要误差源?

2021-05-21 06:38:39

接收器技术的最新发展:接收器百年创新史选编第2部分:接收器架构

2021-01-21 07:17:17

接收器百年创新史选编

2021-01-26 07:27:05

您好:

我准备用FPGA来对接AD9122,FPGA发送LVDS数据,DAC接收。

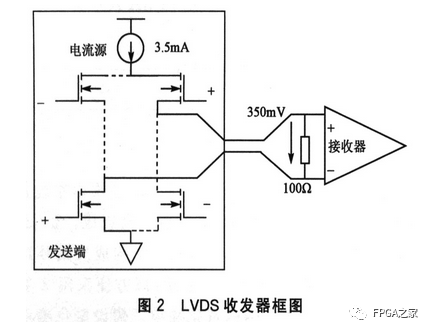

如果FPGA是LVDS接收的话,FPGA可以使能内部的差分电阻,就是在P-N之间使能了一个100欧姆的电阻

2023-12-21 08:30:31

在使用HDMI/DVI 接收器时,你有遇到过以下问题吗? HDMI Receiver 产品中的 EDID 必须要使用吗?将 将 HDMI Receiver 的输出连接到显示设备后 ,一直是蓝屏状态

2017-06-25 14:05:51

、Adobe RGB、Adobe YCC 601和xvYCC扩展颜色范围兼容CEC 1.4·HDMI接收器最小化传输差分信号(TMDS)时钟频率:165 MHz(最大值)24位输出像素总线·音频支持S/PDIF

2015-09-15 14:26:05

AS3933是15–150kHz频率范围、3通道低频唤醒接收器,且具备自动天线调谐功能奥地利微电子推出业内性能最出色的15–150kHz频率范围、3通道低频唤醒接收器,且具备自动天线调谐功能。 3

2018-11-26 09:59:05

`AS3933是15–150kHz频率范围、3通道低频唤醒接收器,且具备自动天线调谐功能奥地利微电子推出业内性能最出色的15–150kHz频率范围、3通道低频唤醒接收器,且具备自动天线调谐功能。3

2018-12-21 15:39:15

3)参考600Mhz时钟通过LVDS发送数据FPGA1)接收单行lvds数据2)我使用“Camera Link接收器”和“相位检测器”和“重新定时”选项。3)我在FPGA(PLL)上生成600MHz

2019-07-17 06:40:58

特征 ●单电源+3.3V电源 ●B/LVDS接收器输入接受LVPECL信号 ●三态输出 ●信号丢失(LOS)引脚检测非驱动总线 ●接收器输入阈值《±100 mV ●1.4ns的快速

2020-07-14 14:48:54

嗨,我集成了dp v1.1接收器IP,项目屏幕截图如下。和display_port_sink_policy_maker没关系。我使用SDK创建比特流,然后使用download.bit对FPGA进行

2020-07-19 07:44:20

1 概述GM8284DD 型 28 位 LVDS 图像收器主要用于视频/图像传输中的接收部分,实现的功 能是将高速串行 LVDS 信号解码为并行 TTL 数据,完成数据的解码功能。该器件可将 4

2020-12-03 10:02:18

过程中产生比特错误。在下图 3 中,我举了两个实例,用以说明如何在 CML 驱动器、LVPECL 驱动器和 LVDS 接收器之间实施 AC 耦合。图3:不同接口的互连连接任意两个不同接口时可使用这种相同

2018-09-13 14:28:38

MS90C104 ——+3.3V 175MHz 的 30bit 平板显示器(FPD)LVDS 信号接收器功能概述 MS90C104 芯片能够将 5 通道的低压差分信号(LVDS)转换成 35bit

2021-01-10 17:48:07

:BGA键都很好。经过这些步骤后,看起来内部的Virtex LVDS接收器在内部出现问题。 A / D和Virtex电源均来自相同的3.3V电源,因此我不认为这是电源竞争问题,特别是因为A / D输出

2020-05-28 13:32:49

类型:接收器 协议类别:LVDS 驱动器/接收器数:0/4 数据速率:400Mbps

2023-03-28 18:28:02

你好,我支持现有的设计,其中有一个摄像机链接接收器(3个LVDS数据线和1个LVDS帧时钟)。这似乎与Xapp1064的案例1相匹配。数据线以315Mbps运行。输入时钟没有放在CLK引脚上,因此

2019-02-14 07:23:17

大家好这是我第一次发布东西,我正在设计一个lvds发射器,我需要知道virtex-6 FPGA中lvds接收器的输入电容能够测试我的发射器吗?我查看了数据手册,发现输入芯片电容为8pF,这与virtex-6中lvds接收器的输入电容相同。提前致谢易卜拉欣·艾哈迈德

2020-06-11 06:07:12

AS3933是15–150kHz频率范围、3通道低频唤醒接收器,且具备自动天线调谐功能奥地利微电子推出业内性能最出色的15–150kHz频率范围、3通道低频唤醒接收器,且具备自动天线调谐功能。3通道

2018-05-12 15:03:49

嗨,每个人,我都使用V4 FPGA从CMOS接收LVDS数据。同时,CMOS输出一个LVDS时钟资源'dck'作为同步时钟。数据在上升沿和下降沿传输,如下图所示。 我清楚地知道在verilog

2020-04-20 10:21:22

关于GPS接收器测试的分析

2021-05-08 07:05:37

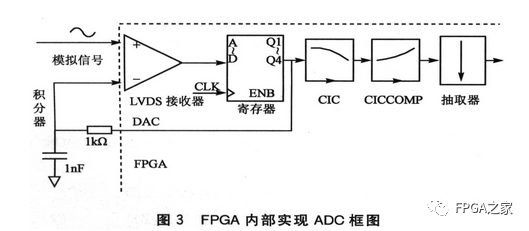

,所以500M采样率工作时,LVDS数据输出的随路时钟是250Mhz,一般的芯片没有可以的达到该速率的接收器,所以必须使用FPGA来作为该芯片的数据接收与后续的信号处理。 明德扬AD9684 ADC接口

2019-12-06 15:33:22

哪位大神给个基于FPGA的IR接收器VHDL语言的程序

2017-05-20 20:43:57

你好!我正在使用斯巴达6 lx100与斯巴达6 lx9进行通信,它位于不同的主板上。它们之间的连接是点对点的,通过30厘米电缆和100Mhz LVDS信号。我应该使用外部驱动器和接收器还是fpga

2019-06-24 15:44:23

于智能手机应用。 本文将介绍基于FPGA的无线充电器接收器系统的解决方案。无线充电器接收器严格遵循最新的WPC Qi标准。接收器系统包含一个模拟模块和一个FPGA模块。模拟模块由分立式组件组成,包括全桥

2018-09-27 15:35:58

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

22.4Gbps(Kintex-7).2. 1对LVDS接收时钟+16对LVDS接收数据.本人可以提供FPGA源代码.同时还可以在Xilinx评估板ML555/ML605/KC705上演示验证.如有高速LVDS数据传输相关方面的技术合作,可联系我。联系方式:neteasy163z@163.com

2014-03-01 18:47:47

基站接收器集成化的进展

2019-08-27 09:05:39

如何使用MLD优化MIMO接收器的性能?

2021-05-24 06:16:55

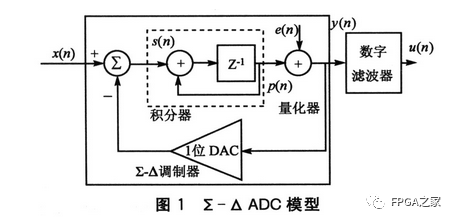

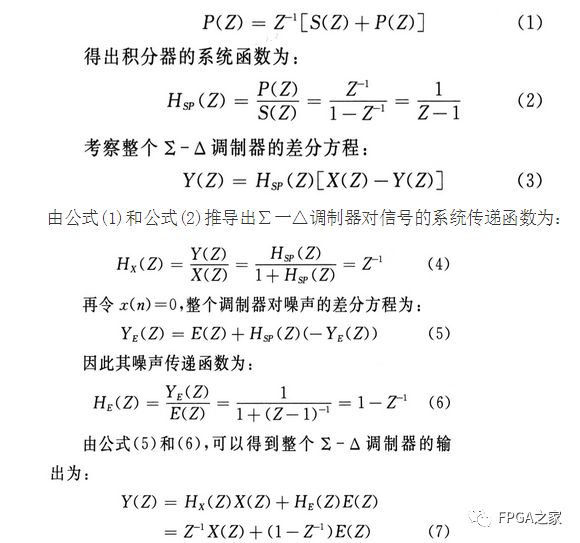

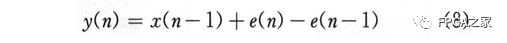

∑一△ADC原理是什么?LVDS收发器标准及其原理是什么?如何利用LVDS接收器去实现ADC?

2021-06-03 06:23:35

Spartan-3 FPGA系列如何仅通过在接收器数据通路中加入一个倒相器即可避免大量使用过孔?如何利用Spartan-3 FPGA进行LVDS信号倒相设计?

2021-05-06 07:30:25

在串行数据传输的过程中,如何在FPGA中利用低频源同步时钟实现LVDS接收字对齐呢?

2021-04-08 06:39:42

本文介绍如何确定接收器增益,以及接收器增益设置太高时对接收SNR的负面影响。文章也讨论如何正确优化数字波束成形器、滤波器、检波器的动态范围以及压缩信号映射。实现上述优化后,系统将最大程度地发挥高SNR接收器的优势,大幅提高诊断性能。

2021-04-19 10:00:39

`` 随着工业无线遥控器的广泛使用,需普及更多的遥控器专业知识给大家,方便大家进行安全的生产和生产更顺畅;今天主要给大家讲解接收器天线及隔离器的安装注意事项,因为在进行上门售后的过程中,技术工程师

2021-04-17 10:28:15

`求大神讲解下他的构成,我要制作的话,需要什么?现在知道他是个无线接收器,接收距离3000`

2013-04-05 19:07:43

现在的无线充电器都是通过线圈来发送的,需要配合无线接收器才能完成充电过程。大部分充电接收器在充电过程中会出现过热的情况,不知道大家怎么看?

2014-08-22 17:59:27

嗨,是否有Xilinx提供的视频LVDS serdes发送器/接收器IP内核?如果是这样请分享详细信息。

2020-05-22 14:34:10

目前使用的的时xilinx kintex7 核心板,使用Bank14作为LVDS输入和输出,Bank14供电为2.5V,并联100欧电阻,测量出来有输出也有输入,但是FPGA读不到数据,为什么?

2023-09-14 10:19:21

本人想做一个直接接入到FPGA或者DSP等基带处理系统的RF接收器,频段是2.4Ghz的,希望能够选择一到两个芯片完成从天线到LNA、下变频、IQ调制的2.4Ghz RF接收器子板,然后通过ADC

2013-10-11 20:26:06

你好,我目前正在设计一个LVDS接收器和DAC ASIC。DAC是12位。我需要使用来自FPGA / Eval板的LVDS信号进行测试。任何人都可以推荐我可以用来测试我的ASIC的评估板或FPGA吗?谢谢。问候,尼基尔

2019-09-19 12:27:09

DIY红外遥控接收器

2012-08-15 22:36:16

您好: 我准备用FPGA来对接AD9122,FPGA发送LVDS数据,DAC接收。 如果FPGA是LVDS接收的话,FPGA可以使能内部的差分电阻,就是在P-N之间使能了一个100欧姆的电阻, 现在

2018-10-29 10:34:15

大家好。我已经模拟了1到10个与XAPP1017相关的DDR数据,我不清楚理解反序列化lvds数据的理论谁能给我一个关于如何用XAPP1017实现1到12 DDR数据接收器的例子

2020-08-06 10:44:54

你好,我目前正在设计一个LVDS接收器和DAC ASIC。DAC是12位。我需要使用来自FPGA / Eval板的LVDS信号进行测试。任何人都可以推荐Xilinx的评估板或FPGA,我可以使用它来测试我的ASIC吗?谢谢。问候,尼基尔

2019-08-28 07:03:41

那位老师可以帮我做一款调频调幅同步无线接收器。

2022-11-16 21:25:57

转换接收器芯片LTM9004资料下载内容主要介绍了:LTM9004功能和特点LTM9004引脚功能LTM9004内部方框图LTM9004典型应用电路

2021-03-30 06:01:33

时钟信号,因为用户为UART硬件提供了必要的时序信息。实际上,有一个时钟信号,但是它不是从一个通信设备传输到另一个通信设备的;相反,接收器和发送器都具有内部时钟信号,这些时钟信号控制如何生成变化的逻辑

2020-09-18 09:00:00

时钟信号,因为用户为UART硬件提供了必要的时序信息。实际上,有一个时钟信号,但是它不是从一个通信设备传输到另一个通信设备的;相反,接收器和发送器都具有内部时钟信号,这些时钟信号控制如何生成变化的逻辑

2020-09-25 17:43:01

毕业设计:功放机遥控接收器的设计,用到了PT2314这个芯片,不懂啊,求帮忙!

2013-05-28 20:16:03

MAX9111/MAX9113单路/双路低压差分信号(LVDS)接收器专为需要超小功耗、空间和噪声的高速应用而设计。这两款器件均支持超过500Mbps的开关速率,同时采用+3.3V单电源供电,并具有

2023-07-12 16:11:19

MAX9111/MAX9113单路/双路低压差分信号(LVDS)接收器专为需要超小功耗、空间和噪声的高速应用而设计。这两款器件均支持超过500Mbps的开关速率,同时采用+3.3V单电源供电,并具有

2023-07-12 16:16:25

驱动器/接收器,驱动器/接收器原理是什么?

5V双RS232驱动器/接收器

T1780/LT1781双RS驱动器

2010-03-08 13:27:01 1818

1818 光接收器,光接收器原理和结构组成是什么?

光接收器的定义:

在光纤通信系统中,光接收

2010-03-19 17:03:21 12852

12852 光接收器件,什么是光接收器件

光接收机用于接收光缆中的光信号,再将之转换为电信号送入电缆网络。

其

2010-04-02 16:02:49 4129

4129 本文描述TI 的客户在不用 LVDS (低压差分信号传输)驱动器时,如何采用LVDS 接收器于其他驱动器配合解决一些简单的问题。

2011-07-18 15:21:36 30

30 介绍了LVDS技术的原理,对LVDS接口在高速数据传输系统中的应用做了简要的分析,着重介绍了基于FPGA的LVDS_TX模块的应用,并通过其在DAC系统中的应用实验进一步说明了LVDS接口的优点。

2012-01-11 10:46:04 99

99 低电压差分信号(LVDS)是一种高速点到点应用通信标准。多点LVDS (M-LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS均使用差分信号,通过这种双线式通信方法,接收器将根据两个互补

2013-08-22 16:09:00 93

93 低功耗数据传输领域的主流技术。它具有信号摆幅小、速度快、功耗低、抗共模噪声能力强、电磁干扰小等优点。 LVDS接口技术的原理可简单概括为:由驱动器( driver)将CMOS或TTL信号转换成LVDS差分信号,并经过互连线传输到接收器端,而接收器又将差分信

2017-11-01 15:50:08 11

11 的作用下由DVI发送器进行编码并串行化后,通过TMDS通道发送给DVI接收器;DVI接收器对其进行串/并转换、通道对齐、解码等一系列处理后发送给显示设备。

2017-11-22 14:27:02 4895

4895 电子发烧友网为你提供TI(ti)SN55LVDS32相关产品参数、数据手册,更有SN55LVDS32的引脚图、接线图、封装手册、中文资料、英文资料,SN55LVDS32真值表,SN55LVDS32管脚等资料,希望可以帮助到广大的电子工程师们。

2018-11-02 19:01:06

电子发烧友网为你提供TI(ti)SN65LVDS32相关产品参数、数据手册,更有SN65LVDS32的引脚图、接线图、封装手册、中文资料、英文资料,SN65LVDS32真值表,SN65LVDS32管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:10:12

电子发烧友网为你提供TI(ti)SN65LVDS2相关产品参数、数据手册,更有SN65LVDS2的引脚图、接线图、封装手册、中文资料、英文资料,SN65LVDS2真值表,SN65LVDS2管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:10:12

LVDS接收器可以承受至少±1V的驱动器与接收器之间的地的电压变化。由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。

2018-11-01 16:47:28 74230

74230

在电缆应用中,接收器将不总是由发送器驱动,并且接收器输入上可能存在超过20 mV的差分噪声,应考虑使用额外的故障保护电阻。

2021-05-21 06:24:00 2846

2846 ADN4668:3 V LVDS四路CMOS差分线路接收器数据表

2021-05-08 17:13:41 1

1 ADN4664:双路3 V CMOS LVDS差分线路接收器数据表

2021-05-09 17:49:57 2

2 ADN4662:单路、3 V、CMOS、LVDS差分线路接收器数据表

2021-05-25 19:48:08 5

5 ADV7782:带LVDS、HDCP和MIPI支持的APIX2接收器数据表

2021-05-27 18:32:53 7

7 VP386 数据表 8/28 位 LVDS 视频接收器

2023-04-27 19:34:18 0

0 红外遥控接收器模块,非常简单,也是由GND,VCC和数据三个引脚组成,通过杜邦线可以直接连接在FPGA的IO口上,产品细节如下

2023-10-15 10:53:49 415

415

简介:本文将介绍基于FPGA的无线充电器接收器系统的解决方案。无线充电器接收器严格遵循最新的WPC Qi标准。接收器系统包含一个模拟模块和一个FPGA模块。模拟模块由分立式组件组成,包括全桥整流器

2023-11-09 15:26:30 5

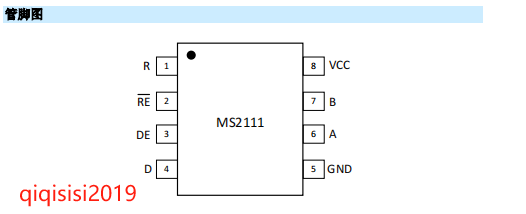

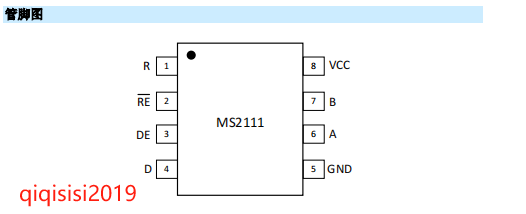

5 产品简述 MS2111 是多点低压差分(M-LVDS)线路驱动器和接收器。经过 优化,可运行在高达 200Mbps 的信号速率下。所有部件均符合 M LVDS 标准 TIA / EIA-899

2024-01-25 11:20:58 263

263

电子发烧友App

电子发烧友App

评论