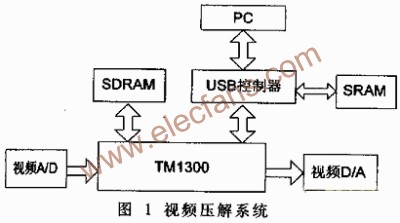

本文针对高速数据传输需求,根据USB2.0的协议规范,利用VHDL语言实现符合该协议的功能控制器,在视频压解系统中使数据在PC与外设之间高速传输。

2010-10-28 15:44:03 1170

1170

广东高云半导体科技宣布发布其USB 2.0接口解决方案,此方案能够使FPGA设计人员轻松的集成USB 2.0功能,无需外挂PHY芯片。

2021-05-17 15:28:34 3589

3589 方式完全和ASIC相同。这并不奇怪,因为它们本质上是相同的东西。唯一的区别是,ASSP是更通用的设备,适用于多个系统设计工作室。例如,独立的USB接口芯片可以归类为ASSP。 SoC——系统级芯片

2014-07-24 11:18:05

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到 I/O 模块。FPGA 的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间

2020-09-25 11:34:41

模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终

2017-09-02 22:24:53

流水方式对复数数据实现了加窗、FFT、求模平方三种运算。整个设计采用流水与并行方式尽量避免瓶颈的出现,提高系统时钟频率,达到高速处理。实验表明此处理器既有专用ASIC电路的快速性,又有DSP器件的灵活性的特点,适合用于高速数字信号处理。

2012-08-12 11:49:01

的EZ-USB FX2系列智能USB接口芯片。其作用是将主机所发送的命令序列经USB2.0端口输出,实现对数据采集系统的控制;同时把A/D转换器采集的数据以高速的数据序列形式发送到主机。其中,USB2.0端口

2020-01-07 07:00:00

FPGA能否继续在SoC类应用中替代ASIC?CoreConsole工具是什么,有什么功能?

2021-04-08 06:23:39

近期在处理一个USB2.0通信的问题,采用FPGA主控,FT245为USB芯片,Verilog编程控制。FT245有RD和WR两个读写控制端,RXF和TXE两个USB芯片工作状态反馈端。数据读操作

2019-07-31 14:07:59

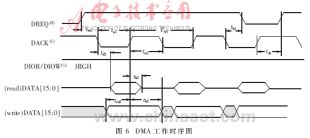

基于数码相机电路系统,USB 为该系统与主机的接口电路。在测试USB 上传数据给主机时,主机先通过EPP 将数据下载到SDRAM中,然后缓存控制器通过DMA总线将数据从SDRAM中读出来,传送给USB 协议

2019-04-12 07:00:12

芯片与FPGA(现场可编程门阵列)芯片接口的Verilog HDL(硬件描述语言)实现。本系统可扩展,完全可用于其他高速数据采集系统中。 1 系统构成 本系统主要是由FPGA和USB2.0控制器

2019-05-10 07:00:03

损坏。 通用串行总线(USB)高速数据应用也十分普遍,用户在热插拨任何USB外设时可能会导致ESD事件。此外,在离导电表面几英寸的地方也可能发生空气放电,可能损坏USB接口及芯片。因此,设计人员必须为

2013-12-27 16:21:39

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

的时间内完成高速的USB2.0数据传输功能的开发。功能特点:1、FPGA程序和VC应用程序开源设计(但不提供CY7C68013固件源码),用户可以根据自己的需要修改源码;2、独家提供稳定高效的SRAM

2018-10-15 10:18:50

的时间内完成高速的USB2.0数据传输功能的开发。功能特点:1、FPGA程序和VC应用程序开源设计(但不提供CY7C68013固件源码),用户可以根据自己的需要修改源码;2、独家提供稳定高效的SRAM

2018-10-18 14:51:28

的时间内完成高速的USB2.0数据传输功能的开发。功能特点:1、FPGA程序和VC应用程序开源设计(但不提供CY7C68013固件源码),用户可以根据自己的需要修改源码;2、独家提供稳定高效的SRAM

2019-01-09 14:31:57

我已经完成了我的fpga实现,如何转向asic实现?我们正在使用ieee_proposed。这项技术具体吗?

2020-03-19 09:28:49

的协议物理层,FX2把所有的功能集成在一个芯片上。 二、Slave FIFO传输2.1概述当有一个与FX2芯片相连的外部逻辑只需要利用FX2做为一个USB 2.0接口而实现与主机的高速通讯,而它本身

2014-03-24 10:06:49

。HAPS-51采用FPGA阵列Xilinx Virtex-5 LX330和板上存储器,加快了ASIC验证的速度。先前的HAPS系统在存储器存取方面采用子板,而最新的HAPS-51则采用位于板上并靠近

2018-11-20 15:49:49

定制ASIC电路的中试样片。 3)FPGA内部有丰富的触发器和I/O引脚。 4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 5)FPGA采用高速CHMOS工艺

2012-02-27 17:46:03

背景:FPGA高速产生数据,通过USB2.0芯片发送给labview(Windows运行)接收。受限于labview程序读取u***数据的速度,最快只能接收约100kbit/s的数据,而u

2021-06-25 15:58:25

通用串行总线则具有安装方便、高带宽、易扩展等优点,其中USB2.0标准具有480Mbps的最高数据传输率,这使USB成为本系统所选接口的主要类型。控制方面,传统数据采集通常使用单片机或DSP作CPU来

2019-07-05 08:23:08

描述该参考设计提供有关如何在空间限制是首要考虑因素时为工业传感器应用中的 FPGA、ASIC 或 MCU 供电的示例。6V 至 60V 的宽输入电压范围和超小且非常高效的直流/直流转换器的使用使该

2018-10-22 10:17:12

在 FPGA、GPU 或 ASIC 控制的系统板上,仅有为数不多的几种电源管理相关的设计挑战,但是由于需要反复调试,所以这类挑战可能使系统的推出时间严重滞后。

2019-10-09 06:21:11

在 FPGA、GPU 或 ASIC 控制的系统板上,仅有为数不多的几种电源管理相关的设计挑战,但是由于需要反复调试,所以这类挑战可能使系统的推出时间严重滞后。

2019-09-30 06:59:24

FPGA的DNN实现专注在矩阵乘法(Matrix product)的实现上,而放弃了在CNN/DNN中复杂data flow的支持。同样地,这个问题在以RAM compiler为基础的ASIC实现上毫无

2023-03-28 11:14:04

提供的门电路规模足够大,通过编程,就能够实现任意ASIC的逻辑功能。

FPGA开发套件,中间那个是FPGA芯片

我们再看看FPGA的发展历程。

FPGA是在PAL(可编程

2024-01-23 19:08:55

要求的PCB板对产品的性能、可靠性起着极为重要的作用,并能带来明显的经济效益。USB2.0接口是目前许多高速数据传输设备的首选接口,实践表明:在高速USB主、从设备的研发过程中,正确设计PCB板能

2015-02-11 14:44:36

1 引言高速数据传输系统在通信系统、测试仪器等电子系统中有着广泛应用,人们对数据传输的处理速度、可靠性及实时性的要求越来越高。高速稳定可靠的数据传输技术,在高速数据采集系统中扮演着重要的角色,随着

2018-08-09 14:18:42

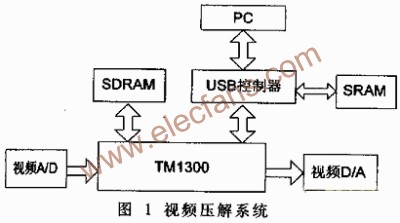

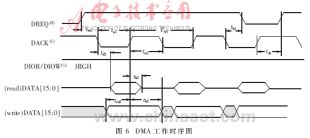

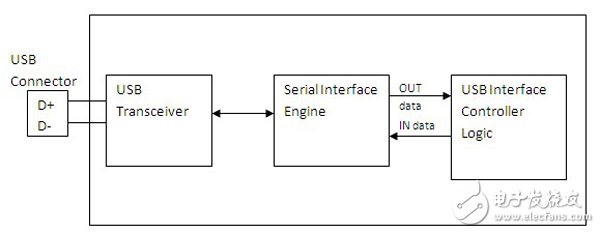

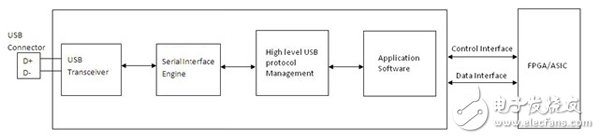

/A。1 控制器结构原理USB2.0控制器结构框图如图2所示。控制器主要由两个部分组成,其一为与外设的接口,另一个是内部协议层逻辑PL(Protocol Layer)。内部存储器仲裁器实现对内部DMA

2021-06-29 07:30:00

基于FPGA的USB2.0设计

2017-12-07 11:27:40

事务中实时更新控制/状态寄存器CSR。SIE还能通过CSR中的中断向量请求设备总线的控制支持。3 系统仿真与实现设计中包含了UTM,SIE,并根据协议写出了含有设备描述符的ROM。这样IP具有USB接口

2018-11-21 11:30:06

的输入输出接口设计就显得尤为重要。1 高速采集系统介绍 数据采集系统原理框图如图1所示,输入的中频信号经A/D采样电路采样后,转换成LVDS信号送入FPGA中,或通过FPGA的端口RocketIO从高速接口

2018-12-18 10:22:18

目前,在数据采集系统的硬件设计方案中,有采用通用单片机和USB相结合的方案,也有采用DSP和USB相结合的方案,前者虽然硬件成本低,但是时钟频率较低,难以满足数据采集系统对速度要求;后者虽然可以实现

2019-09-05 07:22:57

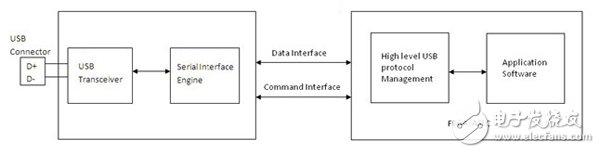

。 USB从接口CY7C68001模块 CY7C68001集成有USB2.0收发器(物理层)、USB2.0串行接口引擎SIE(链路层)、4kB的FIFO和电压调节器、锁相环,支持高速(480Mb/s)或

2019-05-07 09:40:04

速度和精度。

系统总体设计方案

本文提出了一种基于LABVIEW的USB接口高速数据采集系统的设计,充分利用DSP丰富的片上外设以及高性能的数字信号处理能力,将采集的数据经DSP处理后通过高速USB

2018-12-26 07:00:05

引 言在高速的数据采集或传输中,目前使用较多的都是采用USB 2.0接口控制器和FPGA或DSP实现的,本设计在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作为

2021-06-24 07:00:00

信息并控制系统将采集处理后的数据上传至PC显示。单片机与PC的接口利用符合USB2.0规范的接口芯片CP2102实现。首先,PC向FPGA发送触发字信息、数据采集控制信息和开启数据采集信号;单片机发送

2015-01-14 14:56:07

协议外,还负责解释设备子类协议,并实现对具体外部应用系统(设备元件)的操作。 从硬件结构分析,基于增强型8051MCU核的 USB2.0设备接口芯片(IP核)应包括以下几个模块: (1)USB2.0

2018-12-03 15:24:04

多FPGA系统中自定义高速串行数据接口设计为方便多FPGA系统中主从FPGA之间的命令与数据传输,节省连接的引脚数量,设计了一种基于FPGA的自定义高速串行数据传输模块。对主从串行模块进行了详尽

2012-08-11 11:49:57

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM中没有单独的Pariaty写使能位。 如何实现ASIC RAM奇偶校验写入启用ino FPGA RAM。谢谢娜文G K.

2020-04-24 09:37:05

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

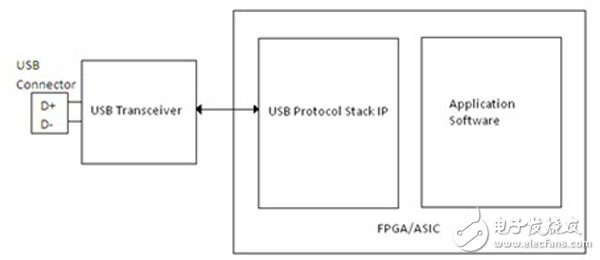

网络连接到USB主机。本文将探讨其设计方法,可以在FPGA或ASIC系统中实现高效高速USB 2.0接口。图1 基于USB的分布式***采集系统 在介绍整合通用串行总线接口到FPGA或ASIC系统的各种

2012-11-22 16:11:20

通用串行总线已经很普遍了,这是由于其使用简单,随插即用,并具有鲁棒性的优点。USB已经找到了进入曾经使用串口、并口作为其host接口的计算机外设的方式,需要接口到host计算机的产品现在也把USB

2019-10-11 07:51:32

行演示在没有等效的ASIC可用,或者需要重新配置硬件的情况下,使用FPGA进行中小批量和高价值商业应用与有线或无线通信等应用中为确保互操作性所需的实时处理不同,图像处理NN的FPGA实现通常不需要满足

2023-02-08 15:26:46

之间进行数据传输适用于高速 USB 2.0 布局的最佳实践布局设计指南完整的子系统参考,具有原理图、BOM、设计文件和测试数据,在专为测试和验证而开发的完全组装的板上实施。`

2015-04-02 15:54:09

怎么实现USB2.0 SIE的ASIC设计?

2021-05-28 06:36:31

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

怎么实现基于USB2.0的高速同步数据采集系统的设计?

2021-05-21 06:47:15

求基于DSP的外扩符合 USB2.0 标准的高速 SLAVE端接口CY7C68013A,支持USB2.0高速和全速标准 相关资料及源码?

2014-02-25 11:58:06

与LVDS接口转换,使在只有USB接的情况下便可实现双视频显示的连接,进一步扩展两种接口的使用范围,从而在一定程度上解决主板插槽与端口日益匮乏的问题。 2 系统概述该系统设计主要由稳压电路,USB接口

2018-11-22 11:24:30

如何去设计一个基于FPGA和USB 2.0的高速CCD声光信号采集系统?

2021-04-29 06:22:30

,USB电缆包含4根电线:Vbus,D+,D-和GND。数据以480M高速信号在D+和D-信号线上差分传输,而收发器在USB接口控制芯片上,不需要外部电路。 USB接口部分是本系统最为重要的通信部分。USB

2019-06-04 05:00:19

。可以通过在DSP的Linkport总线接口上增加FPGA实现的适配电路,扩展USB 2.0接口,实现上述应用需求。下文将介绍具体的实现方案。1 系统总体方案系统实现的总体方案如图1所示。在本方案中

2019-05-31 05:00:04

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-22 07:00:07

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-26 07:00:12

USB接口演进历史USB3.0系统概述USB3.0超高速度链路和 USB2.0链路的静电防护布局设计提议面向USB3.0的现代化静电防护策略

2021-01-06 06:20:43

在过去10年间,全世界的设计人员都讨论过使用ASIC或者FPGA来实现数字电子设计的好处。通常这些讨论将完全定制IC的性能优势和低功耗与FPGA的灵活性和低NRE成本进行比较。设计队伍应当在ASIC

2019-07-15 07:00:39

汉源高科USB2.0光端机由发射机和接收机组成,通过单模或多模光纤把主机的USB接口(USB2.0)延长到远端并扩展为4个USB口。最大传输距离10KM(单模光纤)。支持USB 1.1和2.0类型

2022-06-21 11:02:13

High volume USB 2.0 devices will be designed using ASIC technology with embedded USB 2.0

2009-04-06 10:42:10 30

30 通用串行总线USB是一种新型的计算机通信标准,本文利用USB2.0 总线接口高速高带宽的优点,介绍了一种能够实现高速数据传输的USB2.0接口系统的设计,为雷达信号从外部向主

2009-04-11 17:42:13 25

25 介绍一个基于USB2.0 接口和DSP的高速数据采集处理系统的工作原理、设计及实现。该高速数据采集处理系统采用TI 公司的TMS320C6000 数字信号处理器和Cypress 公司的USB2.0 接口芯片,可以

2009-05-16 14:48:53 21

21 基于FPGA的USB2.0高速、低成本的虚拟逻辑分析仪的设计原理与实现方法:本文介绍了一种基于FPGA的USB2.0高速、低成本的虚拟逻辑分析仪的设计原理与实现方法。重点介绍了逻辑分析仪

2009-06-22 19:11:17 57

57 本文介绍了USB 的优缺点,较详细地论述了笔者开发的一块基于USB2.0 接口的虚拟逻辑分析仪卡,包括它的USB 接口芯片、工作原理和软硬件实现。USB 是英文Universal Serial Bus 的缩

2009-08-11 09:52:10 17

17 提出了一种基于USB2.0 接口的高速光栅自动检测系统的软硬件设计方法。利用CCD作为数据采集元件,结合国家半导体公司的扫描仪控制芯LM9812 和Cypress 公司的USB 接口控制芯片CY7C6801

2009-09-01 08:56:45 12

12 针对工业现场的复杂情况,设计出一种数据传输接口转换方法,采用DSP、FPGA与USB2.0,结合RS-422接口,实现数据的远距离采集。本系统结合了USB2.0的可即插即用的优点,以及RS-422/RS-485接口可

2010-02-24 11:33:48 31

31 本文提出一种基于SOPC(可编程片上系统)和USB2.0的高速数据采集系统设计方案,并利用Labview实现虚拟仪器的设计;介绍此方案中用到的USB接口芯片CY7c68013的工作原理,利用FPGA实现的SOP

2010-07-17 17:10:35 22

22 针对油气井视频检测高速图像采集传输的要求,设计一种基于通用串行总线USB2.0协议的高速图像采集系统。该系统设计是以TMS320DM6437型DSP为系统核心,并通过USB接口器件与PC主机相连

2010-12-30 15:50:57 44

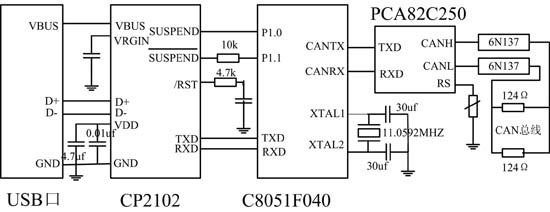

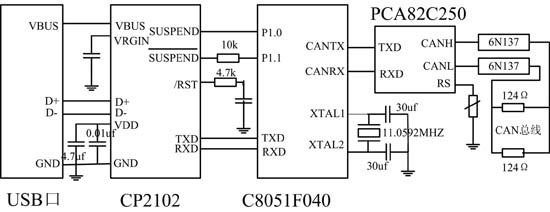

44 基于CP2102高速USB2.0-CAN适配卡的设计

基于桥接芯片CP2102,设计了USB2.0-CAN的适配卡。系统采用USB和CAN接收中断、通信同步的握手协议等方式,解决了USB的高速率和CAN的低

2009-04-22 18:34:07 3177

3177

基于USB2.0与FPGA技术的高速数据采集系统的设计

基于USB2.0与FPGA技术的高速数据采集系统的设计

近年来笔记本电脑迅速普及和更新,其中大部分已经

2009-04-22 19:56:15 1347

1347

MIPS科技实现USB 2.0高速物理层IP

MIPS科技(MIPS Technologies, Inc)宣布,该公司的40nm USB 2.0高速物理层(PHY)IP已获得USB-IF 认证,

2009-05-14 12:10:25 793

793 摘要:介绍了一种用VHDL设计USB2.0功能控制器的方法,详术了其原理和设计思想,并在FPGA上予以实现。

关键词:USB VHDL FPGA

在视

2009-06-20 13:26:46 1474

1474

高速USB数据采集系统的设计

在图像处理、瞬态信号测量等一些高速、高精度的应用中,需要进行高速数据采集。USB 2.0接口以其高速率等优点渐有取

2009-09-26 18:05:46 677

677

基于加密USB2.0接口芯片的设计及验证

0 引言

USB 总线因其具有高速度、即插即用、功耗低等特点,深受广大用户的青睐。但USB 规范本身并未考虑数据传输时

2009-12-10 16:55:58 850

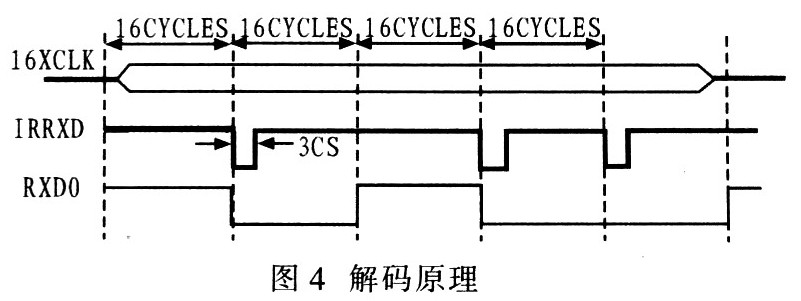

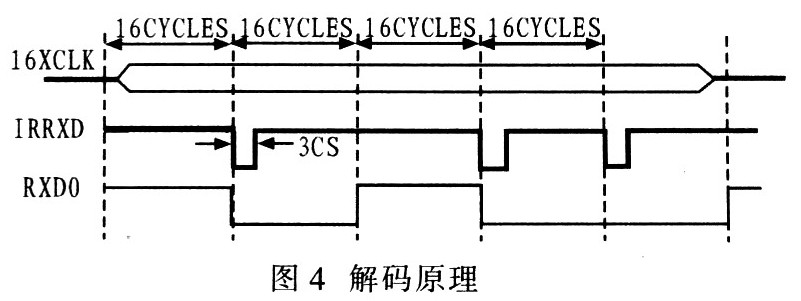

850 基于USB2.0的红外数据传输系统的设计与实现

摘要:针对有线传输的缺点或不足,为避免经常插拔接口造成测试仪器损坏,设计基于USB2.0的红外数据传输系统。详细论

2010-03-13 09:56:50 1363

1363

IR-UWB通信系统高速USB接口的设计与实现

摘要: 采用高速USB接口连接计算机终端与UWB通信系统基带模块,设计并实现了USB接口电路,控制UWB通信系统基带模块与USB接口设

2010-03-13 11:32:33 1984

1984

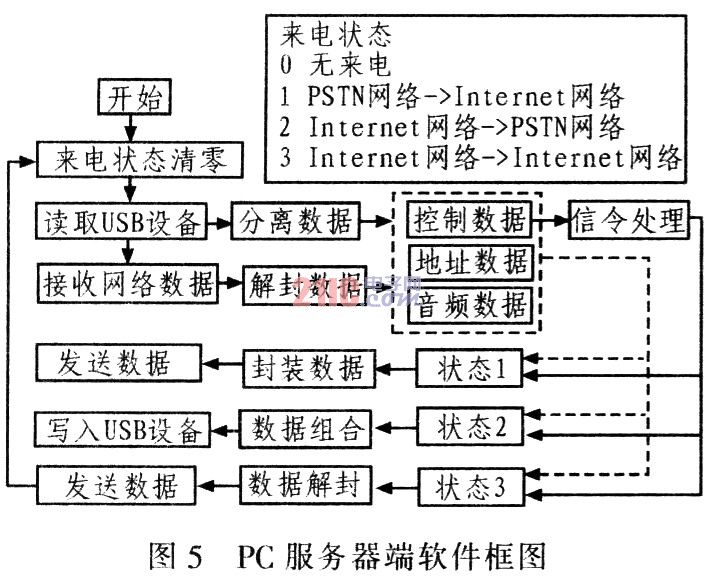

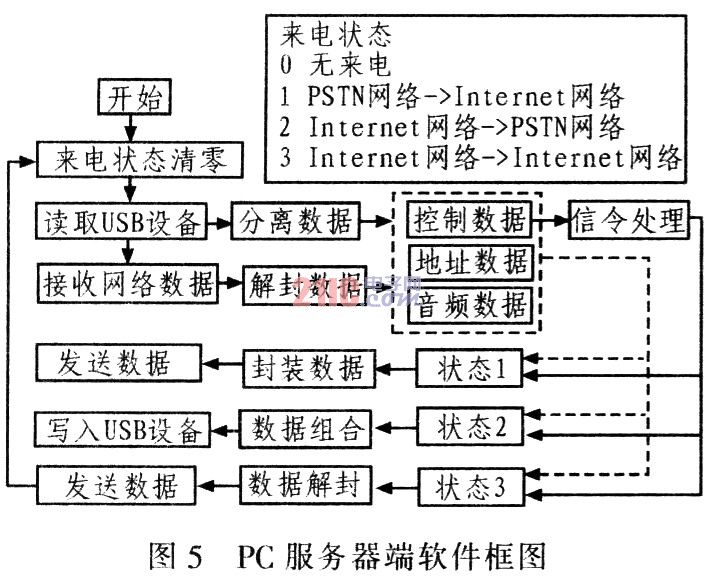

FPGA的嵌入式系统USB接口设计

摘要:设计基于FPGA的IP-BX电话应用系统,用于传统的电话网络(PSTN)与PC机之间的接口连接。USB2.0接口器件EZ-USB FX2 CY7C68013A-56工作在slave FIFO

2010-04-03 10:52:39 1664

1664

摘要:论述了基于DSP和USB2.0接口的高速便携式数据采集处理系统的设计,详细地阐述了虚拟仪器系统的实现原理和方法。利用ADS8364模数转换芯片可实现对6通道信号的同步采样,分辨率达16位。利用EZUSBFX2作为USB2.0接口芯片,实现了主机和该系统的高速数据通讯

2011-03-01 01:13:49 132

132 介绍了一种高速实时数据采集系统的设计。该系统以FPGA作为逻辑控制的核心,以USB2.0作为与上位机数据传输的接口,能同时支持单端16路和差分8路模拟信号输入,最大采样率为200 kHz,

2011-09-29 17:16:36 62

62 白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 基于FPGA的高速USB2.0数据采集系统主控电路设计

2016-01-04 15:31:55 0

0 基于FPGA的高速数据采集系统接口设计.

2016-05-10 17:06:40 27

27 基于FPGA的高速DSP与液晶模块接口的实现

2017-10-19 13:46:23 3

3 高速USB2.0设备的PCB板设计。

2018-01-25 17:27:56 0

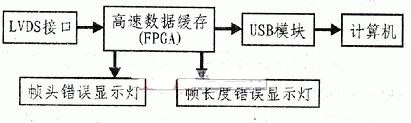

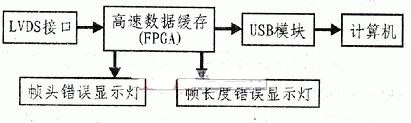

0 整个系统主要由低电压差分信号(LVDS)接口电路、基于FPGA的高速数据缓存、判断数据错误模块、USB传输模块和计算机组成,其系统结构框图如图1所示。当低电压差分信号接口电路把接收的雷达数据形成分机数据送入FPGA缓存后,该信息便可通过USB接口进行传输、记录并在计算机上显示。

2019-05-16 08:14:00 3637

3637

、高增益、实时并行处理等特点外,还具有容量大,体积小,功耗低等优点。因而,采用声光信号处理技术解决带宽、高增益和实时并行处理问题具有重要意义,声光信号的采集系统的设计是整个声光系统关键之一。这里设计了一个基于FPGA和USB 2.0的高速CCD声光信号采集系统,为声光信号采集提供了硬件平台。

2019-03-12 08:45:17 1339

1339

电子发烧友网为你提供基于Verilog的FPGA与USB 2.0高速接口设计资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-12 08:53:53 16

16 FPGA_ASIC-MAC在FPGA中的高效实现(理士电源技术有限公司)-该文档为FPGA_ASIC-MAC在FPGA中的高效实现讲解文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-08-04 19:03:13 8

8

电子发烧友App

电子发烧友App

评论