DCM一般和BUFG配合使用,要加上BUFG,应该是为了增强时钟的驱动能力。DCM的一般使用方法是,将其输出clk_1x接在BUFG的输入引脚上,BUFG的输出引脚反馈回来接在DCM的反馈时钟

2018-05-11 03:53:00 1566

1566 一般认为输入点数是按系统输入信号的数量来确定的。但在实际应用中,通过以下措施可达到节省PLC输入点数的目的,下面以FX1N系列PLC来介绍。

2023-06-01 09:49:31 610

610

大家好,对于BUFG-BUFG级联对错误,我有[Place 30-120]次优放置。我知道错误的发生是因为BUFG无法级联...请参阅下面的“有问题”逻辑。如您所见,时钟多路复用器的输出连接

2018-10-29 14:20:35

BUFG BUFG BUFGP BUFGDS 等含义以及使用目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序

2014-11-24 17:58:10

嗨,当在Planahead 10.1中运行DRC检查时,我收到此错误:位于DCM_ADV_X0Y5的DCM clock_divider_i连接到位于BUFGCTRL_X0Y25的BUFG

2020-06-02 13:49:29

嗨,我们很有兴趣使用具有PLL和MMCM的高频(高达1066 MHz)的Virtex 7(-3速度等级)。BUFG和MMCM静态精细相移是否在此频率下正常工作?我可以使用包括PLL,具有静态精细相移

2020-07-14 16:05:47

嗨,对于BUFG,是否有关于Max Fan的经验法则或建议?如果我还没有找到它。我的问题是每个人都告诉我一个主时钟的BUFG,一个V7的完整设计是可以的。然而,我在Timing Violation

2019-03-20 12:28:13

四、时钟资源介绍4.1 BUFG BUFG在“Device”中如图2-1-1所示,其中它有多种模式可根据需求来选择使用,可以实现将时钟传递到FPGA中的各种资源,具体架构在上文已做阐述,本文

2022-01-06 08:21:32

要提升输出功率有效的方法就是电池升压后再给功放供电。由于升压转换效率的存在又影响电池的续航时间。有效提升机器续航时间办法有:1.用同步升压,同步升压可以规避非同步升压整流二极管固有压降大而损耗大的相对

2020-10-27 06:46:06

关电源的PCB布线不是很精通,这个办法很有效。 2.输入电容采用电解电容和瓷片电容配合来,如果方便的话就再并联几个0.01uf的贴片电容,如果有钽电容就更好了,但是大家一定要注意:所有电容的耐压值电压输入电压

2016-01-18 14:30:43

本帖最后由 island008 于 2014-2-18 00:02 编辑

手机流量使用问题一直都被用户们所关注,怎么才能节省流量呢?下面小编就分享一些节省流量的办法,分析出具体步骤,让大家节省

2014-02-18 00:00:41

芯片上正确的GTX站点。我已成功构建并测试了4 GTX版本的频道。我可以使用这种方法成功构建一个8通道版本,但由于BUFG耗尽,我不能再使用GTX了(我还需要两个以上共10个)。有8个GTX通道(除了我

2020-06-17 07:46:51

正确的方法是使用3个BUFGMUX组件,然后是BUFGCE,但这有问题:1)即使我有V2000 Virtex7 FPGA,由于放置限制,我最多只能使用32个BUFG。2)假设我可以放弃并减少时钟区域

2020-06-19 12:53:16

嗨,我使用virtex7 xc7vx690t来运行P& R但总是得到unrouted网络的错误。但我发现报道的错误是“BUFG驱动SLICE”。我认为BUFG是全球时钟资源,它可以驱动

2018-11-13 14:16:20

在syn中设定了bufg为32个,syn后的报告中也是32个bufg。但是执行impl后,vivado报错说是生成了35个bufg,超出芯片容量。重新syn之后还是这样。不知道是什么原因,怎么syn和impl的结果会不同。

2015-03-09 17:00:15

你好团队xilinx,我正在使用zed板,需要通过tcp链接通过以太网接口接收5MB的大文件。我能够以大小为1446字节的数据包接收它。有没有办法立刻收到完整的有效载荷?等待回复。提前致谢。问候,Akash.O

2020-04-29 09:58:21

大家好。BUFG资源和DCM / PLL模块在许多FPGA线路上使用专用时钟布线资源。对于SerDes应用,我们使用BUFIO2来获得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

为什么BUFG驱动DSP48E1的CE会出现问题?警告:LIT:683 - DSP48E1符号“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

什么是功耗?计技巧为什么能够节省功耗?

2021-04-08 06:49:56

你知道在空闲任务中使用一行代码可以节省多少能量吗?FreeRTOS商业版本OpenRTOS及安全版本SAFERTOS的提供商WHIS创建了一个基本应用程序,在RTOS的idle hook中添加了一条

2022-06-24 15:38:36

本文介绍使开发物联网解决方案更加有效的方法的6个方法。

2021-05-20 06:10:27

我正在尝试在结构中使用GTE时钟。根据架构指南,这就是BUFG_GT的用途。但是对于Vivado 2014.1,当我这样做时:电线wClk156; IBUFDS_GTE3 mIBufDS(.I

2020-07-20 14:42:32

嗨我使用vivado 2015.4,我收到了这条消息:[放置30-150] MMCM-BUFG组件对的次优放置。如果此子设计可接受此子优化条件,则可以使用.xdc文件中

2020-04-24 07:44:55

1、聊一聊 一首含蓄而又简单的歌曲,细细评味或许会在不经意间想起曾经的那么ta!2、正文部分1 现象对于MCU省内存,bug菌应该说得够多了,今天这篇文章主要是对使用const省内存办法中一个小细节

2022-01-25 07:08:04

大前提:C语言基础扎实且熟悉单片机编程(或者会自己查资料解决基础问题)小前提:该功能较为复杂不封装函数难以促成简洁的代码第一步:寻找自己要实现的功能的所有子功能的介绍及实现办法举个例子:当我们目标

2021-11-22 07:22:55

我在vivado 2016.3中看到了以下地方的错误错误:[放置30-675]支持全局时钟的IO引脚和BUFG对的次优放置。如果此子设计可接受此子优化条件,则可以使用.xdc文件中

2018-11-09 11:37:33

嗨,大家好,我正在使用Vivado 2014.对于设计,是使用BUFG或IBUF / OBUF原语到端口引脚还是工具将在分配PIN时自动获取缓冲区?我没有为时钟引脚A2YCLK0分配BUFG。在我

2019-04-03 13:28:08

实际应用经常只会用到数据转换器模拟信号范围的一部分。如果在应用中只用到该范围的一半或者四分之一,则可以很容易地计算出有效分辨率。但如果遇到的是一个更复杂的分数,又该怎么办呢?本文将介绍在使用任何模拟信号范围时有效分辨率的计算。

2019-07-17 06:59:27

)然后传递到BUFG。 BUFG的输出驱动逻辑。如果没有BUFG,即使在13.5MHZ CLK上也无法满足时序要求。我们的问题是LX150设备只有16个BUFG。我们仅将8x用于此模块,我们的整个系统

2019-07-01 10:20:35

我们已经介绍了应用单片机的外设功能的结构和使用方法。本期我们介绍更有效地应用单片机而必须的外设功能——“中断功能”。

2021-02-25 08:07:05

在我合成一个设计之后,我发现估计BUFG的使用率是44,但是设备只有32个。所以我想我必须减少我手动使用的BUFG的数量。但是第一步是我需要在哪里使用这些BUFG,所以在打开合成设计之后,我怎样才能

2019-03-06 07:37:30

使用7系列FPGA,ISERDES的新时钟方法出现了,至少我以前从未见过它:由BUFG驱动的CLK,由不同的BUFG驱动的CLKDIV您可以查看这两个文档以获得更好的解释:7系列:http

2020-07-16 09:42:53

当我放BUFG bufg_axi_rst_i(.O(axi_rst),. I(~frst [0])); //它是https://github.com/Elphel/eddr3/blob/master

2018-10-19 14:38:55

嗨,在我的设计中将Clock引脚连接到BUFG时出现以下错误器件为xc7a200tffg1156,引脚编号为P29,是时钟引脚。解决这个问题应该有什么限制?[放置30-574] IO引脚和BUFG

2020-08-04 06:38:55

建立灵活的、节省成本的ECU测试系统本文简要介绍了发动机控制器的功能和测试。目录:ECU的历史ECU的用途为何要测试ECU?测试系统开发员面临的挑战ECU怎样工作?ECU 功能模块National

2009-12-14 16:17:03

比较器另一端是ramp 电压比较器输出是pulseosc是用referance 电压的分压作为 比较器一端输入(中间有单位缓冲器)发现vref 受osc 影响不小,在ramp 剑锋时刻 有小幅震动在电路上有办法 有效隔离吗?

2012-01-11 10:00:50

方法是增加一个连接到posedge clk的计数器,并使用第24位的值来设置clk上的led触发器。我读了一个线程,其中有人使用BUFG根据计数器内的一个位创建一个触发信号似乎更简单..但它对我不起作用

2019-06-11 08:41:01

嗨,运行时出现此错误:错误:[放置30-467]根据用户约束,此设计需要在SLR no的下半部分放置17个BUFG实例。 1.由于设备容量限制,这是不可能的。 SLR的每一半只有16个BUFG站点

2018-10-30 18:02:31

Ross Bledsoe写道:我正在从一系列REAL64中提供多种颜色警报。我试图将显示屏上的有效位数限制为四位。我尝试在数字选项卡中更改颜色警报的属性,没有效果。有没有办法将有效数字限制为4?感谢

2019-10-31 13:11:55

编写裸机Bootloader有什么办法判断APP是否有效,从而避免重复跳入导致复位再跳入的情况。

2024-02-19 06:19:55

7系列有多少BUFG?我从报告中读到有128个,这是正确答案吗?

2020-08-25 15:49:16

嗨!我想知道BUFIO2 + BUFG和ODDR2的解决方案是否用于时钟路由在时钟源上可以避免使用Spartan 6(使用直接赋值)已经从外部缓冲了。我的意思是,而不是 bufio2_axi_clk

2018-10-23 10:24:05

嗨,我使用IBUFDS将差分时钟信号转换为单时钟信号,这个转换后的单个clokc信号将用于多个PLL_ADV。那么,我应该为每个PLL_ADV的clk_in添加BUFG吗?或者我只需要在IBUFDS

2020-07-23 10:57:17

我正在使用Spartan 6 FPGA,并且在我当前的设计中运行低BUFG。如果我阻止工具在DCM环回(CLK0- > CLKFB)中自动插入BUFG,那将释放我需要用于其他用途的BUFG。从

2019-07-12 09:38:54

请问信号发生器是如何效节省测试时间的?

2021-05-06 07:43:02

你好朋友, 我已经获得了Virtex5 FPGA应用笔记XAPP856,根据图6和表3,我们不能使用DCM和BUFG驱动OSERDES来实现SFI-4.1。因为Virtex 5系列中的DCM最多可以

2020-06-10 12:48:08

警告:[放置30-574]具有时钟功能的IO引脚和BUFG对的次优放置。这通常是一个错误,但CLOCK_DEDICATED_ROUTE约束设置为FALSE,允许您的设计继续。强烈建议不要使用此覆盖

2020-06-17 11:33:53

在某些情况下,采集此类数据可能非常困难。有没有更好的办法来采集数据,并保证数据是有效的?本文介绍了几种数据采集应用,并将说明一些不同的工具如何帮助您采集和分析数据。

2021-04-09 07:04:11

在线评估贮油罐底部腐蚀状况的经济有效技术:本文介绍了一种非侵入式罐底腐蚀在线检测技术。应用该技术可为用户节省数百万美元的损失。本文在介绍该技术原理的基础上阐述了

2009-11-24 08:29:27 28

28 层出不穷的信号发生器可有效节省测试时间

所有电子电路和电子设备都接收输入信号,然后将其处理成新的不同的输出信号。工程师在设计和测试电路及设备时会从哪

2009-11-05 08:53:50 1433

1433 TI最新资料撷取系统可有效节省75%的功耗、空间及成本--ADS8201

2010-01-08 17:38:04 550

550 无线互访故障现象及应对办法介绍

伴随着无线上网技术的不断成熟以及无线网络设备价格的不断走低,无线局域网的“身影

2010-02-23 14:39:20 455

455 广东省无线电管理实施办法 第 一 章 总 则

第一条 为了加强无线电管理,维护空中电波秩序,有效

2010-03-29 11:59:33 578

578 以模拟与数字电路实验课程为例,简述了改进学生实验考核办法的必要性,提出了一个有效的可操作的综合性、设计性实验考核办法,并讨论了该考核办法的实施效果和存在的问题。改革学

2011-04-01 12:27:36 0

0 本问介绍了CADENCE软件组件Allegro开机不能正常启动的问题的解决办法

2016-08-18 17:26:55 0

0 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义

2017-02-08 05:31:40 2048

2048

本文档内容介绍了通过运动检测节省电池的背光控制。

2017-09-17 10:16:09 2

2 本文档内容介绍了基于面板与PLC通讯的故障处理办法。

2017-09-25 18:29:55 4

4 本文首先介绍了音箱发声的原理,其次阐述了四种音箱没声音的原因和解决办法,最后还介绍了电脑音箱没声音的原因及解决办法,具体的跟随小编一起来了解一下。

2018-05-28 14:33:41 42281

42281 本文主要介绍了MES系统无纸化操作可以从这三方面节省.

2018-06-26 08:00:00 2

2 本文针对Vivado中实现的逻辑锁定和增量编译进行的工程实例介绍,文中有对应工程的下载地址。友情提示:(1)增量编译只允许修改当前工程不超过5%的时候才有效,一般应用于较大工程添加修改

2019-07-06 10:32:42 6746

6746

还会造成模具使用的寿命,那么利用什么办法来有效去除钢坯表面的氧化皮呢? 传统的清理方法已经过时,比如说,酸洗、钢丝刷、打磨、抛丸等。这些方法不仅污染环境,而且效率低,费工费时,造成人力资源的浪费。随着高压水除

2020-10-05 11:31:00 20745

20745 腐蚀电路板的进程中不免会遇到一些疑问,这时分咱们就需求有一些应急的处理办法,下面电工之家就来介绍一下腐蚀电路时的一些应急处理办法:

2020-03-22 16:36:00 8525

8525 ,但是使用的方法不一样,芯片的面积是不一样的。基于SRAM有两个事实: (1)1R1W的SRAM面积要比1RW的SRAM的面积大不少。 同样规格的SRAM,增加一组读写接口,其面积会增加很多。但是有一种办法其实有可能将本来需要使用1R1W的SRAM改用1RW SRAM替掉,从而节省

2020-06-22 13:36:09 1116

1116 本文主要介绍了触摸灯的工作原理及触摸灯自动亮的解决办法。

2020-08-11 10:00:02 31982

31982 如果是问保护接地(零)线的接地电阻是否合乎要求(即有效)的话、可以用两种简单易行办法测试。

2020-11-23 15:54:25 8377

8377 电子发烧友网为你提供6个办法有效提升电路板的电磁兼容性资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-01 08:40:03 11

11 需凭借专门的仪器查看才干发现。一般电子产品都有几十、几百个元器件,乃至成千上万个元器件,靠查看每个元器件来发现其中的毛病,是很困难的。下面介绍下钽电容检修办法。

2021-04-09 11:51:56 860

860 节省空间,降低EMI

2021-05-20 11:42:15 6

6 问题描述:前几天我遇到了这个问题,刚开始有点恐慌,以为电脑坏了,就在网上查找各种解决办法,大多数人都用长按电源按钮的方法解决了,但是包括我在内的一些朋友就是不行。解决办法:最后得知电脑是因为气温太低

2022-01-10 12:55:06 7

7 LED显示屏通讯新号载入不上的原因和解决办法

2022-02-10 14:43:15 2897

2897 梯云物联:深圳电梯IP五方对讲有什么问题和解决办法?

2022-04-11 18:16:59 5026

5026 有效解决燃煤电厂再热管腐蚀的办法及案例

2022-05-31 15:33:34 0

0 运放输出钳位机理及避免办法

2022-10-28 12:00:21 0

0 AN4515_在STM32F41x系列MCU上应用BAM模式节省功耗的介绍

2022-11-21 08:11:41 0

0 一站式PCBA智造厂家今天为大家讲讲什么是PCBA加工焊点拉尖?PCBA加工焊点拉尖产生原因及解决办法。接下来为大家介绍PCBA加工焊点拉尖产生原因及解决办法。

2023-05-10 08:56:46 936

936 有些设备管理者在遇到轴类磨损的故障之后,多数为了节省,选择补焊的方法进行维修,但补焊修轴真的有效吗?会对轴有影响吗?下面小编给大家一一介绍说明下,看看到底如何有效维修。补焊修轴对轴的影响:补焊会对

2022-02-20 09:53:12 580

580

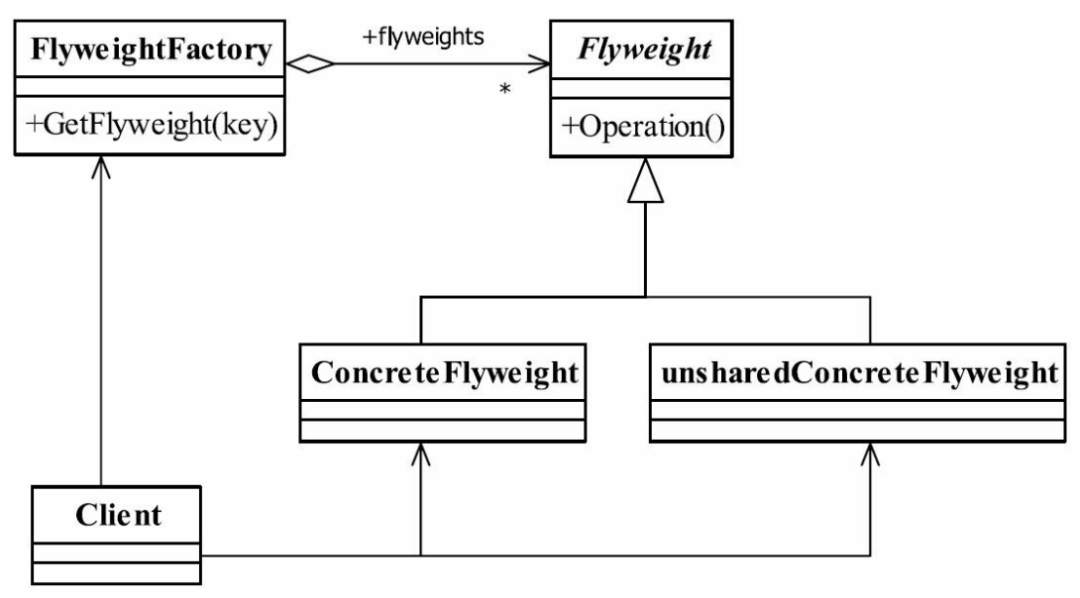

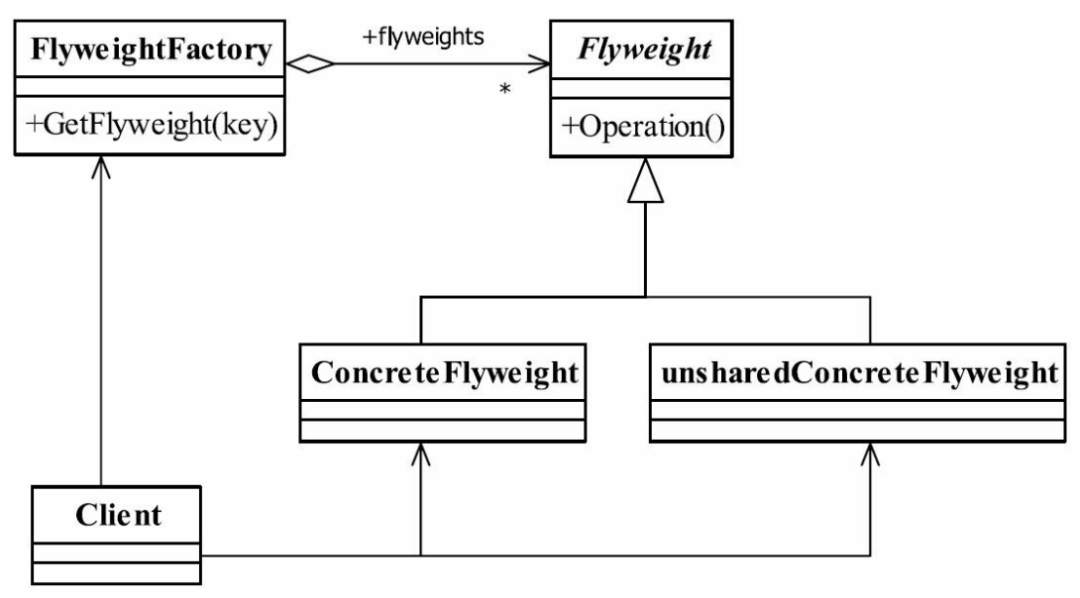

相信大家日常开发过程中,一个优秀的程序猿写出的代码一定要节省空间的,比如节省内存,节省磁盘等等。那么如何通过设计模式来节省内存呢? 1、什么是享元模式? Use sharing to support

2023-10-09 10:31:58 271

271

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

2024-01-05 14:31:06 454

454

正在加载...

电子发烧友App

电子发烧友App

评论