电子发烧友网核心提示 :Xilinx ISE 14.2安装指南,包括Xilinx ISE 14.2软件下载、Xilinx ISE 14.2软件安装、Xilinx ISE 14.2相关产品介绍、Xilinx ISE软件激活、Xilinx ISE14.2软件启动和Xilinx ISE 14.2新建工

2012-10-31 11:59:13 61264

61264

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 Xilinx FPGA的组成部分 本文是以Xilinx Kintex UltraScale+ 系列为参考所写,其他系列有所不同,可以参考相应的user guide文档。 Xilinx家的FPGA有这

2022-12-27 15:54:52 1788

1788 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

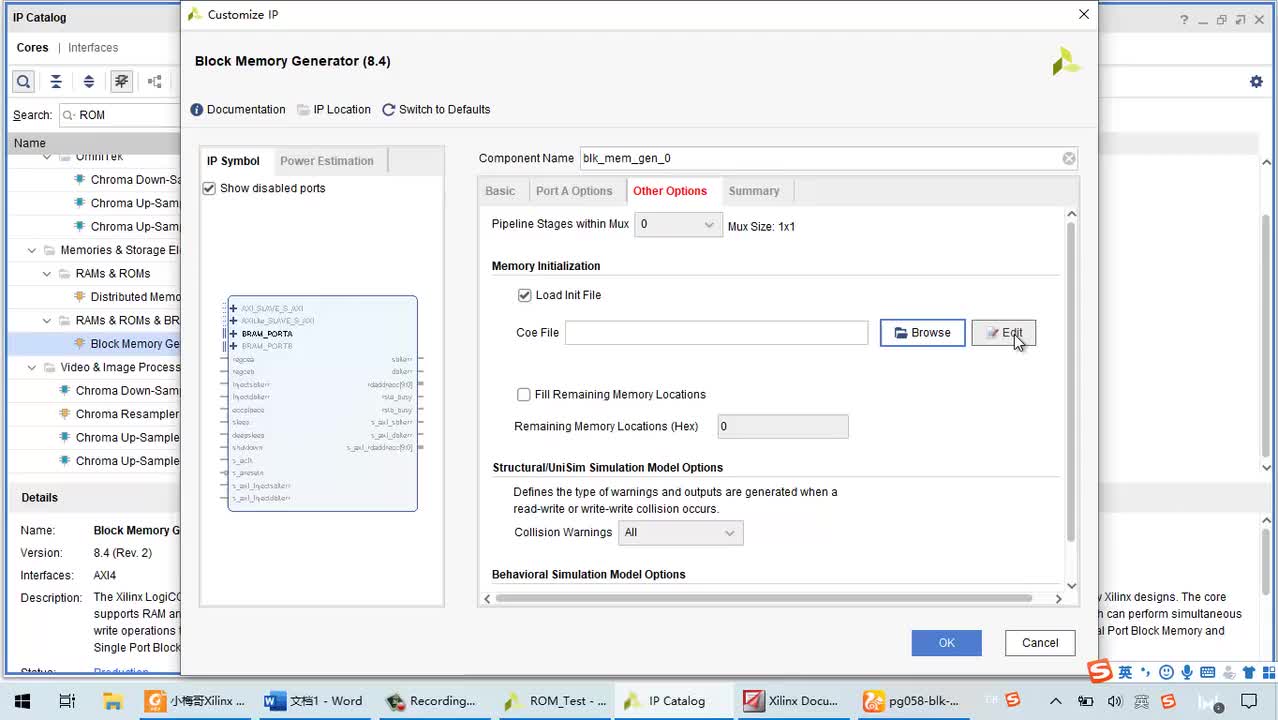

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:20:25

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:27:04

XILINX FPGA 芯片整体架构是如何构成的?XILINX FPGA 芯片有哪些资源?

2021-10-29 06:26:23

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

保险丝,保证用户安全使用开发板15、扩展接口 【主芯片剩余I/O资源均连到扩展接口上】 另外配套了大量的试验,使用户方便掌握Xilinx的CPLD/FPGA的编程设计。实验程序如下:1、串口收发数据

2011-11-17 13:12:57

支持所有Xilinx器件下载 包括FPGA CPLD ISP Configuration PROM 下载接口电压:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

可以找到以下资源以获取帮助以上来自于谷歌翻译以下为原文 Hello, We purchased a full edition of Xilinx- Vivado/Ise - in March/2016.My

2018-12-21 11:00:57

FPGA最小系统说白了就是设计一个最小系统,其可以作为日后一系列产品的基础,一是可以加快开发流程,二是可以降低开发难度,本次选用的芯片是Xilinx(赛灵思)的7系列(ARTIX)的FPGA

2021-11-11 07:39:20

LabVIEW资源进行编程,所有其他文件似乎编译得很好。编译似乎滞后于Core Generation步骤,大约30分钟后失败,并说由于xilinx 13.4错误导致编译失败。我已经包含了日志文件供您查看。在整个

2020-03-26 10:33:35

xilinx和altera区别分析1. 从好用来说,肯定是Xilinx的好用,不过Altera的便宜他们的特点,Xilinx的短线资源非常丰富,这样在实现的时候,布线的成功率很高,尤其是逻辑做得比较

2012-02-28 14:40:59

嗨,我在系统生成器2014中使用黑盒子.4在模拟模式下选择vivado模拟器。如果我运行该项目它正常工作,但如果我在系统生成器或黑盒vhdl中更改某些内容,则会出现此错误:Xilinx模块库中发

2018-10-30 11:07:57

大家好,我一直在从一系列合成迭代开始和关闭这些迭代。有人能告诉我为什么会这样吗?时钟太多了?解决办法是什么?[形状生成器18-119]未能创建I / OLOGIC借道形状例如system_i

2018-10-19 14:35:03

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

Cortex-A9 处理器,但该器件上的 FPGA 数量存在差别,如表 1 所示:[td]Xilinx Zynq SoC可编程逻辑单元块 RAM 的容量大小 (Mb)DSP 切片

2018-08-31 14:43:05

`如题,打算拿手里的十万逻辑资源Altera板子交换Xilinx板子,现在只打算换Xilinx的FPGA的板子,可以是自己做的或者是其他,但一定要好使的!板子是自己设计的,也是自己焊接的,焊接的比较

2015-06-19 21:38:36

遇到了意外错误。建议您在此情况持续存在的情况下保存任何未保存的工作。如需进一步的帮助,请参阅http://support.xilinx.com上的答案数据库和其他在线资源有任何建议如何解决这个问题?谢谢。

2020-05-29 16:06:51

RAM)的时延和抖动都为最小。为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8

2019-10-22 06:01:34

HY,我想在xilinx Blockset中估计FFT7.1块的各个体系结构的资源。有没有办法做到这一点?当我尝试使用“资源估计器”-Block时,结果总是43个IOB。问候Jan以上来自于谷歌翻译

2018-10-16 07:21:32

'une erreur Xilinx。详细信息:错误:位置:906- 由于位置限制导致违反时钟区域规则,因此无法放置和路由由IO时钟网络驱动的组件。 IO时钟网被BUFIO驱动锁定到站

2018-10-19 14:36:19

FPGA的特点及其发展趋势IP资源复用理念与IP Core设计基于Xilinx FPGA的嵌入式系统设计

2021-04-30 07:21:50

嗨,我是FPGA编程的新手。我在Xilinx ISE中使用VHDL进行设计。我的综合结果包括:FF,LUT,内存LUT,I / O,BRAM,DSP48,BUFG。我非常感谢能够帮助我解释每个资源

2020-03-24 10:14:15

某些Xilinx资源包含一个显示“所有版本”链接的按钮。有没有所有版本的xapp1052.zip可用的地方?谢谢,埃米特

2020-04-30 08:18:45

UART 4 UART参考设计,Xilinx提供Verilog代码 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 usb xilinx代码,usb xilinx源代码,usb xilinx程序

The lack of flexibility in reconfiguring the PC has been

2009-06-14 09:04:25 41

41 Xilinx Sol

2009-11-28 11:56:48 14

14 怎样写testbench-xilinx

在ISE 环境中, 当前资源操作窗显示了资源管理窗口中选中的资源文件能进行的相关操作。在资源管理窗口选中了 testbench 文件后

2010-02-09 13:46:12 64

64 Xilinx下载电缆原理图

2011-01-18 16:09:34 114

114 xilinx实验板原理图:

2012-03-20 14:02:47 235

235 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

Xilinx FPGA系列入门教程(二)——Xilinx FPAG开发环境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 xilinx_ise9.01中文教程 xilinx_ise9.01中文教程

2016-02-18 18:16:58 0

0 Xilinx FPGA工程例子源码:Xilinx EDK设计试验

2016-06-07 14:54:57 9

9 Xilinx FPGA工程例子源码:Xilinx 公司的加法器核

2016-06-07 15:07:45 12

12 Xilinx FPGA工程例子源码:Xilinx 高级试验的代码

2016-06-07 15:07:45 19

19 Xilinx FPGA工程例子源码:Xilinx 的I2C工程

2016-06-07 15:07:45 25

25 Xilinx FPGA工程例子源码:Xilinx.CPLD源码参考设计

2016-06-07 15:07:45 33

33 xilinx原语的使用,建议有一定经验的参考。

2016-12-17 11:58:56 13

13 Xilinx学习资料

2017-01-31 20:43:43 68

68 谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

。从新手的角度,我想谈一下自己的一些感受: 网络资源: xilinx主要是做FPGA的,以前没有接触过,zynq是接触的第一个xilinx的产品,总体上感觉资源比较丰富,论坛,文档资料都能轻易获取,就是对英文水平有较高要求,官网上的资源,文档基本都是英文的,所以英文必须得过关。

2017-02-08 06:31:11 209

209 1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 1315

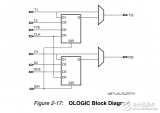

1315 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

2017-02-11 09:21:12 2426

2426

xilinx 约束实现

2017-03-01 13:12:47 15

15 Xilinx TI LVDS 参考设计

2017-03-01 13:13:09 16

16 最重磅的发布,最新的视频和白皮书,还有最新的课程介绍,以及来自 Xilinx 合作伙伴和客户的成功案例,实用工具和套件分享。一文即可掌握,本月我们给您带来了什么样的资源,点击“阅读原文”阅读详情。

2017-09-20 11:39:57 3236

3236 xilinx 原语使用方法

2017-10-17 08:57:42 11

11 xilinx原语使用方法

2017-10-19 08:50:39 15

15 Xilinx机器视觉导论

2017-10-27 08:38:09 6

6 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

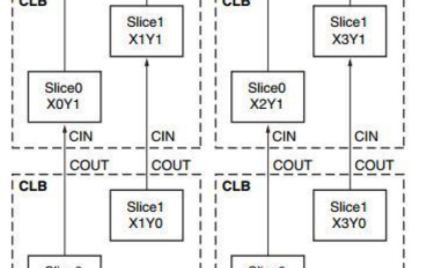

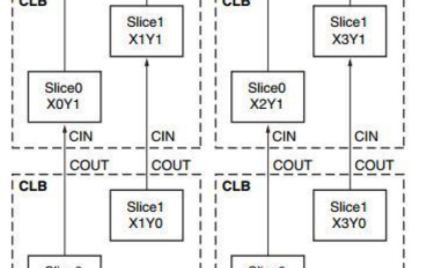

这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

2018-03-21 14:48:00 4672

4672

共同愿景就是帮助用户简化设计,降低开发门槛,让用户更多关注创新本身,甩掉硬件设计与调试的烦恼。威视锐与Xilinx将提供更多面向行业的解决方案,加快FPGA的创新应用。

在Xilinx的30

2018-06-06 02:45:00 3934

3934 Xilinx Zynq™-7000

2018-06-04 13:47:00 3392

3392 介绍赛灵思为各企业提供的专业的关于Xilinx的资源培训,以及课程内容

2018-05-22 13:47:33 3154

3154

现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

2018-10-22 11:00:43 5270

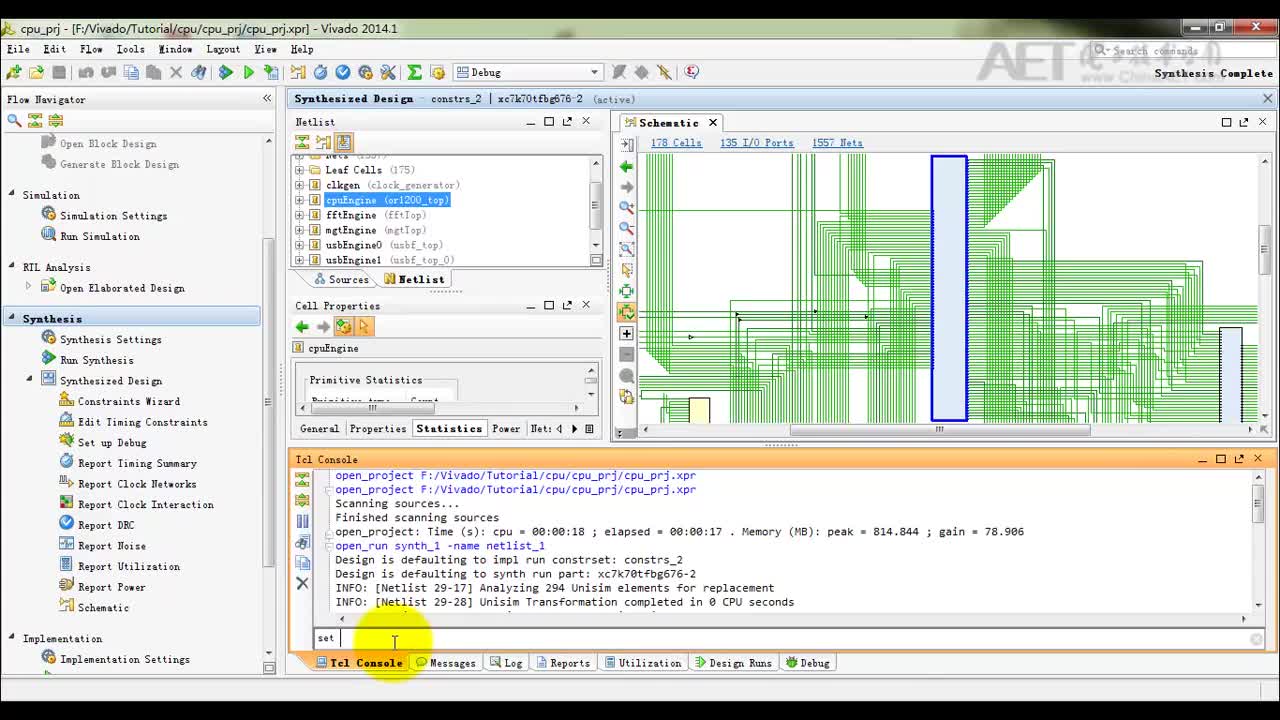

5270 Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 12305

12305

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。 在用Vivado建立

2019-09-15 12:21:00 4826

4826

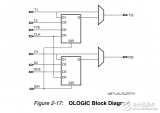

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。

2019-02-17 10:55:30 35932

35932

Xilinx的FPGA的基本结构是一样的,主要由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2019-06-11 14:28:17 3600

3600

命名规则 5.7系列资源概括 1.Xilinx的四个工艺级别 Xilinx目前主要产品有四个工艺等级,通常情况下,Xilinx的产品每个工艺都会有Spartan、Artix、Kintex和Virtex

2020-11-13 18:03:30 14065

14065 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 24

24 本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 Xilinx LogiCORE IP块内存生成器(BMG)内核是一种高级内存构造函数,它使用XilinxFPGAs中的嵌入式块RAM资源生成区域和性能优化的内存。

2020-12-09 15:31:00 22

22 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 15:31:13 9

9 Xilinx7系列FPGA的体系结构具有灵活的内部内存资源,可以配置为各种不同的大小。本白皮书详细介绍了可用的功能,说明了各种可用内存大小,并显示了使用不同资源执行不同大小内存功能的利弊。

2020-12-09 16:15:00 8

8 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)

2020-12-25 17:34:00 16

16 xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

2020-12-29 16:59:33 12

12 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

2020-12-29 17:27:00 3

3 OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks)和OLOGIC2(位于

2020-12-30 16:27:50 9

9 SRL(移位寄存器)资源,在FPGA中都有,不过是叫不同的名字。Xilinx FPGA内部的LUT有个特殊功能,就是可以配置成可变长度SRL。

2020-12-31 16:45:35 8

8 引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 4353

4353

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 自从 Vitis 发布后,Xilinx 在 Github 上持续开源了很多资源,方便开发者进行自己的设计,减少产品上市时间。所以本期文章我们来看下如何获取和使用 Github 上的开放资源。

2021-04-09 11:51:40 3129

3129

Xilinx参考设计(维基网站)

2021-05-12 10:00:30 3

3 在vivado中 ,如何查看各个模块的资源占用情况呢?方法如下。以在xilinx官方评估板VC709的microblaze的软核处理器例程为例。工程如下图模块组成。

2022-07-08 10:01:27 9566

9566 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 VicorPoweringInnovation播客介绍了OLogic如何推崇高密度电源模块来推动当今的机器人革命从玩具到建筑工地工具OLogic加速机器人创意从概念到生产的进程马萨诸塞州安多

2024-02-28 00:00:00 776

776

VicorPoweringInnovation播客介绍了OLogic如何推崇高密度电源模块来推动当今的机器人革命从玩具到建筑工地工具OLogic加速机器人创意从概念到生产的进程马萨诸塞州安多

2024-02-28 00:00:00 748

748

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

电子发烧友App

电子发烧友App

评论