FPGA 管脚分配需要考虑的因素FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 10:27:54

解决方案工具包。它的主要工作是由软件来自动生成、优化FPGA芯片的管脚分配,提高FPGA/PCB设计的工作效率和连通性。FSP完成两项重要工作:一、可以自动生成FPGA芯片的原理图符号(symbol

2011-10-18 11:44:31

小弟刚买的FPGA核心板,打算自己画底板的说。买的核心板没有给引脚配置,只给了原理图,原理图上虽然标明了FPGA的引脚,可是……这个东西怎么看呀?它不像是买的开发板那种,什么A11,W8这种,而是IO,DIFFO_T13P这种。我是该找卖家要一份,还是说要自己看,慢慢去对它的引脚呢?

2017-06-12 08:27:50

FPGA管脚分配需要考虑的因素 FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 11:34:24

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-03-25 18:46:25

FPGA管脚分配需要考虑的因素.pdf

2012-08-20 19:23:04

FPGA的管脚主要包括:用户I/O(UserI/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应

2019-09-18 07:34:49

FPGA配置引脚说明使用EMCCLK引脚,全速加载程序FPGA加载时序

2021-02-03 06:47:35

一、FPGA配置引脚说明1、CFGBVS如果VCCO0连接至2.5V或3.3V,CFGBVS连接至VCCO0。如果VCCO0连接至1.5V或1.8V,CFGBVS连接至GND。建议bank...

2022-02-08 06:52:31

引脚,按照下表进行选择。 3、PROGRAM_B(input) 低电平有效,为低时,配置信息被清空,将配置过程重新进行。上电时保持PROGRAM_B为低电平不会使FPGA配置保持复位状态。而是

2021-01-15 16:43:43

配置引脚的电平值,发现相比起FPGA正常起来时候各配置引脚的电平值,起不来时候的引脚电平异常。检查FPGA的配置电路,发现配置相关的引脚nCONFIG、nSTATUS、CONF_DONE、DCLK

2014-08-21 15:44:32

,版权所有)●部分配置引脚可以被复用,但是要谨慎使用,以免影响器件的上电配置过程。(特权同学,版权所有)FPGA配置电路的设计是非常重要的,相关信号引脚通常都是固定并且专用的,需要参考官方推荐电路进行连接。(特权同学,版权所有) Xilinx FPGA入门连载

2019-01-30 02:34:52

的GC_CLKPIN,PAR就会报错,反之,当一个信号分配的是GC_CLK PIN,无论是否扇出足够大,都会加入IBUFG,这也其实是FPGA内部结构造成的,只有全局管脚上有IBUFG,所以只要该信号用了全局管脚

2019-07-09 08:00:00

发出低脉冲 后,FPGA芯片经过一个初始化序列清空内部FPGA配置存储器。此序列开始时,DONE和INIT_B引脚均转为低。初始化完成后,INIT_B引脚转 为高,并采样芯片的配置模式及变量选择引脚

2012-08-12 11:56:42

FPGA各管脚含义用户I/O:不用解释了。配置管脚:MSEL[1:0] 用于选择配置模式,比如AS、PS等。DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。DCLK FPGA串行

2014-12-29 11:46:33

FPGA在Verilog程序写完后,针对实物芯片,如何分配引脚?!在QtsII软件中仿真后有引脚分配,但感觉和实际的引脚应该有区别吧?问,该如何区分?!

2013-04-03 13:14:13

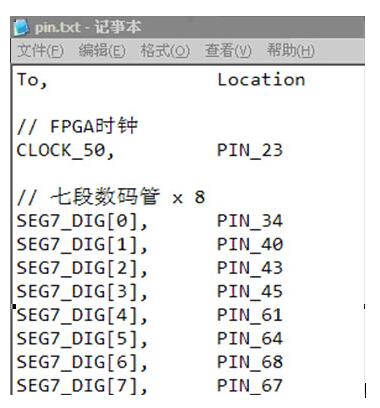

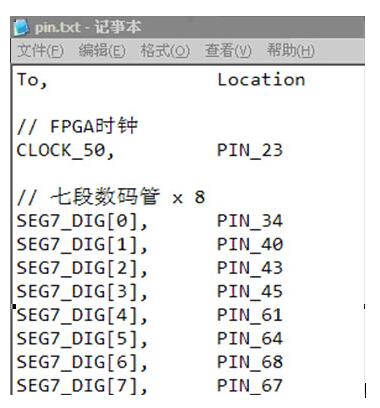

保存在该工程文件夹下)步骤二:添加以下格式内容,格式如下图所示;步骤三:点击保存,引脚分配完成。4、使用.tcl文件进行引脚分配:步骤一:生成.tcl文件,选择菜单栏Project-->

2018-07-03 07:22:06

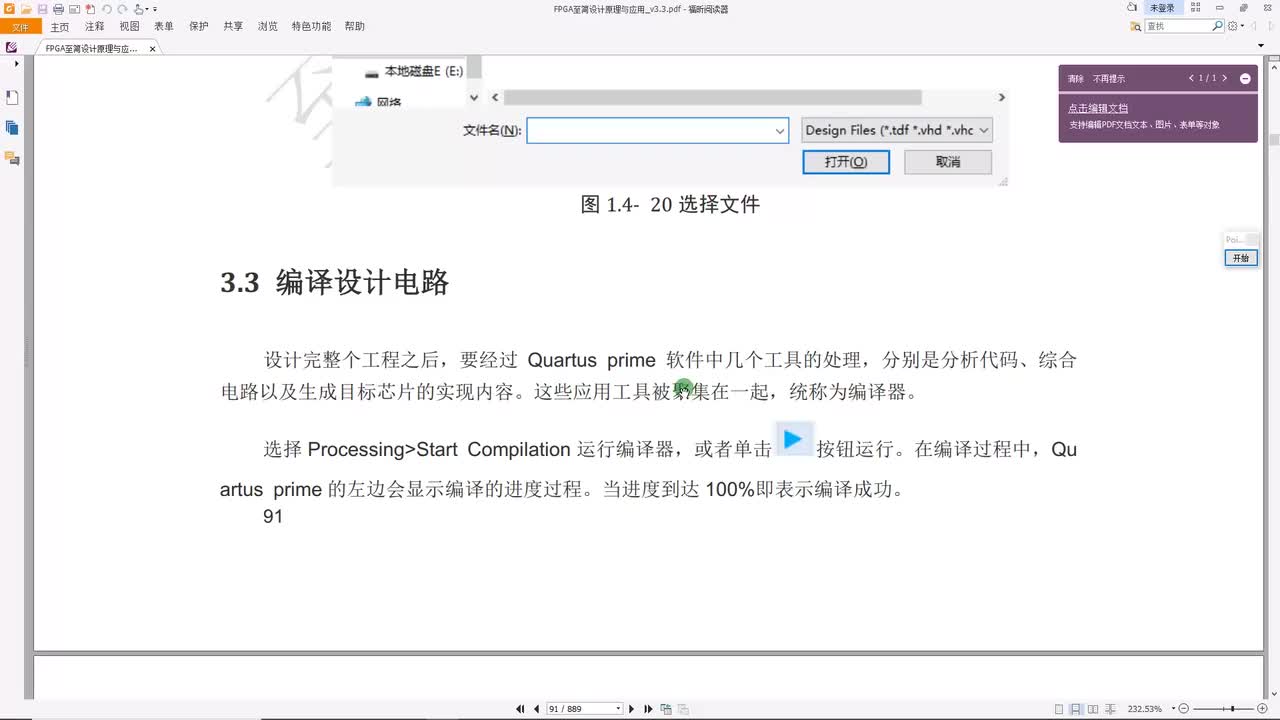

分析、综合。完成后会提示错误和警告数。再点击分配引脚,FPGA可以灵活分配引脚,极大地方便了PCB布线和后续设计。这里根据原理图上LED的位置和按键插线位置设置引脚,以及电平标准。完成配置后,点击编译

2011-07-29 11:18:16

`引脚分配规划和扩展I/O电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 核心板上专门留了一个LED

2015-05-06 11:31:16

FPGA如何对引脚进行分块?是由VCC的电压不同进行自行设计分块?还是每个块的引脚都是固定的?在进行DDR3与FPGA的硬件连接时,由FPGA的芯片手册得采用SSTL_15电压标准,即VDDQ

2021-11-29 16:10:48

完成之前,由于当前FPGA还没有下载程序,无法区分哪些引脚被设计所使用,哪些引脚没有被使用。此时的普通IO包括两部分: 该封装中所有的通用IO引脚。 当前所选择的模式下没有使用到的所有功能复用管脚

2021-01-08 17:29:15

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-06-17 08:55:43

配置历史回顾当FPGA首次面世时,可选择的配置存储器是并行EPROM或并行EEPROM产品。随着时间的推移,NOR闪存技术应运而生,同时因其系统内可重复编程性和高性价比而被广泛采用。在第二次革命性转折

2021-09-03 07:00:00

FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑

2024-01-10 22:40:14

FPGA设计管脚分配注意点

2012-08-11 16:10:10

/区域时钟,你将可能需要使用高速总线附近的管脚,最好提前记住这个要求,以免最后无法为其安排最合适的引脚。如果某个特定块所选择的I/O标准需要参考电压信号,记住先不要分配这些引脚。差分信号的分配始终要先于

2020-09-07 11:01:46

用tcl文件配置引脚后 点击 Run 后就退出到代码界面,然后查看了引脚是否分配成功发现没有分配,这是怎么回事呢?要怎么解决?

2013-09-25 20:00:30

我是fpga开发板的新手,我想知道如何开始使用引脚分配,特别是u*** / serial引脚连接。任何其他pin信息都会有所帮助谢谢

2020-07-19 11:47:31

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

ARM在片上资源确定的情况下,能否具备类似FPGA自由分配管脚功能的能力?比如说集成UART的TX/RX可以分配到任意管脚,而并不是只能分配到指定的几个管脚?谢谢

2022-08-01 14:17:49

板子简介:FPGA在PS配置模式下通过ARM配置;整个电路设计正常,有其他板子已经正常跑起来了。问题板子有以下几个问题:问题一:上电cfg,sta管脚状态异常:分别为0v,1.7v;正常的都是

2017-06-05 11:48:20

PlanAhead工具可以为大家提供相应的内部链接的检查3. FPGA EDITOR也能为大家找出内部逻辑的走线的检查和分析。4. 为什么会存在未分配的输出和输入引脚?这是因为该工程还存在尚未实现的后期功能。这些引脚

2012-02-24 10:49:28

嗨,我想用相同的xc7k325 FPGA来设计定制板而不是kc705评估板,并试图理解配置引脚(见附件1)。但我不明白FPGA_VBATT(引脚C10)的用途。它是否必须由外部来源高(参见附件2

2020-05-13 09:42:06

求助大神!!!FPGA对于DDR3读写,FPGA是virtex6系列配置MIG IP 核时,需要管脚分配1.原理图上dm是直接接地,管脚分配那里该怎么办2.系统时钟之类的管脚分配,是需要在原理图上找FPGA与DDR3之间的连线吗?还是?

2018-03-16 18:45:10

Quartus II 下FPGA管脚锁定在新建工程、编辑文件、编译、排错完成后就进入管脚锁定以及电平设置阶段。这里还是以一位全加器为例介绍管脚锁定。开发板使用FII-PRA006. 开发工具

2021-07-30 15:09:59

、摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总。 二、管脚分配方法FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按钮

2018-07-03 12:56:11

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

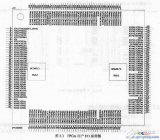

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-07-08 08:00:00

`Xilinx FPGA入门连载12:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植复制

2015-10-14 12:23:31

。分配引脚并设置row上拉电阻详细方式1. 如下图所示,在菜单 Assignments 中选择 Pin Planner,也可以直接点击面板上引脚分配的图标;12.进入引脚分配的界面之后,按照上面给出

2020-02-26 21:03:23

管脚分配有两种,一种就是手动,一个管脚 一个管脚的分配,还有一种就是使用脚本进行分配。一、手动引脚分配。菜单栏中:AssignmentsàPinPlanner出现如下的界面:在最下面,可以看到

2016-09-03 09:26:03

`例说FPGA连载32:PLL例化配置与LED之使用Pin Planner进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-14 16:59:04

`例说FPGA连载33:PLL例化配置与LED之使用Tcl Console进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-17 17:50:15

`例说FPGA连载34:PLL例化配置与LED之使用TCL Scripts进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-23 09:34:42

例说FPGA连载56:VGA显示驱动之复用引脚设置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 在该实例中,SF-VGA子板连接

2016-12-05 18:27:37

刚开始学习fpga,对引脚分配的问题不是很理解,求高手给予帮助 例如fpga的线路板上23引脚接clk ,28引脚是空余的 ,那么在编程的时候我可以用 28引脚接clk 吗?

2013-01-06 15:24:21

`勇敢的芯伴你玩转Altera FPGA连载49:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

2018-02-27 21:50:07

大家好,我刚开始学习FPGA并试图弄清楚哪些FPGA引脚可以分配我的数据信号。我正在使用FPGA Spartan 6封装TQG114器件LX9。查看产品规格,有102个可用的用户I / O.这是

2019-04-23 06:55:23

指定使用哪个器件引脚,也可以让工具选择需要的引脚。在后一种情况下,用户需要对这些引脚的分配进行备注,从而使得以后的PAR运行时继续使用相同的配置。ispLEVER提供两个基本特性以支持该功能

2012-02-27 15:18:09

在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是

2015-01-06 17:38:22

对配置模式需要作出合适的选择。 2.2 Viretex 系列FPGA 的配置模式 Viretex 系列FPGA 的配置模式是由上电时其专用配置管脚的状态决定的,对应的关系 如下表所示:因在系统中使

2015-03-05 15:31:07

配置历史回顾当FPGA首次面世时,可选择的配置存储器是并行EPROM或并行EEPROM产品。随着时间的推移,NOR闪存技术应运而生,同时因其系统内可重复编程性和高性价比而被广泛采用。在第二次革命性转折

2021-05-26 07:00:00

如何克服FPGA I/O引脚分配挑战?

2021-05-06 08:57:22

大家下午好,我计划使用主fpga板的IO引脚配置目标cpld板,即菊花链。我使用主fpga板的IO引脚连接cpld的JTAG头。如何编程master fpga的IO引脚来配置目标cpld?请发送与此相关的任何文件....谢谢问候Vimala

2020-03-24 06:43:09

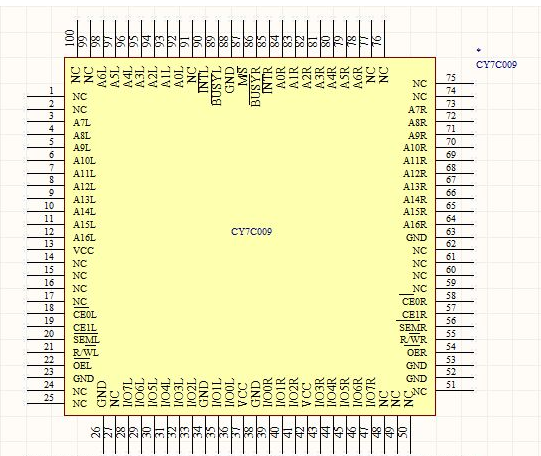

引脚都将转到fpga。我想将板作为第一步,以节省原型零件的费用,所以我试图找出在不使用ISE YET的情况下为地址线,数据总线等分配引脚的最佳方法。不会使用RAM。谢谢!以上来自于谷歌翻译以下为原文I

2019-01-21 06:02:55

求皓石FPGA开发板A4-PLUS原理图或管脚分配表。

2020-10-13 18:17:10

至芯科技之altera 系列FPGA教程 第十四篇 分配管脚

2016-08-11 03:33:10

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

ALTERA FPGA 特殊管脚说明、

管脚名称 器件系列 使用模式

2010-06-11 12:29:47 27

27 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 FPGA重复配置和测试的实现

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA

2010-01-26 09:39:56 544

544

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚信号指配的指导方针有

2010-11-08 18:23:52 868

868 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证

2011-01-25 18:19:39 163

163 基于SD卡的FPGA配置,本文给出了对Virtex FPGA 进行配置的情 况,该方案也可以适用于Spartan 系列FPGA。

2011-12-13 10:02:42 6095

6095

本文主要介绍了在FPGA开发过程中管脚分配时需要考虑的一些实际因素,减少后续开发过程中发生一些细节性的错误。

2016-05-25 10:01:13 18

18 现在的FPGA向引脚分配信号的任务曾经很简单,现在也变得相当繁复。

2016-07-27 20:24:00 6740

6740 管脚分配手册FPGA资料,又需要的下来看看

2016-08-09 14:45:44 64

64 设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

2017-02-11 03:48:34 10684

10684

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2017-05-18 10:51:54 29124

29124

通过SELECTMAP32接口配置和回读XILINX公司生产的V5系列SRAM型FPGA,被配置的FPGA以下简称DUT,产生配置时序的FPGA简称配置FPGA。首先硬件上应将M[2:0]接成110

2017-11-17 10:16:01 8730

8730 Cadence OrCADFPGA System Planner为FPGA和PCB之间的协同设计提供了一种全面的、可扩展的解决方案,它能使用户创建一个正确的、最优的引脚分配。FPGA的引脚分配是根据

2017-11-17 20:36:09 5453

5453

FPGA的管脚主要包括:用户I/O(User I/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应FPGA的芯片手册。

2018-05-25 07:39:00 19862

19862

本文档内容介绍了MagicSOPC主板FPGA-IO引脚分配表,供参阅

2018-03-15 15:50:59 6

6 将Quartus II中FPGA管脚的分配及保存方法做一个汇总。本文首先介绍了FPGA 的管脚分配方法,其次介绍了Quartus II自动添加管脚分配的方法,最后阐述了FPGA管脚分配文件保存方法,具体的跟随小编一起来了解一下吧。

2018-05-16 11:44:41 47376

47376

对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O引脚分配是必须面对的众多挑战之一。 由于众多原因,许多设计人员发表为大型FPGA器件和高级BGA封装确定I/O引脚配置或布局方案越来越困难。 但是组合运用多种智能I/O规划工具,能够使引脚分配过程变得更轻松。

2019-06-03 08:06:00 2312

2312 FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12:00 17251

17251 Altera FPGA支持AS,PS,JTAG等几种较常见的配置方法。 当为AS配置模式时,FPGA为主设备,加载外部FLASH中的数据至内部RAM中运行。当为PS配置模式时,FPGA为从设备,外部

2018-11-18 18:05:01 481

481 本文档详细介绍的是FPGA教程之CPLD和FPGA的配置与下载的详细资料说明主要内容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下载配置,三、FLEX/ACEX系列FPGA的下载配置,四、ALTERA的编程文件

2019-02-28 09:56:18 17

17 管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。

2019-06-28 14:34:07 3703

3703 FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。FPGA的加载模式主要有以下几种:

2020-04-07 08:00:00 16

16 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 最近完成了Arria10的原理图设计,想做一些记录,下面是关于FPGA配置的一些方式。 MSEL 将 MSEL 管脚直接连接到VCCPGM 或 GND,不需使用任何的上拉或下拉电阻,即可选择出所需

2021-03-12 16:26:58 11307

11307

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

2021-05-01 09:47:00 10367

10367

Lattice和Actel的FPGA使用称为反熔丝的非易失性配置技术,其主要优点是系统设计更加简单、不需要外部存储器和配置控制器、功耗低、成本低和FPGA配置时间更快。最大的缺点在于配置是固定的。

2022-12-01 11:08:45 862

862 在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发

2023-02-22 17:45:02 4537

4537 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38:53 597

597 随着 FPGA 的不断发展,FPGA本身自带的PCIE硬核的数量越来越多,本文以ZU11EG为例介绍,如何进行对应的 硬件 引脚分配。 设计目标:ZU11EG FFVC1760封装,挂载4组NVME

2023-12-14 15:45:01 194

194

电子发烧友App

电子发烧友App

评论