本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 15422

15422

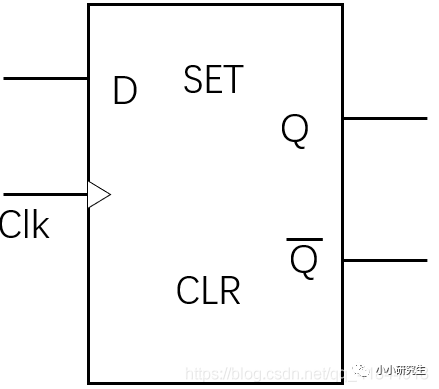

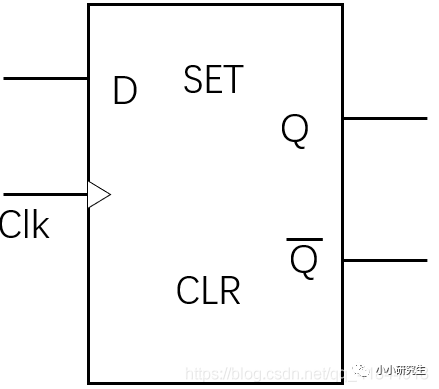

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 53525

53525

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2768

2768

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

2022-12-01 09:04:04 459

459 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-01-13 13:57:47 1830

1830

数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 476

476 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

芯片设计是现代电子设备的重要组成部分,其中组合逻辑和时序逻辑是芯片设计中非常重要的概念。组合逻辑和时序逻辑的设计对于构建复杂的电路系统至关重要。

2023-08-30 09:32:15 809

809 大神求救!我现在想要用FPGA实现一个数与一个数组(宽度为64)数相乘,累加,再取平均,用的是时序逻辑加上非阻塞赋值的方法实现,即从数组0开始相乘,一直到数组63,当乘完63时,将累加的数取平均输出

2017-09-13 11:02:51

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

以及高速数字电路的时序设计与优化。相信通过三天的学习,将会对学员在逻辑设计领域的工作和学习大有裨益。课程时间的安排上授课占60%,实验占40%。五、培训对象课程适合于使用FPGA器件进行科研、教学和产品

2009-07-24 13:13:48

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

基本的时序分析理论2本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面我们再来看一个例子,如图8.2所示

2015-07-14 11:06:10

基本时序路径本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 对于FPGA内部而言,通常有四大类的基本时序

2015-07-20 14:52:19

CMOS摄像头接口时序设计1理想时序(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s

2015-08-12 12:42:14

CMOS摄像头接口时序设计5时序报告(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s

2015-08-19 21:58:55

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

FPGA重要设计思想及工程应用之时序及同步设计希望对大家有用

2016-04-24 22:31:46

实战应用,这种快乐试试你就会懂的。话不多说,上货。 数字电路中的时序逻辑 在各种复杂的数字电路中,不但需要对二值信号进行算数运算和逻辑运算,还经常需要将这些信号和运算结果保存起来。为此,需要

2023-02-22 17:00:37

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

时序逻辑电路的设计实验1 进一步强化EDA仿真软件的使用;2 掌握利用MSI

2009-03-19 15:10:18

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

`Xilinx FPGA入门连载37:SRAM读写测试之时序解读特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 SRAM读写时序解读

2015-12-16 12:46:04

根据逻辑电路的不同特点,数字电路分为组合逻辑和时序逻辑,明德扬粉丝里的同学提出,无法正确区分,今天让我跟一起来学习一下两种逻辑的区别以及使用环境。·时序逻辑和组合逻辑的区别关于组合逻辑和时序逻辑

2020-03-01 19:50:27

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2019-08-11 08:30:00

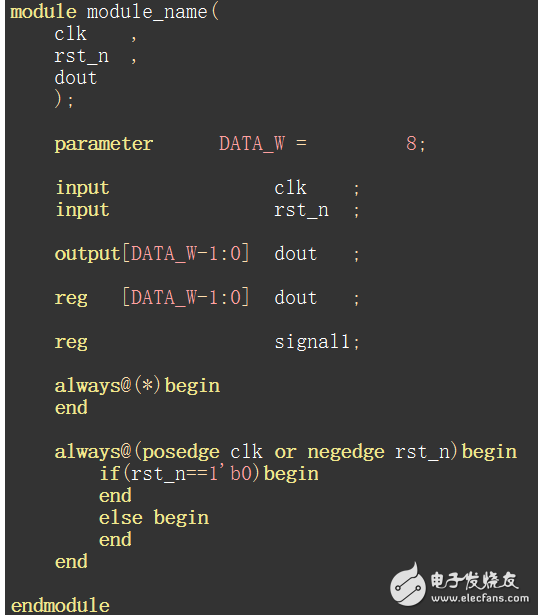

,就能使用这些模板了。1.时序逻辑的模板在GVIM输入“Module”并回车,如下图所示就能得到下面的时序逻辑的模板。模块的模板包括了输入输出信号列表、信号定义,组合逻辑和时序逻辑等,这是一个模块常用

2017-05-08 15:02:21

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

什么是时序逻辑?时序逻辑由哪几部分构成?

2021-09-17 07:43:37

```勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 数字电路按照逻辑

2017-11-17 18:47:44

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

涉及时序逻辑电路的实例,希望能够帮助大家理解在FPGA中实现时序逻辑电路。与组合逻辑电路相比,时序逻辑电路需要时钟的参与,电路中会有存储器件的参与,时序逻辑电路的输出不仅取决于这一时刻的输入,也受此

2022-07-22 15:25:03

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2021-05-18 15:55:00

了如何通过FPGA实现RS 232接口的时序逻辑设计。关键词:FPGA;时序电路;RS 232;串行通信

2019-06-19 07:42:37

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于FPGA内部的寄存器都有特殊的意义,不同的时钟周期执行不同的操作

2017-02-26 09:42:48

器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合

2018-04-03 11:19:08

输入“Shixu2”并回车就能得到带有2个if条件的时序逻辑代码。3.输入“Shixu3”并回车就能得到带有3个if条件的时序逻辑代码。欢迎关注明德扬公众号“fpga520”,或群97925396,索取明德扬模板。口号:多用模板,减少记忆,专注设计!

2017-04-26 16:08:40

,就能使用这些模板了。1.模块的模板在GVIM输入“Module”并回车,如下图所示就能得到下面的模块的模板。模块的模板包括了输入输出信号列表、信号定义,组合逻辑和时序逻辑等,这是一个模块常用的组件

2017-11-29 15:19:11

时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 中规模集成时序逻辑设计:计数器:在数字逻辑系统中,使用最多的时序电路要算计数器了。它是一种对输入脉冲信号进行计数的时序逻辑部件。9.1.1 计数器的分类1.按数制

2009-09-01 09:09:09 13

13 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 FPGA重要设计思想及工程应用之时序及同

在FPGA设计中最好的时钟方案 是: 由专用的全局时钟输入引脚 动单个 主时钟去控制设计项目中的每一个触发 器

2010-02-09 10:29:36 51

51 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 虚拟FPGA逻辑验证分析仪的设计

随着FPGA技术的广泛使用,越来越需要一台能够测试验证FPGA芯片中所下载电路逻辑时序是否正确的仪器。目前,虽然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 8146

8146

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1169

1169 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 FPGA重要设计思想及工程应用之时序及同步设计

2016-05-10 11:24:33 16

16 电子专业单片机相关知识学习教材资料之时序逻辑电路的分析与设计

2016-09-02 14:30:26 0

0 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2017-02-09 01:59:11 264

264 fpga时序收敛

2017-03-01 13:13:34 23

23 这是特权同学的关于fpga时序分析方面的极好资料

2017-08-28 11:19:14 20

20 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 控制器,在介绍控制器的逻辑结构的基础上,对FPGA与SDRAM间数据通信进行了时序分析,实现SDRAM 带有自动预充电突发读写和非自动预充电整页读写。

2017-11-18 12:42:03 2054

2054

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 8630

8630 的数量,可以用消耗的触发器和查找表的个数或者是等效逻辑门数来衡量;速度是指一个设计在FPGA上稳定运行时所能 达到的最高频率,由设计时序状态决定。 关于面积和速度的折衷,应在满足设计时序和工作频率要求的前提下,占用最小的芯片面积;或者在所规定

2017-11-25 03:57:01 802

802

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 123040

123040

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 106881

106881

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4150

4150

本文档的主要内容详细介绍的是数字电路基础教程之时序逻辑电路的详细资料概述。内容包括了:1.时序逻辑电路分析2.若干常用时序逻辑电路3.时序逻辑电路设计

2018-10-17 08:00:00 0

0 时序逻辑电路对于组合逻辑的毛刺具有容忍度,从而改善电路的时序特性。同时电路的更新由时钟控制。

2018-11-24 11:17:51 3197

3197

本文档的主要内容详细介绍的是数字电路教程之时序逻辑电路课件的详细资料免费下载主要内容包括了:一 概述,二 时序逻辑电路的分析方法,三 若干常用的时序逻辑电路,四 时序逻辑电路的设计方法,五 时序逻辑电路中的竞争冒险现象

2018-12-28 08:00:00 12

12 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 30485

30485 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 49628

49628 本文档的主要内容详细介绍的是FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明免费下载。

2019-03-27 10:56:04 20

20 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

2019-12-02 07:05:00 1522

1522

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:04:00 2191

2191

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37:00 2460

2460

本文档的主要内容详细介绍的是模拟电路教程之时序逻辑电路的课件资料免费下载包括了:1 概述,2 时序逻辑电路的分析方法,3 若干常用的时序逻辑电路,4 时序逻辑电路的设计方法。

2020-06-22 08:00:00 13

13 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 典型电路的模板1 模板代码1.1 输出时序逻辑的模板代码1.1.1 异步复位的时序电路(用的最多)1.1.2 同步复位的时序电路1.2 输出组合逻辑的模板代码1.3 输出整个模块部分代码1.4 输出

2021-12-22 18:57:03 4

4 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-02-12 10:28:36 771

771 时序逻辑的代码一般有两种: 同步复位的时序逻辑和异步复位的时序逻辑。在同步复位的时序逻辑中复位不是立即有效,而在时钟上升沿时复位才有效。 其代码结构如下:

2023-03-21 10:47:07 400

400 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 时序逻辑电路会复杂很多,强烈推荐mooc上华中科技大学的数字电路与逻辑设计,是我看过讲得最清楚的数电课。

2023-05-14 15:11:33 1693

1693

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 2539

2539

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30:43 247

247

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

FPGA高级时序综合教程

2023-08-07 16:07:55 3

3 时序逻辑电路 一 : 触发器 1:D 触发器 : 时序逻辑电路最小单元 。 (1):D 触发器工作原理 忽略清零端情况下 : 当使能条件 ( 往往为时钟的触发沿 : 上升沿 / 下降沿 ) 满足

2023-11-02 12:00:01 308

308

时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 499

499

![]()

![]()

![]()

![]()

![]()

电子发烧友App

电子发烧友App

评论