通常来讲,“一个好汉三个帮”,一个完整的嵌入式系统中由单独一个FPGA使用的情况较少。##系统架构确定,下一步就是FPGA与各组成器件之间互联的问题了。

2015-05-12 13:41:18 2836

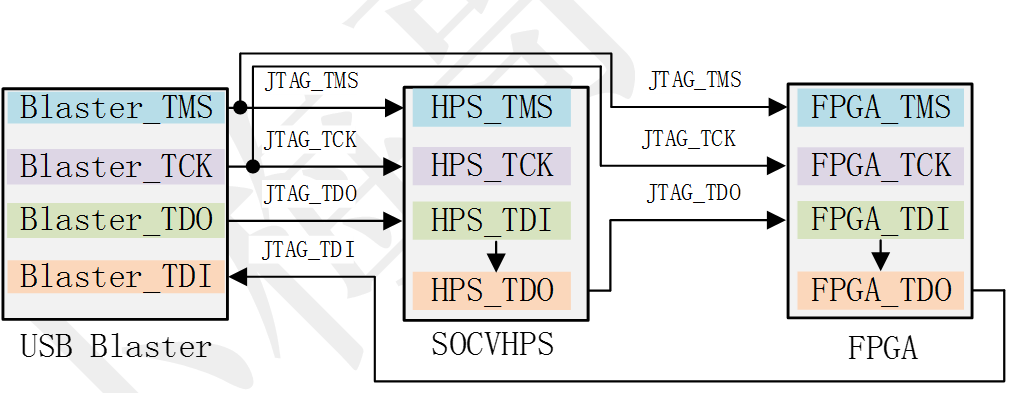

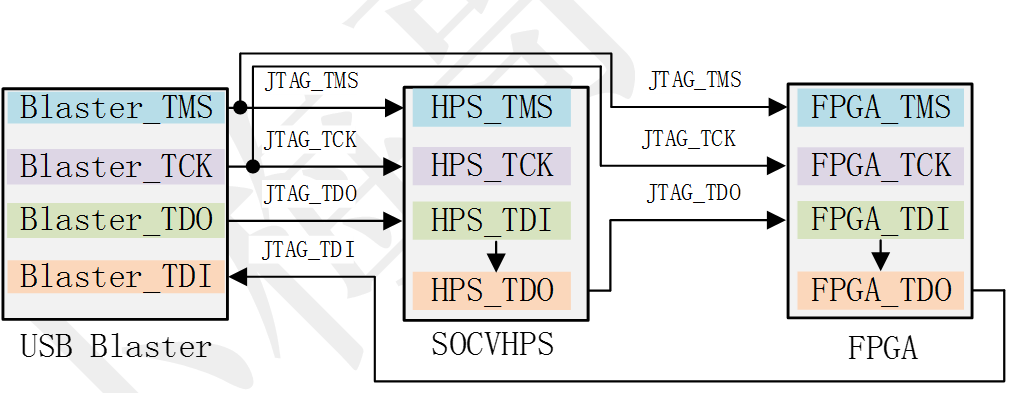

2836 SoC FPGA作为在同一芯片上同时集成了FPGA和HPS的芯片,其JTAG下载和调试电路相较于单独的FPGA或ARM处理器都有一些差异,但是同时两者又有紧密的联系。

2020-08-08 10:08:00 1633

1633

Kintex-7 FPGA的内部结构相比传统FPGA的内部结构嵌入了DSP48E1,PCIE,GTX,XADC,高速IO口等单元,大大提升了FPGA的性能。

2023-08-24 09:26:56 1393

1393

。 值得一提的是Altera SoC使用宽带干线互联,在HPS和FPGA架构之间的大吞吐量数据通路实现了双芯片解决方案无法提供的互联性能。HPS和FPGA架构的紧密集成提供了100-Gbps的峰值带宽,在处理器

2014-08-01 14:12:39

下面给大家介绍FPGA LUT的结构

2018-07-09 04:57:10

可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构

2021-04-02 06:03:40

(Flexible static memory controller)接口用于MCU与FPGA之间的通讯最近使用的一款MCU与FPGA之间通讯,FPGA模拟成NAND Flash作为Memory让MCU读写FPGA与MCU之间的连接方式如下所示上述信号定义如下这里可以看到,NAND flash访问是,Maste

2021-11-01 07:11:31

本帖最后由 rousong1989 于 2015-1-27 11:45 编辑

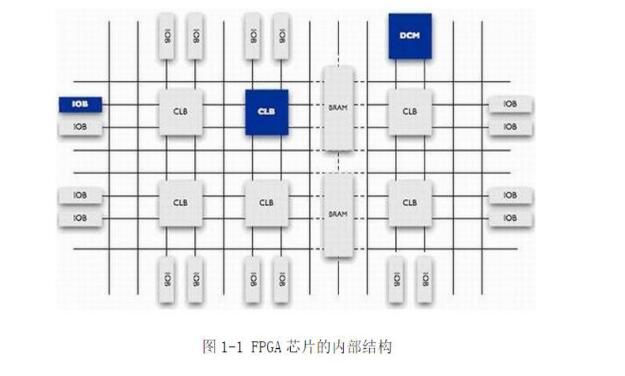

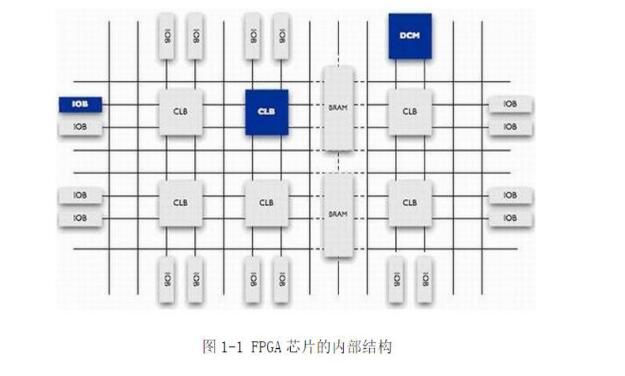

FPGA入门:内里本质探索——器件结构本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门

2015-01-27 11:43:10

可重构设计是指利用可重用的软、硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。FPGA器件可多次重复配置逻辑的特性使可重构系统成为可能,使系统兼具灵活、便捷、硬件资源可复用等性能

2011-05-27 10:22:36

,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌

2017-05-09 15:10:02

FPGA实现逻辑函数用的什么电路结构?

2017-01-01 21:49:23

FPGA的I/O结构的发展的怎么样了?

2021-04-29 06:12:52

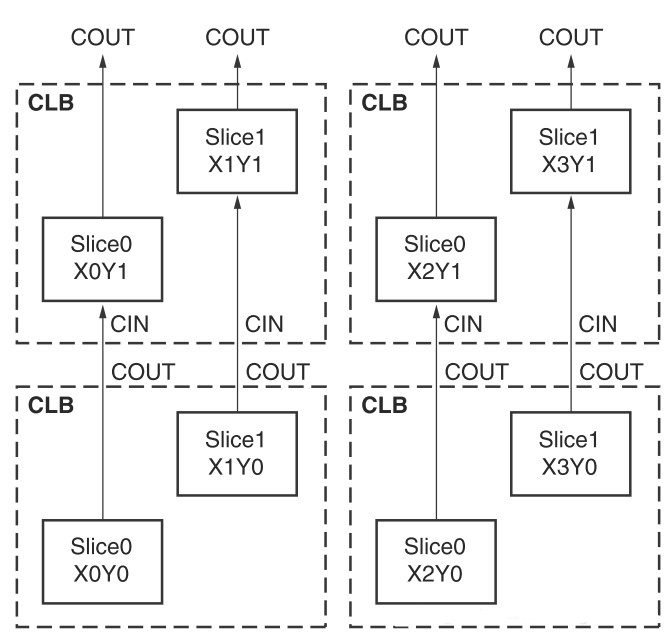

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-10-08 14:43:50

系统架构确定,下一步就是FPGA与各组成器件之间互联的问题了。通常来说,CPU和FPGA的互联接口,主要取决两个要素:(1)CPU所支持的接口。(2)交互的业务。通常来说,FPGA一般支持与CPU

2018-08-06 11:52:32

AD9674与AD9276的数据输出采用的是LVDS输出接口,现在准备用AD9674做一个超声波设备,但是数据采集方案一直没弄出来,看着英文文档实在老火啊,对FPGA也不太了解,现在是如何用FPGA采集出AD9674的数据呢,AD9674与FPGA之间如何连接?

2023-12-21 07:31:42

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2023-12-13 09:01:52

求大神帮忙解答下,altera soc 的HPS部分的引脚配置如何自动生成,怎么我改动了下qsys里面的HPS配置,怎么无法生成fitter location 来配置hps部分的引脚

2018-03-14 12:02:41

SoCFPGA器件在一个器件中同时集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA方法的优点。

2019-09-26 07:59:27

大家好,我现在在画一块28335的板子,想实现与FPGA之间的通信,但是不知道该怎样设计,包括FPGA与DSP连接的引脚、通过内部什么模块实现数据通信,现在一头雾水,请大家帮忙。谢谢。

2018-12-03 15:55:34

DSP和FPGA之间串口通信研究

2015-03-16 15:44:52

本帖最后由 mr.pengyongche 于 2013-4-30 03:24 编辑

通用微处理器具有良好的接口功能,便于构建可重构系统。按照MPU与FPGA之间的相互关系以及在系统中所起的作用,主要可以分为两类:MPU控制FPGA工作的可重构系统和MPU协同FPGA工作的可重构系统

2011-05-27 10:29:16

原谅我记忆力不好。。。花了好久弄明白的东西才十个小时不到就忘记了,所以趁现在记得赶紧记录下来。本文内容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

2018-07-03 08:10:25

件的能力。边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据。SoC FPGA作为在同一芯片上同时集成了FPGA和HPS的芯片,其JTAG下载和调试电路相较于单独

2020-02-25 18:40:45

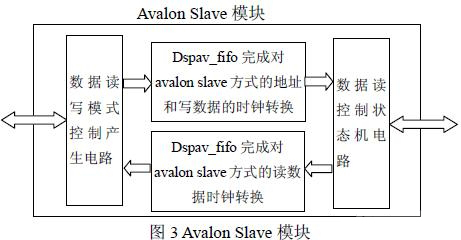

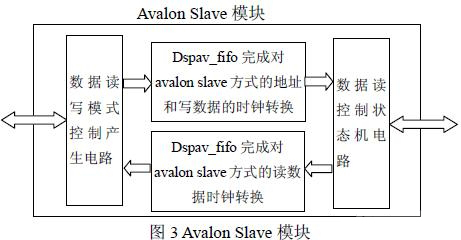

本文由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。Qsys系统和Linux应用程序之间通过一个名为hps_0.h的文件交互硬件信息,例如总线上添加

2020-02-16 18:41:59

\altera\hps\altera_hps\hwlib\include添加路径D:\intelFPGA\17.1\embedded\ip\altera\hps\altera_hps\hwlib

2020-02-16 18:38:28

两单板之间1000M网口之间对测,吞吐率只有300M,单板的连接结构博通61735-fpga-wan口,RGMII。

2017-09-18 18:03:59

由于Quartus®II15.0 Update 2及更早版本中的问题,用于将数据从HPS EMAC内核发送到FPGA内核的时钟缺少时钟分配。因此,这些HPS EMAC到FPGA路径将不会进行时序分析。

2018-07-27 14:27:56

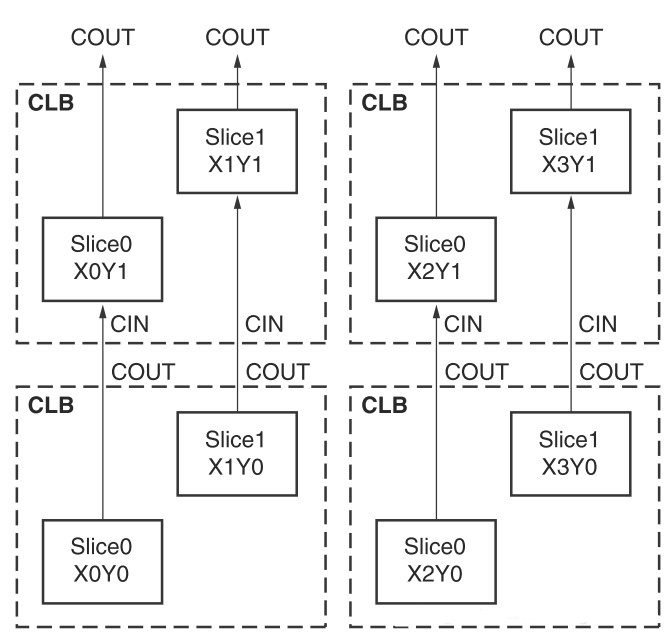

可预测性。这是由于FPGA是门级编程,并且CLB之间采用分布式互联,而CPLD是逻辑块级编程,并且其逻辑块之间的互联是集总式的。七,在编程方式上,CPLD主要是基于E2PROM或FLASH存储器编程

2009-10-05 16:32:12

SEED-HPS6678(HPS6678)是北京艾睿合众科技有限公司新推出的新一代高端DSP+FPGA应用方案。DSP采用TI公司首颗最高主频为10GHz的8核浮点DSP芯片TMS320C6678

2019-09-24 08:29:12

1 CHI的片上互联总线片上互联是将SoC内部不同模块连接起来的结构,如前文提到过的硬件系统结构中, Interconnect Bus就是片上互联。需要支持模块之间的高速数据传输,高效地互联

2022-06-29 16:28:32

会有可编程的互连线、LABs内部的各个LEs内部之间也会有可编程的互连线、I/O块与LABs之间、LABs与存储块以及乘法器之间都有着灵活可编程的互连线。图3.21 LAB互联结构 `

2017-11-21 22:28:24

如何在两个FPGA之间通过GPIO口进行通信,不要使用RS232或是RS485接口,可否I告诉技术方案

2013-11-19 10:50:34

)、离散余弦变换(DCT)、小波变换、数字滤波器(有限脉冲响应(FIR)、无限脉冲响应(IIR)和自适应滤波器)以及数字上下变频器。这些算法中,每一种都有一些结构性的元件可以用并行方法实现。而FPGA

2021-12-15 06:30:00

。以Altera的SoC为例, 简单的说,该产品(芯片)由CPU,FPGA,以及连接他们的互联部分(高速/轻量级)组成,如下图所示,这样的结构给开发需要同时用到CPU和FPGA产品提供了很大的便利。4.

2016-08-17 13:34:22

如何使用循环结构实现0~99之间所有偶数之和!

2016-04-15 22:33:55

”,而在SBBulkSourceSink固件中没有显示这个错误,可不可以证明我的FPGA和USB之间通信成功?另外,我该如何排查FPGA与USB之间的芯片通信问题?

2024-02-27 06:46:10

求arm和fpga之间SPI通信的源码

2014-12-09 16:46:23

各位大神请问FPGA和arm互联的硬件电路是怎么样的啊,我想做到高速的数据交换,需要注意什么,还有电路中的总线驱动器是必须的吗求原理图,网上原理讲很多,可是对我这种菜鸟不顶用

2022-04-28 10:16:13

));......reg [25:0] counter;regled_level;always @(posedge fpga_clk_50 or negedge hps_fpga_reset_n)beginif(~hps_fpga_reset_n)begin counter

2019-04-29 11:31:11

我们设计的系统里面需要实现DSP28377和ARM之间的高速互联,目前拟定的方案有双口RAM并行总线互联和SPI总线互联,请问还有其它高速总线互联方式吗?

2018-09-20 14:14:15

,有没有相关的资料 ?通过网络互联的话 phy 到phy 之间直接连接可不可以 ?就是不使用网络变压器互联?有没有其他的和FPGA 互联的方案以供参考 ?

2020-08-18 07:03:22

关于socfpga,还有个疑问: 1) 请问根据sopcinfo可以生成dts和dtb文件,而内核编译也会生成dts和dtb文件,请问有什么区别啊, 2)我用quartus13.1,工程编译后,有

2019-07-17 05:55:50

各位大神请问FPGA和arm互联的硬件电路是怎么样的啊,我想做到高速的数据交换,需要注意什么,还有电路中的总线驱动器是必须的吗求原理图,网上原理讲很多,可是对我这种菜鸟不顶用

2022-06-07 15:53:01

大家好好,请问大家有用过FPGA+arm的架构吗?本人现在做的一个项目就是关于FPGA+ARM用于视频处理方面,但是不知道ARM和FPGA之间具体怎么工作,或是ARM负责给FPGA发送什么指令

2022-06-02 09:52:32

首先介绍异步FIFO 的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法; 在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA 实现。

2009-04-16 09:25:29 46

46 本文讨论了一种可在FPGA 上实现的FFT 结构。该结构采用基于流水线结构和快速并行乘法器的蝶形处理器。乘法器采用改进的Booth 算法,简化了部分积符号扩展,使用Wallace 树结构和4-2

2009-09-11 15:46:40 16

16 The HPS3039 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co, ltd.Optimized Electrical design for 2-6W LED Application

2009-10-28 10:32:40 23

23 The HPS1014 series led driver is designed For Highvoltage led driver applicationOptimized Electrical design ,With active power factorcorection.

2009-11-07 11:41:26 16

16 The HPS1011 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-07 11:44:15 17

17 The HPS2007 series led driver is the new generation leddriver products of WeihawOptoelectronics Co

2009-11-07 11:48:18 19

19 The HPS1010 series is the new generation led driver products of Weihaw Optoelectronics Co

2009-11-10 14:38:40 19

19 The HPS2002 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-10 14:41:33 28

28 The HPS1011 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-10 14:43:12 13

13 The HPS1004 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-10 14:46:37 20

20 HPS1007X HIGH PERFORMANCE LED POWER SUPPLY

Wide input & output voltage

2010-04-19 15:31:02 13

13 系统(HPS)来评估SoC的特性及性能。Intel Agilex® F系列FPGA开发套件提供了一个完整的设计环境,其中包括采用PCI Express(PCIe)

2024-02-27 11:51:58

基于FPGA实现DSP与RapidIO网络互联

1. 引言

随着通讯系统的数据处理量日益增大,过去总线形式的体系结构逐渐成为约束处理能力进一步提升的瓶颈。本文首

2010-02-25 16:46:46 868

868

高级FPGA设计结构

2011-01-10 10:36:50 293

293 本文介绍了这种基于SRIO互联技术的高速实时数据处理硬件平台,并在该平台上研究了多DSP之间、DSP与FPGA之间的SRIO通信技术。

2012-01-10 15:07:55 3562

3562

SoC FPGA使用宽带互联干线链接,在FPGA架构中集成了基于ARM的硬核处理器系统(HPS),包括处理器、外设和存储器接口。Cyclone V SoC FPGA在一个基于ARM的用户可定制芯片系统(SoC)中集成了

2012-09-04 14:18:14 4604

4604

我经常收到关于各类设备之间的差异的问题,诸如ASIC、ASSP、SoC和FPGA之间的区别问题。例如是SoC是ASIC吗?或ASIC是SoC吗?ASIC和ASSP之间的区别是什么?以及高端FPGA应该归类为SoC吗?

2014-07-17 09:42:39 42262

42262 异步FIFO结构及FPGA设计,解决亚稳态的问题

2015-11-10 15:21:37 4

4 高级FPGA设计 结构、实现和优化,适合于FPGA的进阶学习。

2016-05-11 16:40:55 15

15 高级FPGA设计 结构、实现和优化,适合于学习FPGA的进阶学习。

2016-05-11 16:40:55 14

14 引入IP核的三维FPGA结构研

2017-01-07 20:32:20 2

2 DSP与FPGA高速的数据传输有三种常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 现场可编程逻辑门阵列) 设计 FIFO的接口电路,即可实现高速互联。

2017-02-11 14:16:10 2487

2487

HPS型顶导向高压单座调节阀是为高温、高压工况而设计的。阀体结构紧凑,流体通道呈S 流线型,压降损失小,允许流通能力大,可调范围广。阀芯导向部分的导向面积大,具有抗振性能强的特点。阀座关闭性能符合

2017-09-25 11:17:59 8

8 SoC使用宽带互联干线链接,在FPGA架构中集成了基于ARM的硬核处理器系统(HPS),包括双核ARM。处理器、外设和存储器控制器。

2018-03-22 13:34:21 7

7 本文首先分析了FPGA是否会取代DSP,其次介绍了FPAG结构特点与优势及DSP的基本结构和特征,最后阐述了FPGA与DSP两者之间的区别。

2018-05-31 09:51:25 35711

35711

如何在预加载器中调试HPS SDRAM

2018-06-20 00:44:00 3023

3023

霍尼韦尔过程控制部 (HPS) 近日发布一款新型天然气计量解决方案,为运营、维护和管理团队提供简单易用的中游计量系统状态监控功能。霍尼韦尔互联工厂天然气计量IQ解决方案有助于提高计量的可靠性和安全性,同时大幅减少现场检修需求,从而削减运营成本。

2018-07-09 10:55:00 2030

2030 小梅哥最新款FPGA_SOC

2019-09-02 06:02:00 2139

2139

目前市场上90%以上的FPGA来自于xilinx和altera这两家巨头,而这两家FPGA的实现技术都是基于SRAM的可编程技术,FPGA内部结构基本一致,所以本文仅以xilinx的7系列FPGA介绍。

2019-10-20 09:03:00 2380

2380

电子技术行业里面的攻城师们应该对ASIC、FPGA和单片机这些名字都不陌生,但我相信并不是所有人都清楚ASIC和FPGA之间的区别和关系,下面我们分几个方面去理清一下他们之间的瓜葛纠纷吧!

2020-06-04 11:36:11 5697

5697 对于FPGA的学习者而言,怎样学习FPGA是大家争论不断的。有的认为要先学习语言,也就是HDL硬件描述语言;也有的说要先学习数电、模电,没有这些知识,就算学会了语言,以后的学习也会非常艰难。但是唯一大家都认可的是掌握FPGA的基本结构。

2020-06-01 09:07:18 12050

12050 简单介绍了FPGA器件的发展及基本结构、设计方法,并以PWM电路的FPGA实现为例,说明了FPGA在电力系统中的应用前景.

2020-10-20 16:16:50 11

11 1.项目需求 FPGA :V7-690T两片 Resource:两片FPGA通过X12 gth互联;每片FPGA使用48路serdes走光口与板外连接;每片FPGA使用SIROx4通过VPX与外界

2021-01-07 10:15:31 4645

4645

1、两块fpga 之间采用12 根线连接,包括8 根数据线, 2 根同步时钟线, 2 根使能信号线。

2021-02-25 09:58:00 44

44 最近完成了Arria10的原理图设计,想做一些记录,下面是关于FPGA配置的一些方式。 MSEL 将 MSEL 管脚直接连接到VCCPGM 或 GND,不需使用任何的上拉或下拉电阻,即可选择出所需

2021-03-12 16:26:58 11307

11307

两块fpga之间采用12根线连接,包括8根数据线,2根同步时钟线,2根使能信号线。

2021-04-27 09:35:16 13

13 FPGA各存储器之间的关系(嵌入式开发工作怎么样)-该文档为FPGA各存储器之间的关系总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 16:35:09 6

6 根据国际电信联盟(ITU)的定义,物联网主要解决物品与物品,人与物品,人与人之间的互联。因为互联网并没有考虑到对于任何物品连接的问题,所以我们就使用物联网来解决传统意义上的问题。

2021-09-21 17:17:00 8263

8263 设计属硬件范畴,它的硬件(FPGA)是可编程的,是一个通过硬件描述语言在FPGA芯片上自定义集成电路的过程;二者最大的区别:单片机(无论哈佛总线结构或者冯诺依曼结构)均为取出指令->执行,指令是顺序执行的(即使是中断,其发生后的中断服务程序也

2021-11-15 16:51:06 24

24 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 系统架构确定,下一步就是FPGA与各组成器件之间互联的问题了。通常来说,CPU和FPGA的互联接口,主要取决两个要素。

2022-10-08 11:37:08 1749

1749 全新英特尔 Agilex D 系列 FPGA 和 SoC 具备多项新特性,例如升级版硬核处理器系统 (HPS)、采用 AI 张量模块的增强型数字信号处理 (DSP)、MIPI I/O 支持和固核 IP 时间敏感网络 (TSN) 控制器。

2022-11-23 15:23:35 507

507

电子发烧友App

电子发烧友App

评论