随着现代通信技术的发展,各种多址技术在日常生活中的应用正变得越来越广泛。所谓多址技术,是指许多用户同时使用同一频谱,采用不同的处理技术,使不同用户信号之间互不干扰地被分别接收和解调。多址技术分为频分多址(FDMA)、码分多址(CDMA)、时分多址(TDM-A)。频分多址是以不同的频率信道实现通信,码分多址是以不同的代码序列实现通信,而时分多址是以不同的时隙实现通信,它是一种实现共享传输介质或网络的通行技术。

时分多址技术把时间分割成周期性的帧,每一帧再分割成若干个时隙,通过介质或者网络发送信号。在满足定时和同步的条件下,接收方可以分别在各个时隙中接收到对应的信号而不混扰。时分多址技术具有保密性较高,传输容量较大等特点。

目前,利用FPGA实现多路信号的时分多址帧格式来进行传输的方法众多,但大多数方法都是通过使用FPGA芯片大量的门电路构成寄存器来实现时分多址。该类方法将占用大量的FIGA资源,导致单片FPGA可实现的功能大大减少,提高了工程成本,甚至对于一些资源较少的FPGA芯片,该类方法无法实现时分多址传输。本文提出了一种基于IP核的方法来实现时分多址,利用芯片内部的Block SelectRAMResource(BRAM)存储数据,节约了大量的逻辑门资源,使单片FPGA芯片能完成更多的逻辑功能。

1 理论分析

1.1 IP核

IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,该程序与集成电路的工艺无关,可以移植到不同的半导体工艺中去生产基础电路芯片。利用IP核设计电子系统,引用方便,修改基本元件的功能容易。IP核模块有行为(Behavior)、结构(Str-ucture)和物理(Physical)3级不同程度的设计,对应描述功能行为的不同分为3类,即软核、完成结构描述的固核和基于描述并经过工艺验证的硬核。

1.2 BRAM(Block SeleetRAM Resource)

FPGA内部的资源种类比较复杂,主要包括了以下几个部分:输入/输出模块(Input/Output Blocks,IOB)、可配置逻辑单元(Configur-able Logic Blocks,CLB)、Block SelectRAM、乘法器、数字时钟管理单元(DCM)、布线资源(Routing Resources)等。本文提出的算法正是利用芯片内部集成的Block SelectRAM实现时分多址方式的传输,从而节约出大量的CLB.以便单片FPGA能完成更多的功能。

FPGA芯片内部集成的每一块BRAM都是物理上的双口随机访问存储器(双口RAM),它有两套完全独立的数据线,地址线和读写控制线,并允许两个独立的系统同时对该存储器进行随机性的访问,即共享式多端口存储器。

双口RAM最大的特点是存储数据共享。一个存储器配备两套独立的地址,数据和控制线,允许两个独立控制器同时异步的访问存储单元。因为数据共享,就必须存在访问仲裁控制。内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配;信令交换逻辑等。

BRAM的工作类似于寄存器的工作方式,控制信号、地址信号以及输入输出数据信号必须要在时钟沿的建立时间内保持有效,BRAM会在这个时钟周期进行读写操作来输出结果或写入数据。其读写方式分为3种,分别是对地址进行读和写、只读、只写。

1.3 算法实现

第1步,例化双口RAM的IP核,将程序的输入输出与双口RAM的输入输出进行映射。

第2步,通过双口RAM的第一套端口将输入信号存储到RAM中,通过双口RAM的第二套端口将存储到RAM中的数据读出。

以4路信号为例,假设每路输入信号的采样率是48 kHz,采样位数是64 bit,则每路输入信号的位时钟是3.072 MHz,在第一个48 kHz的采样周期内,当采到3.072 MHz位时钟的下降沿时,将输入地址递增1。则在接下来的位时钟的上升沿,根据所例化的双口RAM的IP核,4路输入数据将存储到双口RAM当前输入地址所对应的存储器地址中,等待读取。由于共有4路信号,即输入信号宽度为4位,则存储到双口RAM中的数据宽度也应为4位,其中,每个地址中的所存储数据的第一位对应第一路输入信号,第二位对应第二路输入信号,以此类推。此时需要的双口RAM的大小位64x4 bit。

在下一个48 kHz的周期内,与前面类似,将4位宽度的输入数据继续存储到双口RAM新的64个4位的存储空间,同时,应将上个48 kHz周期所存储的前64个4位数据读出,并且准备以时分多址的格式传输出去。

第3步,将从第二套端口读出的数据以时分多址的帧格式传输出去。

要想4路输入信号以时分多址的格式传输,应该将48 kHz时间周期划分为4个时间周期,在划分的每一个时间周期内,读取一遍双口RAM中存储的数据。首先,应在划分的第一个时间周期内把读出的64个4位数据的第一位送给时分多址的输出,然后回到起始地址,在划分的第二个时间周期内再重新读出一次64个4位数据,把数据的第二位送给时分多址的输出,以此类推,直到4路数据全部输出。由于在一个48 kHz周期内要重复读取双口RAM中的数据4次,所以此时位时钟的频率要提高到原来的4倍,因此,读取数据的位时钟频率应该为12.288 MHz。

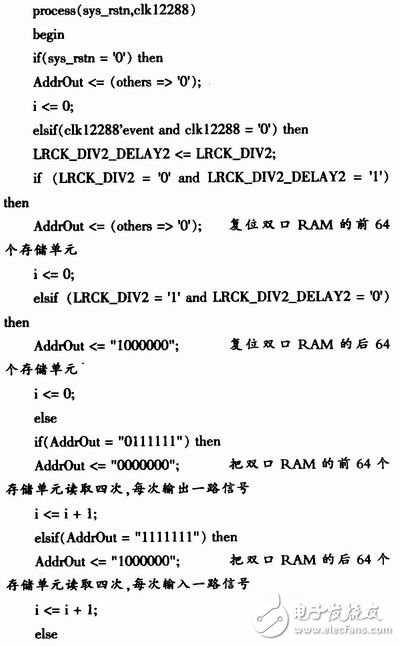

在接下来的一个48 kHz周期内,将双口RAM中后64个4位存储空间内的数据以与上面相同的方式发送出去,同时,由于前64个4位的存储空间的数据已经发送完成,不再需要保存,则新输入的数据可被存储到前64个4位的存储空间,以此类推,前64个4位存储空间与后64个存储空间交替存储输入数据,并交替将存储的数据发送出去。

由此可以看到,所需要双口RAM的大小应为2x64×4bit,在A端口对数据写入,在B端口对数据进行读出。

2 FPGA的实现

实验所采用的FPGA是XILINX公司的SPARTAN 3E系列中的XC3SS00E芯片,该芯片的封装是PQ208,芯片速度为-5,采用的程序开发语言是VHDL,综合工具为XILINX公司的ISE 10.1,仿真工具采用的是ModelSim se 6.2。

与理论算法对应,硬件实现的VHDL程序包括了以下几个模块。

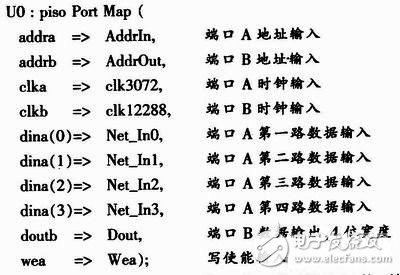

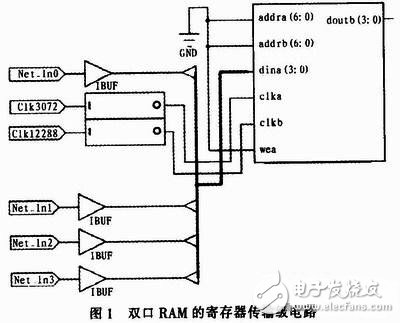

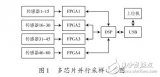

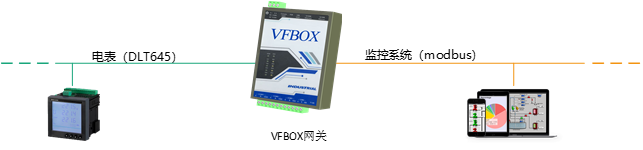

使用芯片内部的双口RAM的IP核,通过例化IP核,利用一个双口RAM有两套读写地址,将程序的输入输出与双口RAM的输入输出进行映射,则内部电路将程序的输入输出连接到了双口RAM的输入输出上。对程序的输入输出脚的操作相当于对双口RAM进行操作。图1是双口RAM的VHDL代码在Xilinx ISE中综合后的寄存器传输级电路图。

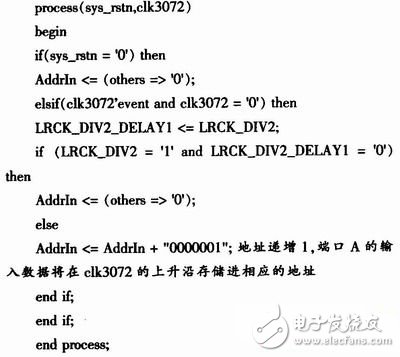

在端口A输入时钟clk3072的每个下降沿,端口A输入地址AddrIn都递增1,则在elk3072的上升沿,根据例化的双口RAM的IP核,端口A的四路输入数据将存储进相应的地址空间中。

在端口B输入时钟elk12288的每个下降沿,端口B输入地址AddrOut都递增1,则在elk12288的上升沿,根据例化的双口RAM的IP核,相应的地址空间中的数据将通过Dout被读出来。

依次将输出数据以时分多址的帧格式传输出去。

3 仿真结果

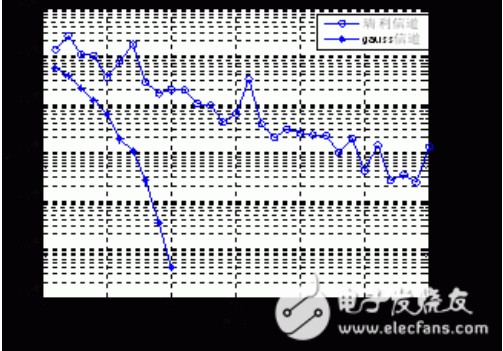

用ModelSim se 6.2b对程序进行仿真,在48 kHz的时钟周期内,给第1路输入源的64位输入信号为0x1111111111111111,第2路输入源的64位输入信号为0x2222222222222222,第3路输入源的64位输入信号为0x3333333333333333,第4路输入源的64位输入信号为0x4444444444 444444。仿真结果如图2所示。

由仿真图可以看出,在一个48 kHz的时钟周期内,TDMA_OUT,即时分多址帧格式的输出为0x11111111111111112222222222222222333333 33333333334444444444444444,即每一帧被分成了4个时隙,4路输入信号在每一帧中占用各自的时隙进行传输,通过该仿真结果,可以验证该方法的可用性。

将VHDL语言程序通过ISE10.1综合,布局布线后,通过JTAG线缆下载到XC3S500E中进行电路板上的测试,再次验证了该方法的正确。

通过ISE综合后,可以看到程序所占用的芯片资源如下表所示。

从表中的数据可以看出,通过使用一个BRAM从而节约了大量的资源,FPGA芯片资源的重要指标Slices仅仅占用了15个,LUTs仅仅用了29个,可见,该方法所占用的FPGA资源极少,达到了设计目标。

4 结论

本文研究了FPGA实现时分多址的一种改进型的方法,通过使用FPGA芯片内部的双口RAM,利用IP核,实现了多路信号转换成时分多址帧格式信号进行传输,根据所占资源的统计数据,可以看到在完成相同功能的前提下,该方法相比于已有的方法,确实能大量节省FPGA芯片的逻辑资源,从而使单片FPGA能完成更多的逻辑功能。但是,此方法会占用一部分双口RAM,在双口RAM资源紧张的时候不是太适用。

用ModelSim SE 6.2b对FPGA程序进行了仿真,并且将程序下载到电路板上进行了验证,证实了该方法的可用性。

电子发烧友App

电子发烧友App

评论