IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

你好,我在使用Xilinx网站的IP核时遇到了一些问题。我已经下载了Vivado Webpack,也为此同时下载了IP-Core的许可证。Vivado Webpack工作正常,但我看不到我下载

2018-12-24 13:50:01

XILINX ISE 14.7,我想建立一个工程,里面要调用之前别人的包含SRAM IP核的模块,需要使用.v和.ngc文件,可是不知道那个.ngc文件该怎么使用,是copy到自己工程目录然后在工程里面添加进去吗?为什么加进去后我的工程文件层次就乱了。。。

2015-04-18 14:21:49

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

用的xilinx的FFT 9.1版本的ip核 , 仿真出来的结果和我MATLAB算出来的结果差的很多,也没有倍数关系,scaled因数改了好几次,没有溢出,波形大致相同,但是数值上差的太多,已经弄了快两周了,求做过这个的讲讲经验。

2018-07-10 16:16:31

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

xilinx dds IP核输出能不能改为无符号数,因为一般DA转化器只能转化正数

2015-09-29 18:30:23

的模拟信号,通过选择不同的频率成分来实现信号滤波。滤波器是一种电路,它只允许一定频率范围内的信号成分正常通过,而阻止另一部分频率成分通过的电路,也叫做经典滤波器或滤波电路。实际上,任何一个电子系统都具有

2019-06-28 04:20:07

本人在做电磁兼容试验时,临时搭配的滤波器,临时搭配滤波器没有外壳,将滤波器放在电源处,CE102效果很好,但是将滤波器放在客户产品机壳内,滤波器感觉没有效果,CE102过不了,跟不放效果一样,请问怎么回事?

2017-12-31 20:32:29

滤波器如何延缓信号?如何设计一款可预测的滤波器?

2021-04-06 09:39:32

什么是滤波器?滤波器分类分类和作用1.滤波器工程上根据输出端口对信号频率范围的要求,设计专门的网络,置于输入—输出端口之间,使输出端口所需要的频率分量能够顺利通过,而抑制或削弱不需要的频率分量,这种

2017-04-22 21:49:23

一、从功能上分;低、带、高、带阻。 二、从实现方法上分:FIR、IIR。 三、按元件分类:滤波器可分为:有源滤波器、无源滤波器、陶瓷滤波器、晶体滤波器、机械滤波器、锁相环滤波器

2020-06-24 16:06:54

求:RC滤波器,LC滤波器设计,椭圆低通滤波器设计资料???1106765606@qq.com

2013-08-18 19:51:23

AD9854官方设计的滤波器将50ohm电阻并联在滤波器输入端,而滤波器设计软件一般都是滤波器输入串联电50ohm电阻,输出并联50ohm电阻负载,请问二者有什么区别?

2015-12-11 21:45:55

BRAM IP核包括哪几种类型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

请问C滤波器和RC滤波器在特性和用途上有什么区别吗?IC的电源管处只用C来滤波。但在很多单片机的AD输入管脚和传感器的输出管脚,有时候会只用C,而有时候也会用RC来滤波。查了产品手册并无特殊的滤波要求,请问为什么会使用这两种不同的滤波器。感谢各位大侠赐教!

2015-06-18 11:35:37

我在用fir 核做半带插值滤波器时,自己写好tb后,直接用quartus ii 调用modelsim仿真时,出错,提示说找不到auk_dspip_lib 库怎么解决呀,谢谢大家

2017-11-24 19:28:15

滤波器使用的比较多。 6、相较于IIR滤波器, FIR滤波器有以下的优点: (1) 可以很容易地设计线性相位的滤波器,线性相位滤波器延时输入信号,却并不扭曲其相位,实现简单, 在大多数DSP处理器

2011-09-24 16:05:53

。iir滤波器运算结构通常由延时、乘以系数和相加等基本运算组成,可以组合成直接型、正准型、级联型、并联型四种结构形式,都具有反馈回路。由于运算中的舍入处理,使误差不断累积,有时会产生微弱的寄生振荡。3

2018-03-12 13:21:07

的线性相位滤波器IIR滤波器有以下几个特点:1、IIR数字滤波器的系统函数可以写成封闭函数的形式。2、IIR数字滤波器采用递归型结构,即结构上带有反馈环路。IIR滤波器运算结构通常由延时、乘以系数

2016-08-08 08:49:32

第一个问题的基础上,我是设置unsigned还是signed?3、滤波器的设计,我要给他什么样子的输入,仿真看得出什么样子的结果?部分代码如下

2017-05-09 14:18:17

刚接触FPGA,想用EP4CE6F17C8这个型号的altera芯片实现低通滤波器设计,我看能直接调用IP实现,但是网上的资料都是调用MATLAB生成滤波器所需的系数,还只是用于仿真,但是我想用

2017-08-04 19:25:28

形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。所谓串行结构,即串行实现滤波器的累加运算,将每级延时

2017-08-02 17:35:24

RC滤波器和LC滤波器的区别

2020-12-23 07:34:04

RT所示,这两个数字滤波器怎么使用呢?目前想滤掉5khz后面的波形进行处理,这两个滤波器应该怎么操作最好呢?

2018-08-20 07:12:59

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

最近在使用altera的FIR IP核做半带滤波器,quartus ii软件也破解了,firIP核也破解了,modelsin仿真也通过了,但是下载不了.sof文件到开发板,大家有用FIR IP核成功实现下板的经验吗,求大神指点呀。谢谢!

2018-05-11 16:01:15

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

。本文研究了一种16阶FIR滤波器的FPGA设计方法,采用Verilog HDI语言描述设计文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平台上进行了实验仿真及时序分析,并探讨了实际工程中硬件资源利用率及运算速度等问题。

2012-08-11 18:27:41

testbench进行仿真分析,预计第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。这的图发不出来。1. 添加DDS的IP核(1) 新建一个原理图文件,添加DDS的IP。(2) DDS

2020-01-18 22:05:50

请教各位大师,quartus ii 中调用fir数字滤波器IP核,可不知道如何设置参数,比如如何设置滤波器的系数

2013-11-23 20:54:41

本人想使用一个verilog低通滤波器,IPCore设置好了,在程序中怎么实例化,第一次使用低通滤波器,不知道怎么实例化,书上锁相环实例化有例子我会实例化,书上没有滤波器例子,怎么实例化。或者说

2017-05-17 21:57:11

的主要性能指标7.2 离散傅里叶变换基础7.2.1 离散傅里叶变换7.2.2 频域应用7.2.3 FFT/IFFT IP Core的使用7.3 XtremeDSP模块功能介绍7.4 乘累加结构的FIR滤波器

2012-04-24 09:23:33

除了在Xilinx官网上在哪里能下载到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

实现技术,以此为参考,来评估现有的各种实现技术的优劣。RC有源滤波器是由时不变电阻、电容和有源器件组成,根据这个定义,它是不包含电感器的,这样是可以避免电感庞大笨重的外形,以及相关的磁场和非线性行为。即便是综合问题,考虑电感器的绕组的电阻和核损,网络设计也会因此变的复杂。

2019-04-23 12:14:50

通过数字滤波器可以获得很窄的带宽。和模拟滤波器相比,理想的高斯滤波器可以实 现。数字滤波器在可接受的价格内有更好的选择性,如5级电路模拟滤波器的形状因 子为10,高斯滤波器为4.6。另外,数字滤波器

2017-10-13 09:22:59

FIR滤波器如何定义?为什么要使用FIR滤波器?

2021-04-06 07:48:45

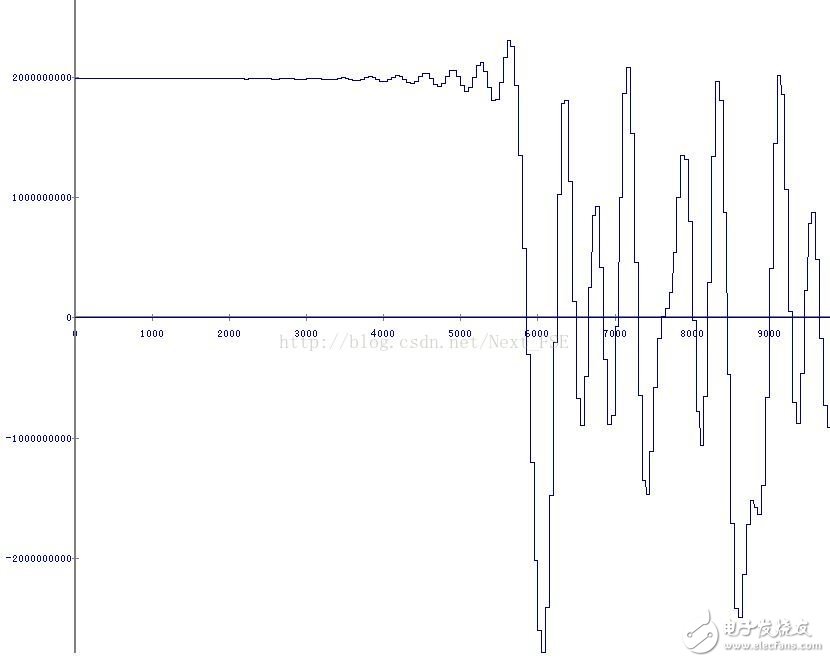

新手见谅使用IP核设计了一个10阶3级的CIC滤波器,输入数据位宽12位,输出最大22位但是仿真出来的结果有种溢出的感觉,想不通是怎么回事,求各位前辈帮忙分析~~贴出来IP核设置界面,还有matlab处理的结果{:4_108:}

2013-10-13 16:56:12

我们使用quartusII的fir ip核生成了一个滤波器,用AD采集了单频正弦信号输入,可是不管输入频率多少,滤波器的输出端口都没有输出,不知道这是为什么啊?

2013-08-12 22:49:58

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

有找到关于添加IP的文章A simple BBP for RF Transceivers [Analog Devices Wiki] 我想直接使用Xilinx的IP核,但是vivado建立的IP核

2018-08-13 08:03:00

最近在做一个FIR低通滤波器,利用Matlab 产生滤波系数,导入到Quartus中,再利用其中的FIR IP核进行滤波器设计,在采用分布式全并行结构时,Modelsim 仿真有输出;如果改为分布式

2018-07-05 08:33:02

各位大佬,xilinx ip核的各个参数的含义从哪里看啊

2021-05-30 10:37:27

各位牛人,xilinx Blockset能做A计权滤波器吗?

2013-03-12 14:54:22

Programmable Gate Array,现场可编程门阵列)基于查找表的结构和全硬件并行执行的特性,如何用FPGA 来实现高速FIR 数字滤波器成了近年来数字信号处理领域研究的热点。目前,全球两大PLD 器件供应商都提供了加速FPGA 开发的IP(IntelligentProperty,知识产权)核。

2019-09-05 07:21:15

基于FPGA的FIR滤波器IP仿真实例 AT7_Xilinx开发板(USB3.0+LVDS)资料共享 腾讯链接:https://share.weiyun.com/5GQyKKc 百度网盘链接

2019-07-16 17:24:22

和ip-iq检测方式[1].本文利用软件建立了基于这两种方法的并联有源电力滤波器模型,并进行了谐波分析.在图1中,有源电力滤波器输入交流电流ic抵消交流电源中电流is的谐波含量,交流电流is是负载电流iL和全文下载

2010-04-24 09:03:00

我正在尝试将Xilinx MIG IP Core从1.7版升级到1.9版。 Coregen UI左侧有一个方便的“升级IP核”按钮,但它显示为灰色。我需要做什么才能进行IP核升级?我在Kintex

2019-11-04 09:26:19

Xilinx 官方提供的技术参数来实现对 IP 核的写控制。写命令和写数据总线介绍DDR3 SDRAM控制器IP

2022-02-08 07:08:01

本文将简单介绍FIR滤波器的原理,详细介绍使用Verilog HDL设计并行FIR滤波器的流程和方法。接下来几篇会介绍串行结构FIR的Verilog设计、使用Quartus和Vivado的IP核

2020-09-25 17:44:38

微波滤波器的分类方法很多,根据通频带的不同,微波滤波器可分为低通、带通、带阻、高通滤波器;按滤波器的插入衰减地频响特性可分为最平坦型和等波纹型;根据工作频带的宽窄可分为窄带和宽带滤波器;按滤波器

2019-11-04 09:10:14

怎么区别交流滤波器与直流滤波器

2015-07-27 00:03:06

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-23 06:39:46

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-27 07:16:54

DSP系统中不常用,Quartus和Vivado都没有提供相关的IP核,因此只能自己进行Verilog设计。本文设计参考自杜勇老师的《数字滤波器的MATLAB与FPGA实现》。本设计将在Vivado环境

2020-09-27 09:22:58

相关滤波器、数字滤波器和虚拟滤波器三者的含义,区别,联系真的是菜鸟一枚啊,求大神帮助

2015-10-14 20:01:46

你好,有可能设计一个带50滤波器的带阻滤波器在PSoC上使用滤波器块吗?我试过,但实际上不起作用…谢谢。当做,罗米拉。

2019-09-20 06:41:29

; 数字滤波器由数字乘法器、加法器和延时单元组成的一种算法或装置。数字滤波器的功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。数字滤波器可用计算机软件实现,也

2010-05-10 21:04:02

本帖最后由 86xue 于 2011-10-17 11:46 编辑

1.输入正弦波,用模拟滤波器滤除高频信号,发现有相位延迟,怎样才能补偿掉?2.输入不同频率,延时还不同,所以补偿方法还要针对不同频率都不要有延迟。求解答

2011-10-17 11:46:13

什么是奈奎斯特定理?什么是模拟低通滤波器?什么是数字有限脉冲响应 (FIR) 滤波器?模拟低通滤波器和数字有限脉冲响应滤波器有何不同?

2021-07-29 07:27:13

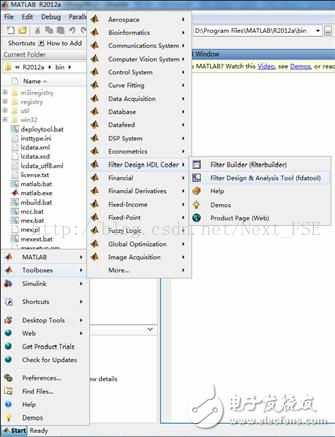

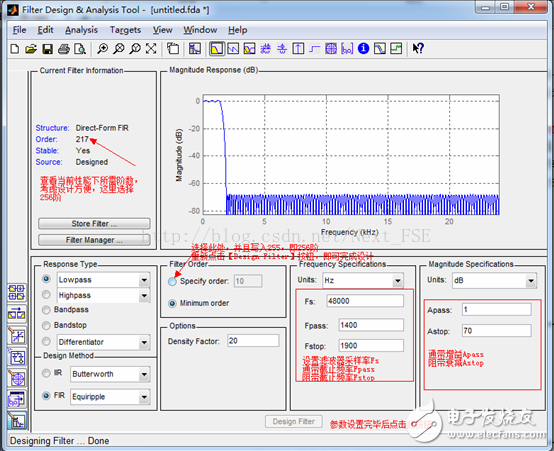

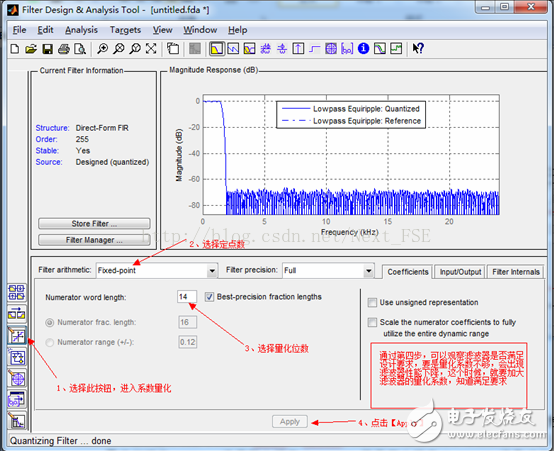

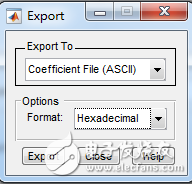

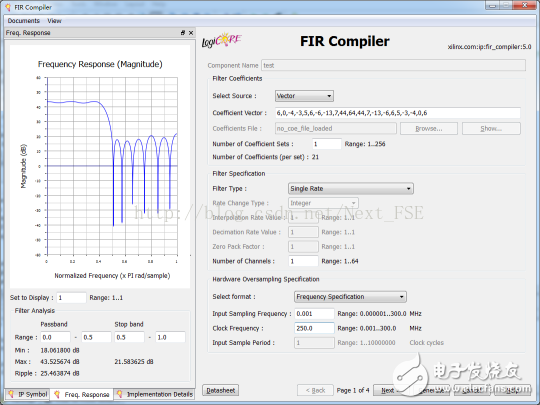

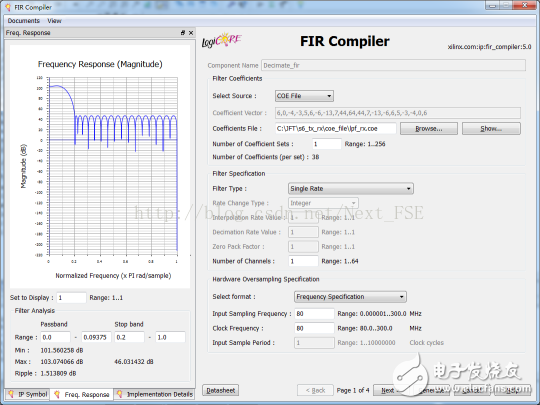

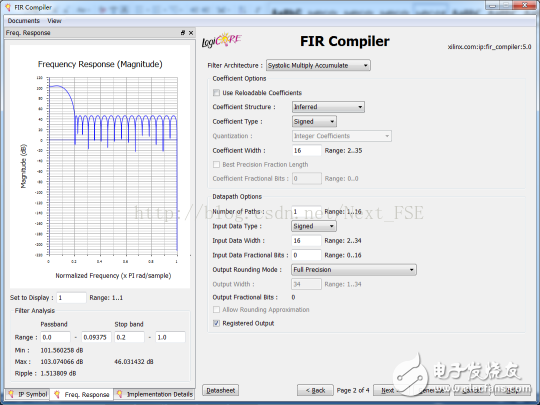

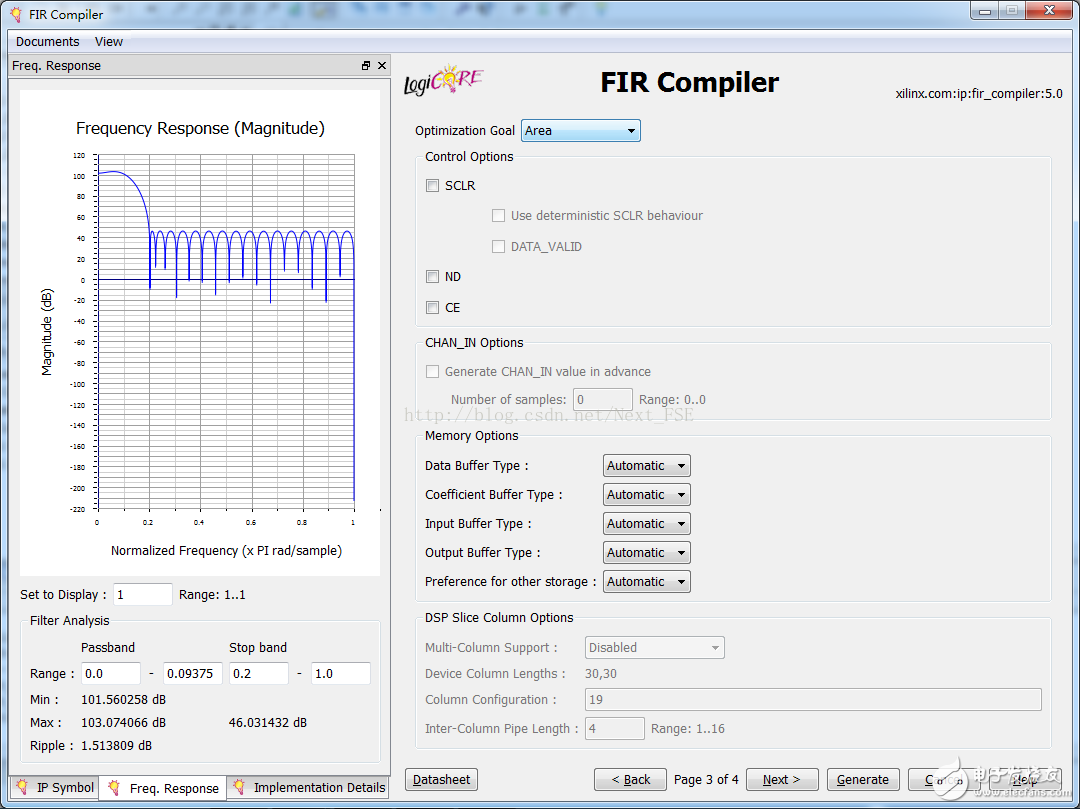

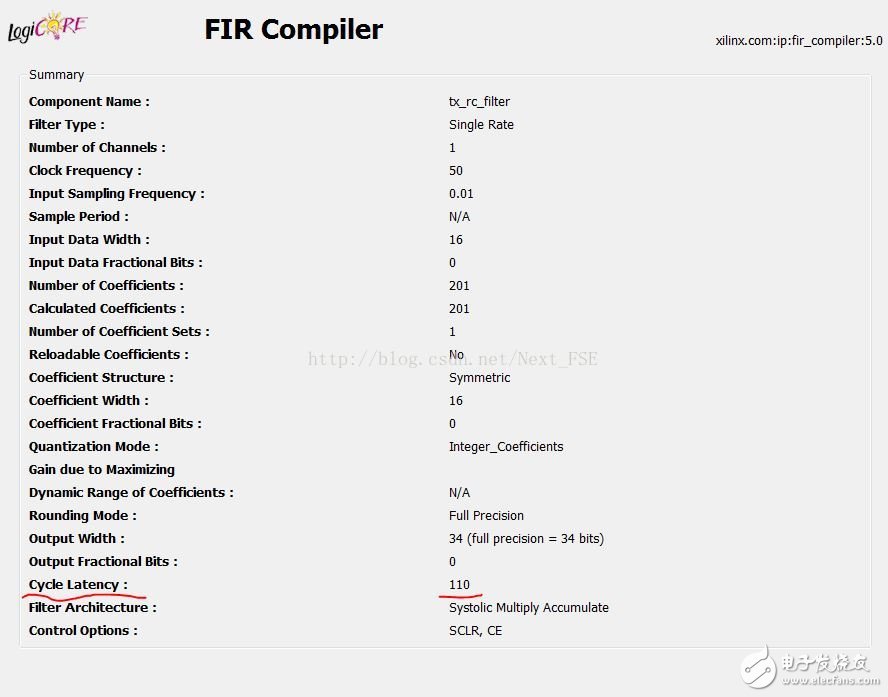

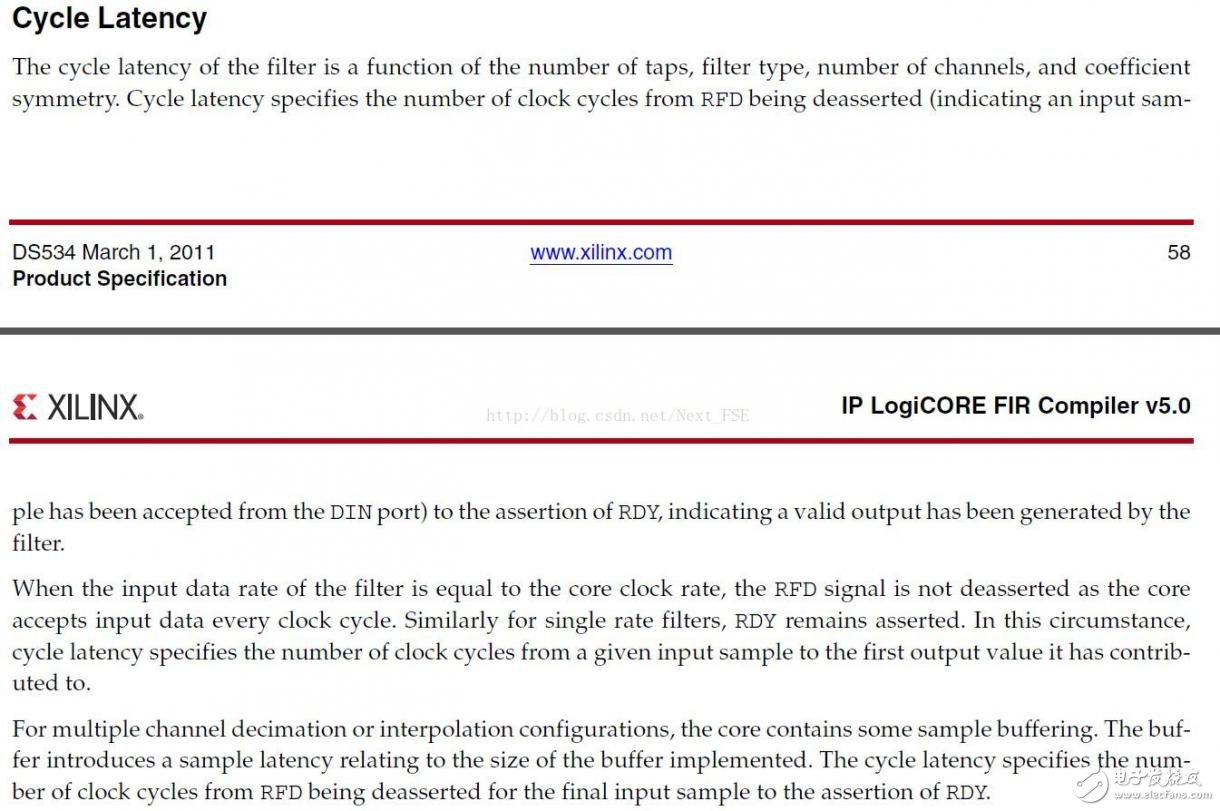

小弟现在需要一个带通滤波器,大概设计方案是通过MATLAB的fdatool设计滤波器,生成滤波系数,再调用fpga的ip核,但是这样占用fpga的太多资源,有没有什么更好的方法来实现,或者是我的参数设置不对,贴出我的fir编译器

2017-07-10 15:20:09

使用的是Vivado,希望使用其FIRIP核设计一个滤波器,该滤波器不是固定结构,而是可以根据项目中的变量filterselect的值选择其通带频率,例如filterselect=0,1,2,3

2017-08-10 05:49:04

求解答怎么利用IP core设计收音机的FIR滤波器

2013-08-09 17:41:36

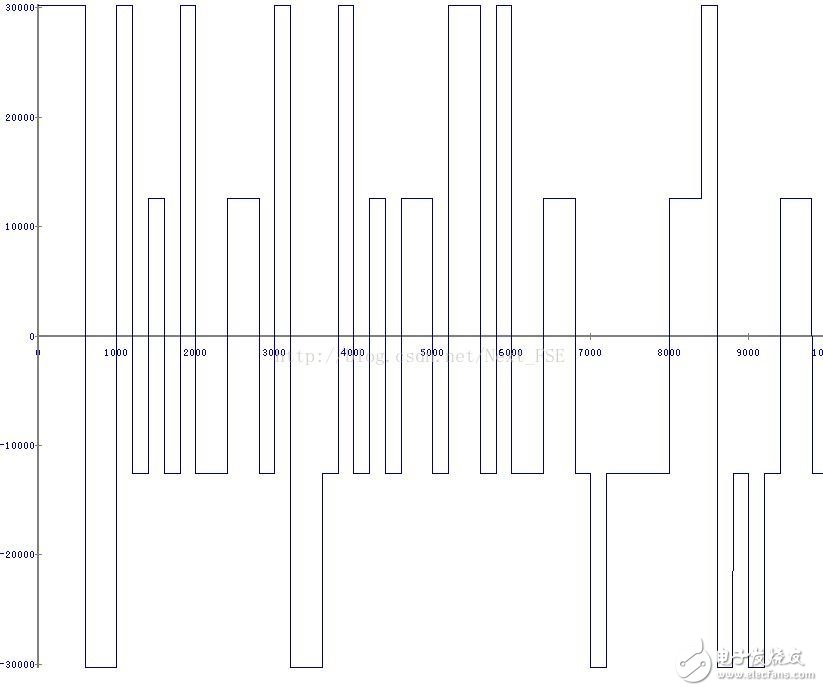

依次送入FIR滤波器IP核进行处理,输出结果写入fir_result.txt文本中。`timescale 1ns/1psmodule zstar_fir_sim();reg clk; reg [15

2020-01-14 09:39:45

如何去实现程控滤波器的设计?设计程控滤波器又有何作用?

2021-04-13 06:24:42

给响应带来了损失。现有的视频信号制式包括RGB、分量视频、复合视频和RGB PC图像等。所有应用与制式都希望视频滤波器能达到"线性相位",这是群延时(不同频率的延时)特性所要

2021-05-14 07:55:00

我用MATLAB设计好单位增益的滤波器系数,然后导入 FIR 的IP核里面,系数转换成定点数了,但是此时显示的滤波器幅频特性曲线却是100dB的放大倍数,求问怎么让其变成单位增益?

2018-01-27 13:53:00

带通滤波器(BPF)被广泛用于通带非常窄、通带以外任何其它频率被衰减的应用。公式(1)是带通滤波器的二阶带通传输函数:其中,K代表恒定的滤波器增益,Q代表滤波器的品质因数。

2019-06-24 07:23:07

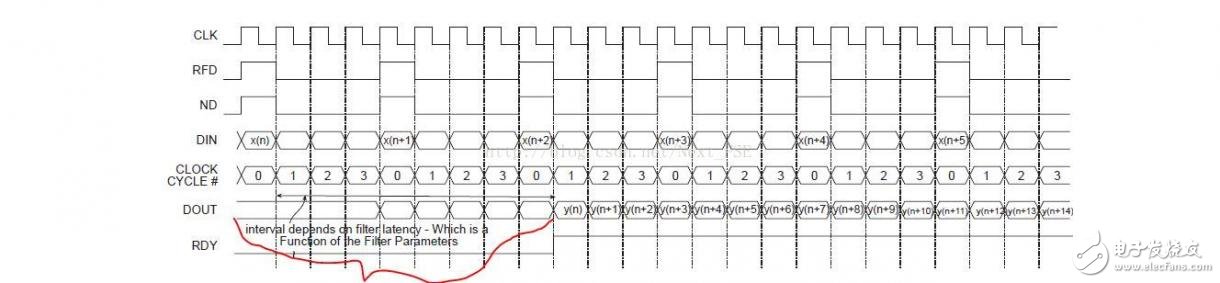

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一个问题。比如说:某个IP,用于计算sin函数,使用了流水线机制,所有从输入到输出需要20个时钟周期的延时。另外,还有一个IP,从输入到输出需要1

2021-06-19 11:06:07

请教大家谁用过 Xilinx PCIe IP 核啊?

2014-01-15 14:38:28

AD9361的FIR滤波器是否可以配置成RRC滤波器?只能用作低通滤波器吗?另外,FIR滤波器的2/4倍插值是对原信号进行补0吗?

2019-01-07 11:31:53

书籍共七章,首先概括介绍了有源滤波器的种类和结构特点,接着分开详细介绍了巴特沃斯和切比雪夫低通滤波器,带通滤波器,带阻滤波器,全通和恒定延时滤波器的特点和实际的设计方法。本资料来自 世纪电影网 wkubae所发资料

2020-11-18 22:22:25

相同,滤波器阶数为10。 图1 可以发现转置型结构不对输入数据寄存,而是对乘累加后的结果寄存,这样关键路径上只有1个乘法和1个加法操作,相比于直接型结构,延时缩短了不少。 综合得到结果

2019-06-28 08:22:02

频率滤波器大概分为带通、带阻、高通、低通。特性不同的模拟滤波器中经典滤波器有Butterworth 和 Chebyshev 。其中,Butterworth 滤波器特点是通带处幅值特性平坦,而 Chebyshev 滤波器则比前者的截至特性要好,但通带处的幅值有振荡。

2019-09-19 09:00:57

有源滤波器中数字低通滤波器的设计及其DSP实现摘要:介绍了基于瞬时无功功率理论的ip iq 谐波检测方法及对低通滤波器的要求,分析讨论了数字低通滤波器的类

2010-05-13 17:19:18 90

90 抗混迭滤波器,什么是抗混迭滤波器

背景知识:基本原理:抗混叠滤波器g(n)的输入和输出之间的卷积关系如下

2010-03-24 14:02:02 1287

1287 光滤波器,什么是光滤波器

基于干涉原理的滤波器:熔锥光纤滤波器、Fabry-Perot滤波器、多层介质膜滤波器、马赫-曾德干涉滤波

2010-04-02 16:54:04 2190

2190 数字滤波器用于离散系统;模拟滤波器用于连续时间系统,也可以用在离散时间系统中,比如SC(开关电容)滤波器。 数字滤波器 由数字乘法器、加法器和延时单元组成的一种算法或装置。

2012-03-30 14:11:39 4878

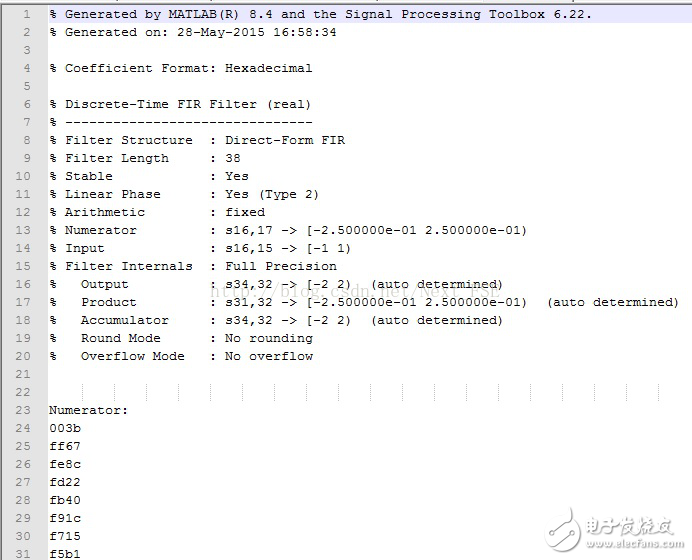

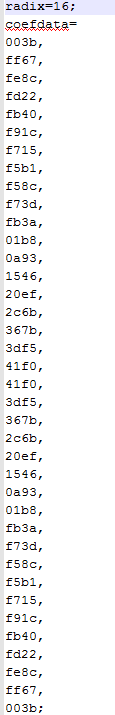

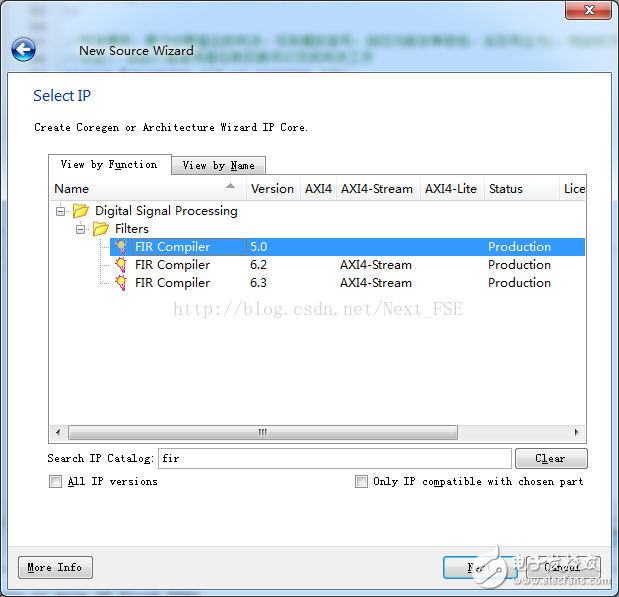

4878 Xilinx FIR IP的介绍与仿真 1 xilinx fir ip 简介 1)符合 AXI4-Stream 的接口 2)高性能有限脉冲响应(FIR),多相抽取器,多相内插器,半带,半带抽取

2020-10-30 12:29:01 511

511

电子发烧友App

电子发烧友App

评论