时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。

2016-05-29 23:25:10 1064

1064 时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

使用DCM进行相位同步和PLL这24MHz高达300MHz的信号我把这个300MHz的信号充电到我的逻辑我的问题是:在我的.UCF计时时序约束中,我只指定了对300MHz信号的约束,并假设它将通过DCM

2019-02-28 06:24:28

本帖最后由 卿小小_9e6 于 2020-10-21 18:31 编辑

资料分享:《VIVADO从此开始高亚军编著》此版本为2017年出版,例程软件Vivado2016.2,共七章,适合入门

2020-10-21 18:24:48

Vivado运行Report Timing Summary时,只显示各个子项目最差的十条路径,很可能并不包含你最关心的路近,这个时候显示指定路径的时序报告就显得很重要了,下面就简单介绍一下

2021-01-15 16:57:55

使用Vivado 2015.4我生成了两个FIFO和一个Aurora Core。我收到与Vivado自动生成的时序约束相关的严重警告。由于我的FIFO在整个设计中被多次使用,我需要一种让Vivado

2018-11-02 11:30:10

(约束指令介绍)UG904 - Vivado Design Suite User Guide -Implementation UG906- Vivado Design Suite User Guide

2018-09-26 15:35:59

我正在使用vivado 2017.4,并且设计成功完成了p& r,没有任何pblock限制。在尝试添加pblock约束时,实现会挂起以下内容:阶段1.2 IO放置/时钟放置/构建放置器

2018-11-08 11:38:17

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

此版只讨论时序约束约束理论约束方法约束结果时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II

2013-05-16 18:51:50

、Vivado基本操作流程2、时序基本概念3、时序基本约束和流程4、Baselining时序约束5、CDC时序约束6、I/O时序7、例外时序约束8、时序收敛优化技术

2018-08-01 16:45:40

怎么进时序约束的,时序约束是自己输进去的

2014-01-17 15:10:43

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

vivado默认计算所有时钟之间的路径,通过set_clock_groups命令可禁止在所标识的时钟组之间以及一个时钟组内的时钟进行时序分析。 1.异步时钟组约束声明两时钟组之间为异步关系,之间不进行时序

2018-09-21 12:40:56

小弟刚学习FPGA不久,仅仅学习了一个普通工作流,但对于时序约束什么的几乎一无所知最近在编一个模块时,VIVADO综合实现出来Timing那里是红色,WNS TNS为负值,只知道似乎是当前布线延迟

2015-09-06 20:08:42

。

时序约束可以让VIvado和Quartus等FPGA开发软件,在布线时检测综合出来的逻辑电路是否满足这个时序要求,并生成时序报告。

一、建立/保持时间

1、基本概念

设定时序约束的目的就是为了满足

2023-11-15 17:41:10

刚刚看的一个非常不错的讲解时序约束的资料。在此分享下。

2015-01-21 15:14:35

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing

2016-06-02 15:54:04

转帖0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还

2017-12-27 09:15:17

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

有没有哪位大神对ISE的时序约束比较熟悉,尤其是多周期约束这一块。在Quartus中使用比较简单,而且相关资料也比较多,但是ISE中的资料好像不是那么多,而且也没有针对具体例子进行分析。官网上给出

2015-04-30 09:52:05

在Vivado 2016.1和Kintex-7 FPGA中,我可以使用名为“Clocking Wizard v5.3”的IP来配置为我的项目输出系统时钟的MMCM。自定义此IP后,将自动为IP生成约束

2019-08-02 09:54:40

过程中,我从map,par和trce中收到以下警告:警告:时序:3223- 时序约束TS1 =从TIMEGRP“TNM_C”到TIMEGRP“TNM_P”的MAXDELAY在时序分析期间忽略75 ns

2018-10-10 11:03:02

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

大家好我的设计效果不佳,所以我想用chipcope来检测信号。但是,在设置“keep hierarchy = yes”之后,不能满足时序约束。有什么办法可以解决这个问谢谢!最好的祝福YHM以上

2019-03-28 13:38:35

嗨,我们正在尝试使用Vivado工具链手动路由FPGA,并想知道应该使用什么工具来手动路由Virtex 7 FPGA。还可以在Vivado时序分析器工具中指定温度和电压值来估算设计时序吗?我们将如

2018-10-25 15:20:50

如何编写高级时序约束?我使用提前一词,因为我知道如何在ucf文件中约束的基本知识。基本内容包括将引脚分配给相应的输出和顶部模块的输入,并配置时钟引脚周期。但是除了LOC和PERIOD之外,还有很多

2019-03-27 09:58:42

问一下啊,在写时序约束的时候,如何根据设计的要求进行时序上的约束啊,看了好多网上的资料,说的都是有关约束的一些原理。有没有那位大侠给个设计实例啊!

2023-04-23 11:42:16

有哪位大神有NI DIAdem的培训资料或者培训课程?

2022-01-19 23:00:25

一直对时序约束没有什么概念,向各位大神求教经验及可以拜读的资料

2017-04-11 21:42:03

时,老是范糊涂,因为Quartus II和ISE对IO端口的约束方式和计算公式略有不同,容易混淆。而老掉牙的ISE中也只是光秃秃的没有任何提示,Vivado可好了,出现了标好了具体约束值的时序图

2016-01-11 16:55:48

网上找到一个介绍,偏移约束也是一类基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,只能用于端口信号,不能应用于内部信号我现在将一个输入时钟clk0经过一个DCM产生clk1 ,然后

2017-04-27 16:12:30

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

时序约束文件SDC支持哪些约束?

2023-08-11 09:27:15

静态时序分析(Static Timing Analysis,STA)是流程成功的关键环节,验证设计在时序上的正确性。STA过程中设计环境和时序约束的设定、时序结果的分析和问题解决都需要设计工程师具有

2020-09-01 16:51:01

本手册主要描述高云半导体时序约束的相关内容,包含时序约束编辑器(Timing Constraints Editor)的使用、约束语法规范以及静态时序分析报告(以下简称时序报告)说明。旨在帮助用户快速

2022-09-29 08:09:58

ISE时序约束:What effects do timing constraints have on your project?• The implementation tools do

2010-01-11 08:54:06 87

87 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0 此课程将教会你:1)创建并编辑UCF文件;2)源同步和系统同步接口要求的I/O时序约束和设计修改;3)通过Tcl命令行完成设计;4)用SmartGuide技术保护设计结果;5)用PlanAhead工具创建

2010-12-14 15:02:38 0

0 时序约束的概念 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(STA, IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE

2011-03-16 18:10:38 0

0 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 Xilinx时序约束设计,有需要的下来看看

2016-05-10 11:24:33 18

18 FPGA学习资料教程之Xilinx时序约束培训教材

2016-09-01 15:27:27 0

0 美国赛灵思官方授权培训伙伴依元素科技,以赛灵思最新的客户培训课程,通过Webex在线举办免费培训。近期推出的在线免费培训是 “Vivado设计套件工具流程”。 Xilinx采用先进的 EDA 技术

2017-02-08 11:58:12 423

423 这个为期 1 天的课程奖不仅向您介绍内核和工具,阐述如何有效地利用触发器,而且还将向您介绍如何调试设计以缩短整个设计开发时间的方法。该培训提供动手实验以展示 如何利用 Vivado® Design Suite 的调试工具解决高级验证和调试挑战。 了解更多 »

2017-02-09 02:20:11 218

218 最近有些朋友在ISE中做的V7项目需要切换到vivado来,但导入代码后,导入约束时,发现vivado不再支持UCF文件,如果手抄UCF约束到 VIVADO 的 XDC 约束,不仅浪费时间,而且容易出错,这里介绍一种方法可以实现两种约束的切换。

2017-03-24 13:54:36 8529

8529

TI培训 《基于AM335x LED WALL应用介绍》 课程资料

2017-10-19 10:17:57 5

5 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

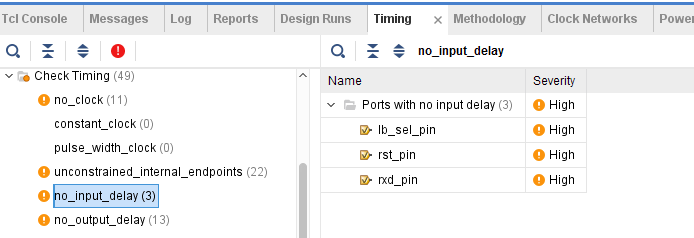

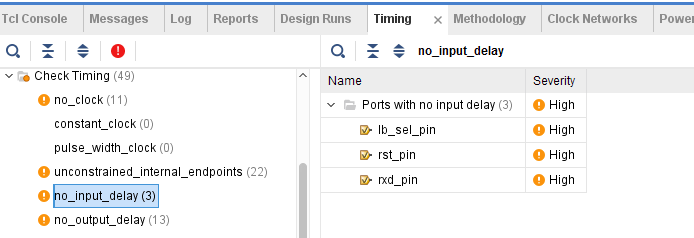

过程必须以满足XDC中的约束为目标来进行。那么: 如何验证实现后的设计有没有满足时序要求? 如何在开始布局布线前判断某些约束有没有成功设置? 如何验证约束的优先级? 这些都需要用到Vivado中的静态时序分析工具。

2017-11-17 18:03:55 34003

34003

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

时序分析基本概念介绍——Timing Arc

2018-01-02 09:29:04 23487

23487

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 14208

14208

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 6374

6374 了解时序约束向导如何用于“完全”约束您的设计。

该向导遵循UltraFast设计方法,定义您的时钟,时钟交互,最后是您的输入和输出约束。

2018-11-29 06:47:00 2702

2702

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 3077

3077

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

Timing Report中提示warning,并不会导致时序错误,这也会让很多同学误以为这个约束可有可无。 但其实这种想法是不对的,比如在很多ADC的设计中,输出的时钟的边沿刚好是数据的中心位置,而如果我们不加延迟约束,则Vivado会默认时钟和数据是对齐的。 对

2020-11-14 10:34:35 2757

2757

伪路径约束 在本章节的2 约束主时钟一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径

2020-11-14 11:28:10 2636

2636

create_clock:和其他FPGA EDA tool一样,在vivado中timing约束越全越好,越细越好,而place约束可以很粗略或者省略调。约束中最常用的语句就是

2021-01-12 17:31:39 21

21 本文档的主要内容详细介绍的是Xilinx的时序设计与约束资料详细说明。

2021-01-14 16:26:51 32

32 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 4401

4401 很对人在使用Vivado时喜欢使用多个约束文件对整个工程进行约束,同时Vivado允许设计者使用一个或多个约束文件。虽然使用一个约束文件对于一个完整的编译流程来说看似更方便,但是在一些情况下,这会

2021-10-13 16:56:54 6309

6309 VIVADO中时序报告中WNS,WHS,TNS,THS含义运行“report_timing”或“report_timing_summary”命令后,会注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 2848

2848 明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 2922

2922

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

电子发烧友网站提供《Gowin设计时序约束用户指南.pdf》资料免费下载

2022-09-15 16:04:17 2

2 随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的?

2022-09-15 10:24:37 972

972 在描述时序约束时,一个重要的原则是确保约束简洁高效。简洁高效意味着约束只针对指定的对象,即约束对应的对象的个数

2023-02-23 09:03:38 855

855 本章节主要介绍一些简单的时序约束的概念。

2023-03-31 16:37:57 928

928

对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20:31 2368

2368

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 1260

1260

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

很多小伙伴开始学习时序约束的时候第一个疑惑就是标题,有的人可能会疑惑很久。不明白时序约束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 829

829

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414 本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 694

694 今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00:02 1397

1397

本小节对时序约束做最终的总结

2023-07-11 17:18:57 351

351

本文继续讲解时序约束的第四大步骤——时序例外

2023-07-11 17:17:37 417

417

时序约束出现时序违例(Slack为负数),如何处理?

2023-07-10 15:47:06 3099

3099 'sys_clk'. [timing.xdc:37](63 more like this) A:对于约束的问题,我们可以在Vivado的tcl中先执行一下这些约束指令,如果有

2023-08-08 14:10:48 711

711 电子发烧友网站提供《Vivado Design Suite用户指南:使用约束.pdf》资料免费下载

2023-09-13 15:48:39 0

0 有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18:36 291

291

电子发烧友App

电子发烧友App

评论