目前,图像监控系统大多采用PC和视频采集卡作为系统主要部分,基于嵌入式技术的图像监控系统设备在我国还只是起步阶段,没有成熟的产品应用。这一现状的根本原因就是我国在开发这类产品时,没有统一的开发标准和共用的开发平台,而且没有可靠的功能和性能测试标准,各个企业的开发技术力量分散,极大的影响了该类产品开发的效率和可靠性。而制造出来的产品同国外同类产品相比,功能相差太大,没有竞争力,市场基本上被国外公司所占领。因此,开发一个该类嵌入式系统势在必行。

系统总体方案

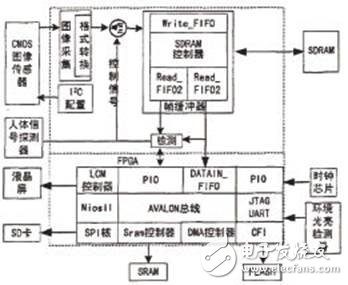

为了实现自动图像报警和图像采集,本文设计了动体检测算法,这是因为绝大多数情况下我们只对监控区域中运动的物体感兴趣,这样可以过滤掉只包含静态背景的图像,从而降低了对有限的嵌入式硬件资源的消耗。由于活动物体大多是人,而且这也是图像监控的目标,为此加入了人体信号探测器,用以辅助动体检测,以达到降低图像报警误报率的目的。本系统主要集成了图像采集、控制和存储等器件或芯片,组成了以FPGA为控制核心的实时图像监控系统。系统的总体方案如图1所示。

图1 图像监控系统结构图

系统工作流程为:系统上电后,FPGA从外部EEPROM自动加载程序,I2C模块对CIS进行初始化工作参数配置。CIS向FPGA输入图像数据信号,FPGA将采集的原始数据(RAW)转换成RGB格式,帧缓冲模块(Frame Buffer)每次将相邻两帧图像数据写入SDRAM,然后比较这两帧图像的差值,如果差值大于设定的阈值,并且人体探测器输出高电平,就认为检测到了外界场景的运动,系统会自动将捕获的图像输出到SD卡进行存储。图2给出了系统的工作流程。

图2 系统工作流程图

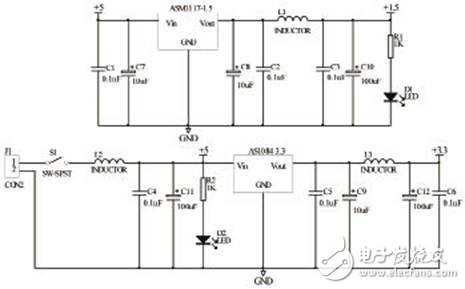

图3 电源电路原理图

系统硬件设计与实现

图像监控系统处理的数据量较大,同时还要满足实时性要求,因此板载电路需要选用容量较大,速度较快的器件。本系统采集的一帧图像分辨率大小为640×480,色深是24位,检测时需要在SDRAM缓存两帧,因此SDRAM的容量必须大于1.8M字节(640×480×3×2=1843200字节),由于每个像素位宽为24位,同时NIOS是32位的处理器,所以SDRAM的位宽最好是32位。外部提供给FPGA的晶振频率必须大于CIS的像素时钟25MHz。考虑到检测算法需要较多的逻辑资源,因此FPGA的片内LE要很丰富,另外FPGA的管脚必须要满足外部器件连接的要求,在本系统中要实现所有器件的I/O口相连,FPGA的I/O管脚必须大于150个。由于电路原理图较多,这里只给出其中的一部分。

主控制芯片电路

本系统选用的Cyclone系列FPGA器件的具体型号是EPlCl2Q240C8。逻辑资源达12060个逻辑单元(LE,Logic Elements),片内RAM的容量为239616bits。完全可以满足图像采集的设计要求。其内核供电采用1.5V、0.13um工艺,功耗较低。Cyclone器件支持各种单端I/O接口标准,如3.3V、2.5V、1.8V、LVTTL、LVCMOS、SSTL。Cyclone器件具有两个可编程锁相环(PLL)和八个全局时钟线,提供健全的时钟管理和频率合成功能,实现最大的系统性能。Cyclone器件具有高级外部存储器接口,允许设计者将外部单数据率(SDR)SDRAM,双数据率(DDR)、SDRAM和DDR FCRAM器件集成到复杂系统设计中,而不会降低数据访问的性能。Cyclone系列FPGA器件基于一种全新的低成本架构,从设计之初就充分考虑了成本的节省,因此可以为价格敏感的应用提供全新的可编程的解决方案。

电源电路

一般而言,FPGA器件出于芯片设计、多电平接口的需要,电源都分为两组:VCCINT和VCCIO,即内核电源和I/O电源,随着芯片内部连线尺度的逐渐减小,核心电源电压和接口电压也越来越低。本设计中EPlCl2器件的VCCINT为1.5V,VCCIO为3.3V。目前总的来说有三种电源解决方案,分别是线性稳压器电源(LDO)、开关稳压器电源和电源模块。

LDO线性稳压器适用于降压变换,具体效果与输入/输出电压比有关。从基本原理来说,LDO根据负载电阻的变化情况来调节自身的内电阻,从而保证稳压输出端的电压不变。其变换效率可以简单地看作输出与输入电压之比。

由于采用线性调节原理,LDO本质上没有输出纹波。与LDO相比,DC/DC调整器输出纹波电压较大、瞬时恢复时间较慢、容易产生电磁干扰(EMI)。系统电源输入电压为5V,3.3V电压供电部分采用了ASl084;此外,对于FPGA的PLL工作需要的1.5V电源部分,采用AMS1117-1.5 LDO来实现。

由于Altera的PLL是模拟电路实现的,其对电源噪声比较敏感,所以在设计PCB的时候,对给PU的供电部分要做一些特殊的处理。即使在设计中没有用到PLL也必须给其供电。

本系统中选用的EPlCl2F400C8芯片的输入输出接口电压为3.3V,内核电压降低到1.5V,这样可以降低功耗,有利于系统的稳定,但也给电源供电和其它芯片的选择带来了麻烦,系统中其它芯片的接口电压必须为3.3V,至少也要兼容3.3V,电源设计中需要考虑的主要问题是功率是否满足的问题。

SD卡接口电路

在各种存储设备中,SD卡不仅小巧,而且功耗很低,另外市面上常见SD卡的容量可达到2GB以上,因此非常适合用于对体积和功耗要求严格的嵌入式图像存储。如图4所示,SPI的两个数据线DAT0、CMD分别接上拉电阻,这是为了使本电路可以与MMC卡的接口兼容。卡的供电采用可控方式,这是为了防止SD/MMC卡进入不确定状态时,可以通过对卡重新上电使卡复位而无需拔出卡。可控电路采用P型MOS管,由FPGA的GPIO口SDPC进行控制,当SDPC输出高电平时,MOS管关断,不给卡供电;当SDPC输出低电平时,MOS管开通,VCC3V3电源给卡供电。考虑管子开通时,漏极与源极之间的压降要足够小(保证SD/MMC卡的工作电压在允许范围内),管子允许通过的电流也要满足卡的要求,一般一张SD/MMC卡工作时的最大电流通常为45mA左右,所以选用的MOS管要求允许通过100mA左右的电流。采用2SJ355的目的是当它开通时,管子上的压降比较小。

卡检测电路包括两部分:卡是否完全插入到卡座中和卡是否写保护。检测信号由卡座的两个引脚以电平的方式输出。当卡插入到卡座并插入到位时,SDIN(第10脚)由于卡座内部触点连接到GND,输出低电平;当卡拔出时,该引脚由于上拉电阻R2的存在而输出高电平,该输出由FPGA的输入引脚来检测。卡是否写保护的检测与卡是否完全插入到卡座中的检测原理是一样的。

图像传感器电路

图像的输入端的采集模块是CMOS图像传感器,与CCD传感器相比,CMOS传感器不仅成本远低于CCD产品。而且CMOS传感器可轻松实现较高的集成度(比如CMOS被广泛用于拍摄手机的微型摄像头),另外CMOS传感器拥有超低功耗的优点。本系统图像采集用于监控领域,对于图像的质量要求不是非常高,而对传感器的功耗要求必须很低,而且可以直接输出系统需要的数据格式,因此本系统的图像采集部分选用了CMOS图像传感器。

在本设计中采用美光科技公司的MT9M011型号CMOS图像传感器,MT9M011是一块SXGA(super extended graphics array,超大扩展图像阵列)制式的1/3英寸主动式数字图像传感器,其有效图像序列范围为1280×1024,结合了众多数码照相机具有的功能如开窗取景、行列跳跃、快照模式等等,可以通过一个两线的串口来实现可编程操作,并且具有功耗低的特点。片载A/D转换器将提供每像素I/O位的输出精度,帧有效和行有效信号将在特定的引脚上输出,并且还配有像素时钟同步响应的有效数据。

NiOS系统软件设计及实现

本系统的软件设计是以C语言形式在利用Altera公司的软件集成开发工具IDE所提供的硬件配置模块(HAL)的函数支持下来完成编写的。系统启动后,进行初始化工作,初始化程序主要完成初始化DMA通道及清FIFO控制接口的FIFO缓冲器等。随后系统进入主循环状态,并检测按键。当检测到DETECT时,启动FIFO控制接口开始保存数据,当检测到data_avaible有效时,启动一次DMA传输。如此循环,直到检测到SAVE_DONE为止,就实现了图像数据的采集功能。

UART传输程序设计

uart传输程序主要是将图像数据传输到电脑进行显示,用于调试。在PC端,通过串口接收工具和Matlab将图像显示出来。Nios II系统中,可以通过ANSI C文件操作的标准库函数来执行UART传输(uart 0),即将UART作为文件来处理。执行过程为:打开外设UART并获得外设旬柄——fopen();向外写入数据——fWrite();关闭外设——fclose()。

SD存储卡的程序设计

SD卡程序设计包括驱动程序和文件系统两部分设计。两部分通过文件系统的接口函数相连接。驱动程序包括硬件配置模块和命令应用模块。硬件配置模块包括访问SD卡的硬件环境配置、SPI接口实现通讯的基本函数、内存变量初始化以及SPI中断的处理。命令应用模块提供访问SD卡的读数据函数和写数据函数。

结论

本文主要完成了嵌入式图像监控系统的设计,该系统克服了模拟图像监控技术具有的弊端,在普通家庭、临时性作业场所中具有很强的应用前景。这些领域一般对视频传输指标的要求不一定很高,但要求便于携带,同时功耗较小(例如临时性场合等),具有体积小、功耗低、成本低、速度快、稳定性好等特点,可以有效地克服传统的基于计算机的监控系统的缺点。系统可做为一个智能部件“嵌入”到各种应用系统中,如将其配上网络接口接上计算机系统,即可构成一个监控网络系统,是一种相对独立的OEM部件。

电子发烧友App

电子发烧友App

评论