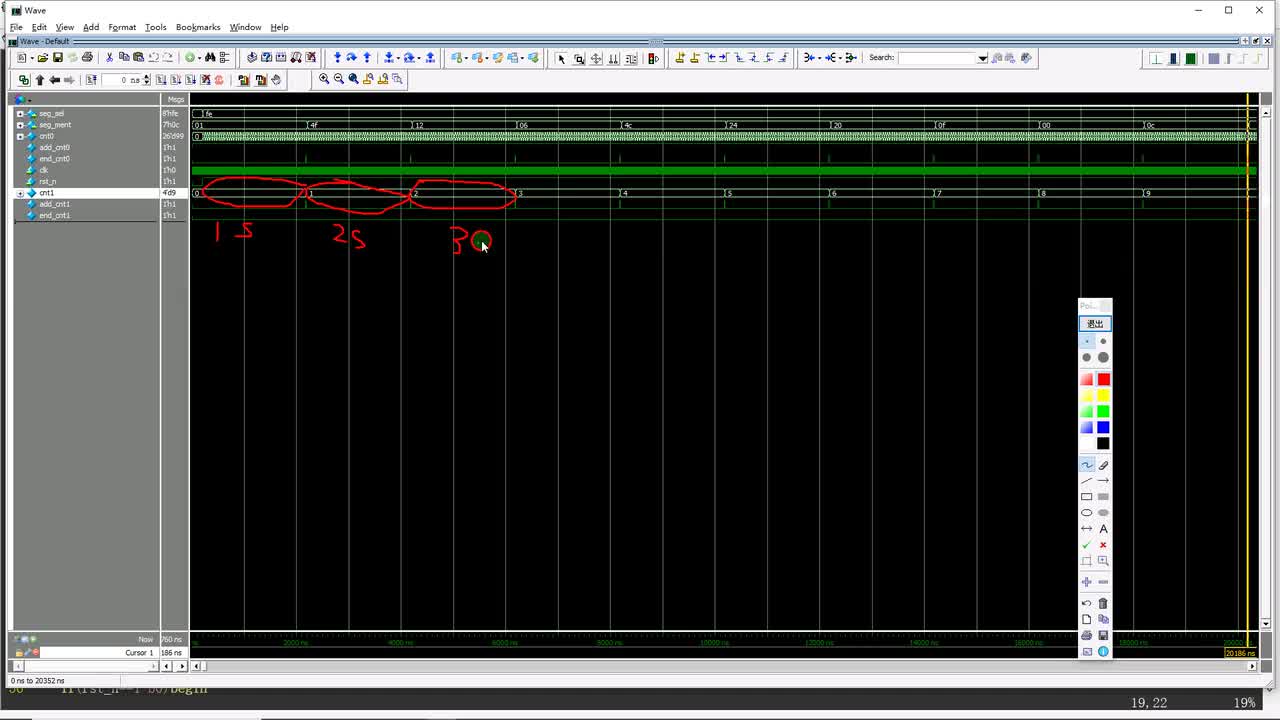

案例3. 当收到en1=1时,dout产生3个时钟周期的高电平脉冲;当收到en2==1时,dout产生2个周期的高电平脉冲。

上面波形图显示了描述的功能。第3个时钟上升沿收到en1==1,所以dout变1并且持续3个时钟周期;在第9个时钟上升沿看到en2==1,所以dout变1并且持续2个时钟周期。注意,en1==1和en2==1的出现是没有顺序的。

有读者可能会问,如果en1==1和en2==1同时出现,或者说在dout==1期间,出现了en1==1或者en2==1,该怎么办?请不要考虑这种情况,本案例假设永远不会出现该情况。明德扬在模块划分规范时,会要求各个模块之间配合清楚。否则每个模块都要处理所有情况,那就相当复杂了。

看到大于1的数字,就知道要计数。推荐的计数方式如下:

计数器cnt都是计算dout==1的个数。不要考虑使用2个计数器来分别计数en1和en2的情况,这是因为即使用了2个计数器,这2个计数器都不是同时在计数的,不同时计数就说明可以合并。

在确认计数器数多少个时,我们遇到了问题。因为这个计数器有时候数到3个就清零(en1==1触发的波形),有时候数到2个就清零(en2==1触发的波形)。此时,我们建议你用变量x代替,即数 到x个。注意,verilog是没有变量的概念的,这个变量,是明德扬提出的一个设计概念,x本质上还是一个信号。

引入变量有什么用呢?设计计数器时就方便了,该计数器加1条件是dout==1,数x个就结束,因此代码如下:

甚至我们还可以写出dout的代码,dout变1的条件是:en1==1或者en2==1;变0的条件是:计数器数完了。所以代码如下:

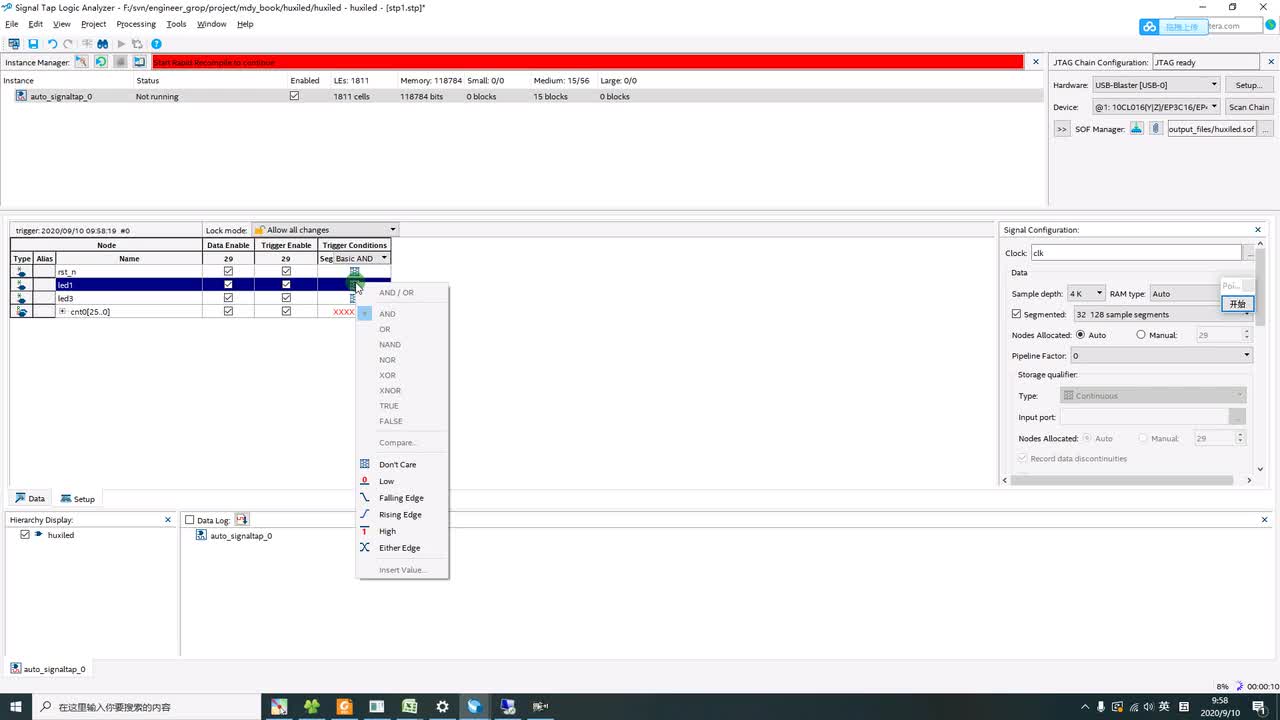

我们再设计一下变量x,我们知道计数器en1==1触发的时候数3个就清零,en2==1触发的时候数到2个就清零,为此增加一个信号flag_sel来区分这两种情况,flag_sel==0表示是en1==1触发的,flag_sel==1表示是en2==1触发的,波形如下:

flag_sel变0的条件是遇到en1==1,flag_sel变1的条件是遇到en2==1,为此flag_sel的代码如下。

有了flag_sel,我们就好区分x的值了。flag_sel为0时,x为3(数3个清零);flag_sel为1时,x为2(数2个清零),此时要用组合逻辑设计x,不然会出错的。代码如下:

至此,本工程的主体程序已经设计完毕,本题,我们使用了变量x,这是明德扬的至简设计方法中的变量法。

将module的名称定义为my_ex3。并且我们已经知道该模块有5个信号:clk、rst_n、en1、en2和dout。为此,代码如下:

其中clk、rst_n、en1和en2是输入信号,dout是输出信号,并且5个信号都是1比特的,根据这些信息,我们补充输入输出端口定义。代码如下:

接下来定义信号类型。

cnt是用always产生的信号,因此类型为reg。cnt计数的最大值为2,需要用2根线表示,即位宽是2位。add_cnt和end_cnt都是用assign方式设计的,因此类型为wire。并且其值是0或者1,1个线表示即可。因此代码如下:

dout是用always方式设计的,因此类型为reg。并且其值是0或者1,1根线表示即可。因此代码如下:

flag_sel是用always方式设计的,因此类型为reg。并且其值是0或者1,1根线表示即可。因此代码如下:

x是用always方式设计的,因此类型为reg,并且其值最大为3,用2根线表示即可。因此代码如下:

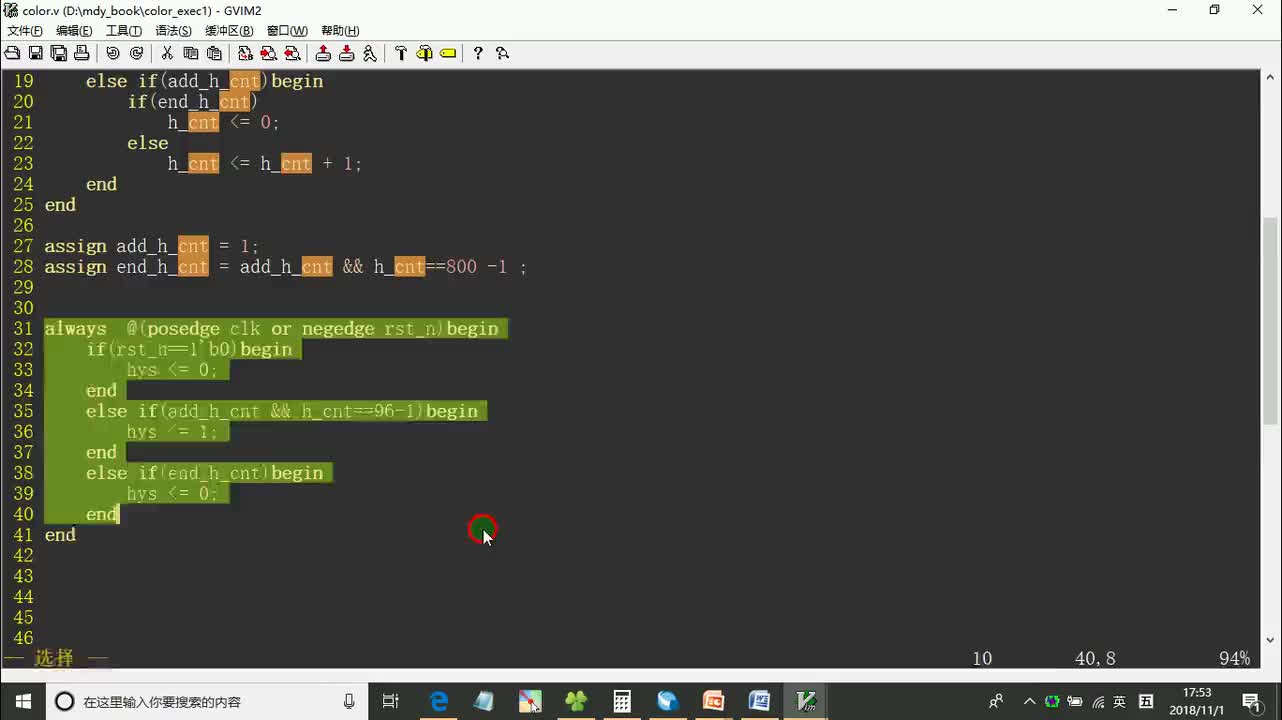

至此,整个代码的设计工作已经完成。整体代码如下:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

module my_ex3(

clk ,

rst_n ,

en1 ,

en2 ,

dout

);

input clk ;

input rst_n ;

input en1 ;

input en2 ;

output dout ;

reg [ 1:0] cnt ;

wire add_cnt ;

wire end_cnt ;

reg dout ;

reg flag_sel ;

reg [ 1:0] x ;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

assign add_cnt = dout==1;

assign end_cnt = add_cnt && cnt==x-1 ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout <= 0;

end

else if(en1==1 || en2==1)begin

dout <= 1;

end

else if(end_cnt)begin

dout <= 0;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

flag_sel <= 0;

end

else if(en2==1)begin

flag_sel <= 1;

end

else if(en1==1)begin

flag_sel <= 0;

end

end

always @(*)begin

if(flag_sel==0)

x = 3;

else

x = 2;

end

endmodule

总结:设计时,我们不要受具体数字的影响,而是仔细识别信号的一致性动作,然后利用变量法来设计。这样就能设计出精妙的代码。

电子发烧友App

电子发烧友App

评论