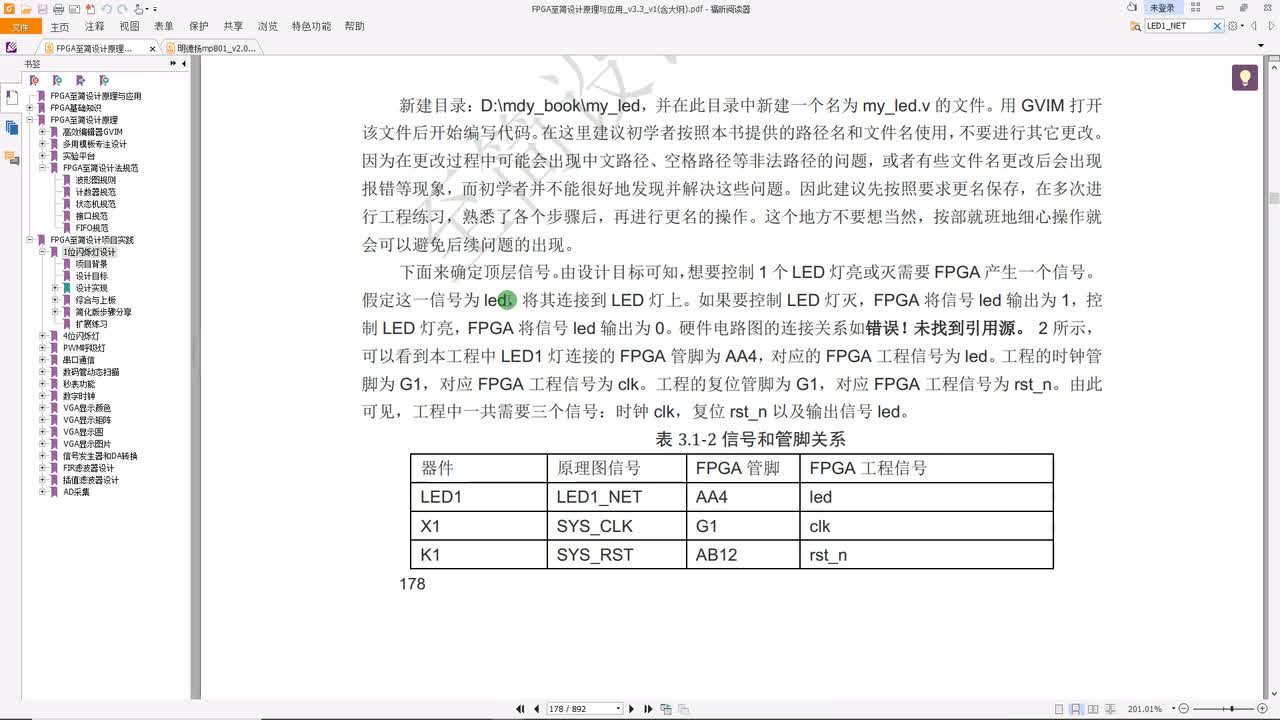

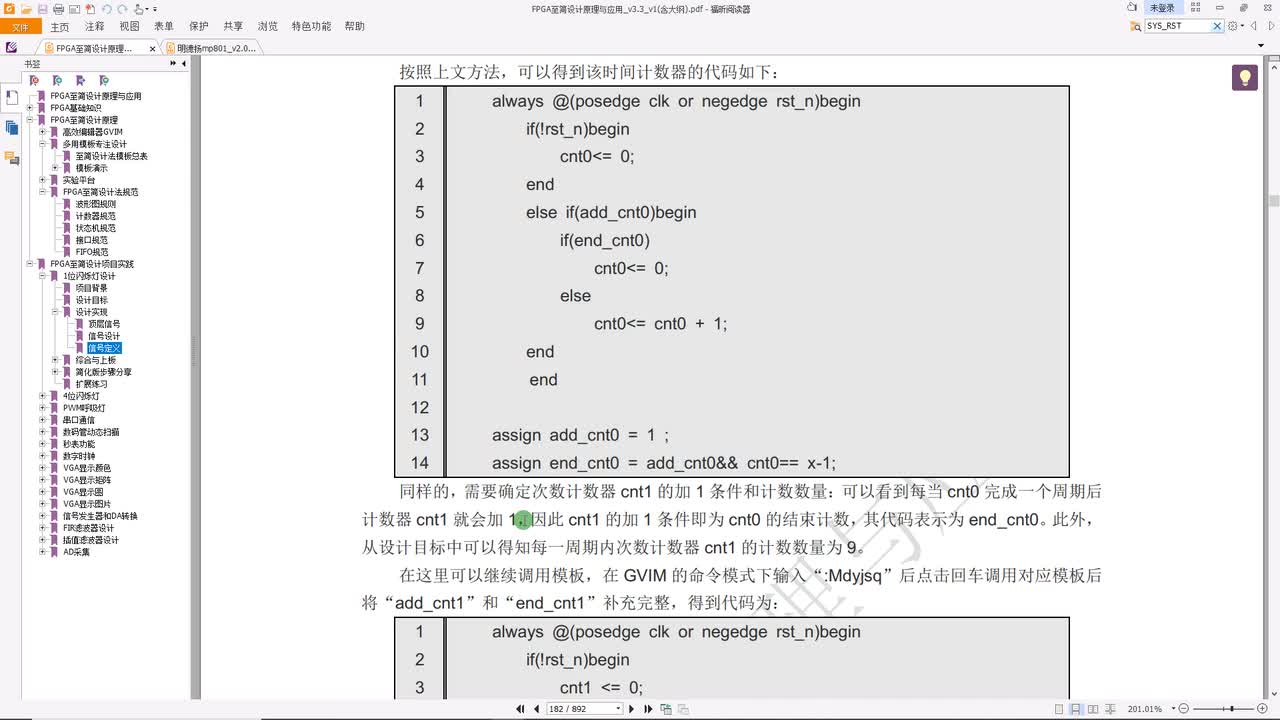

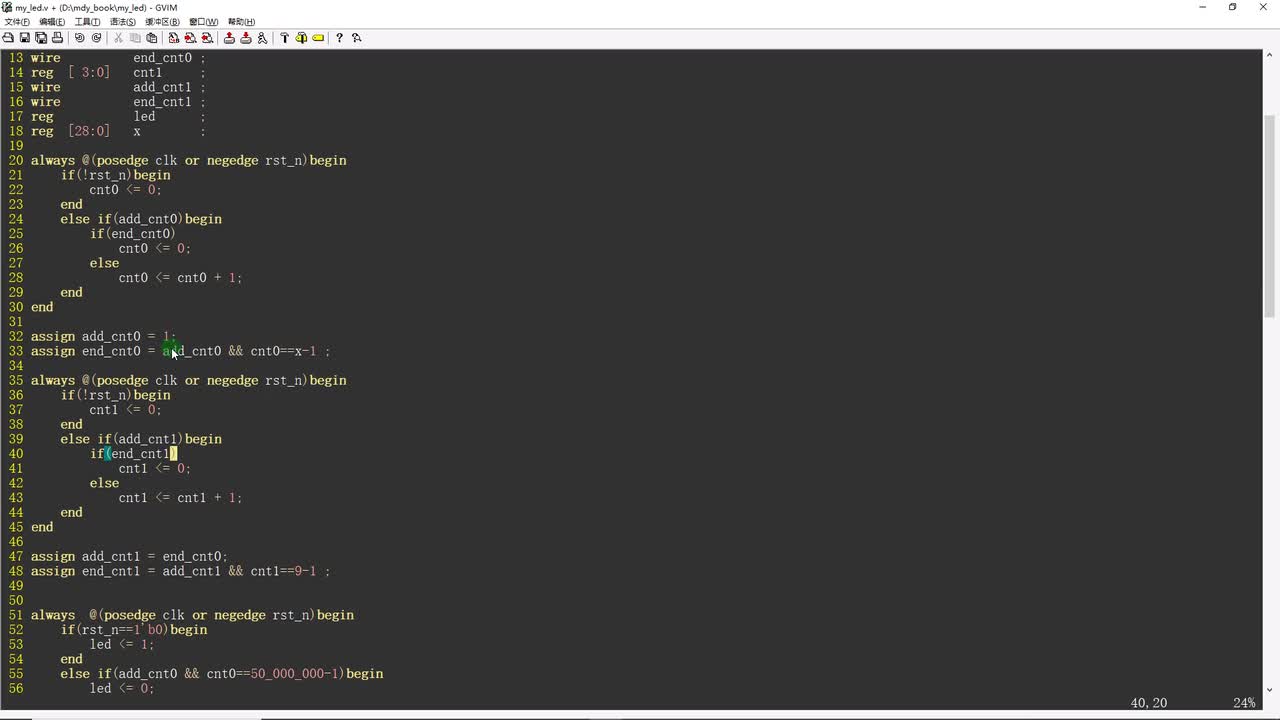

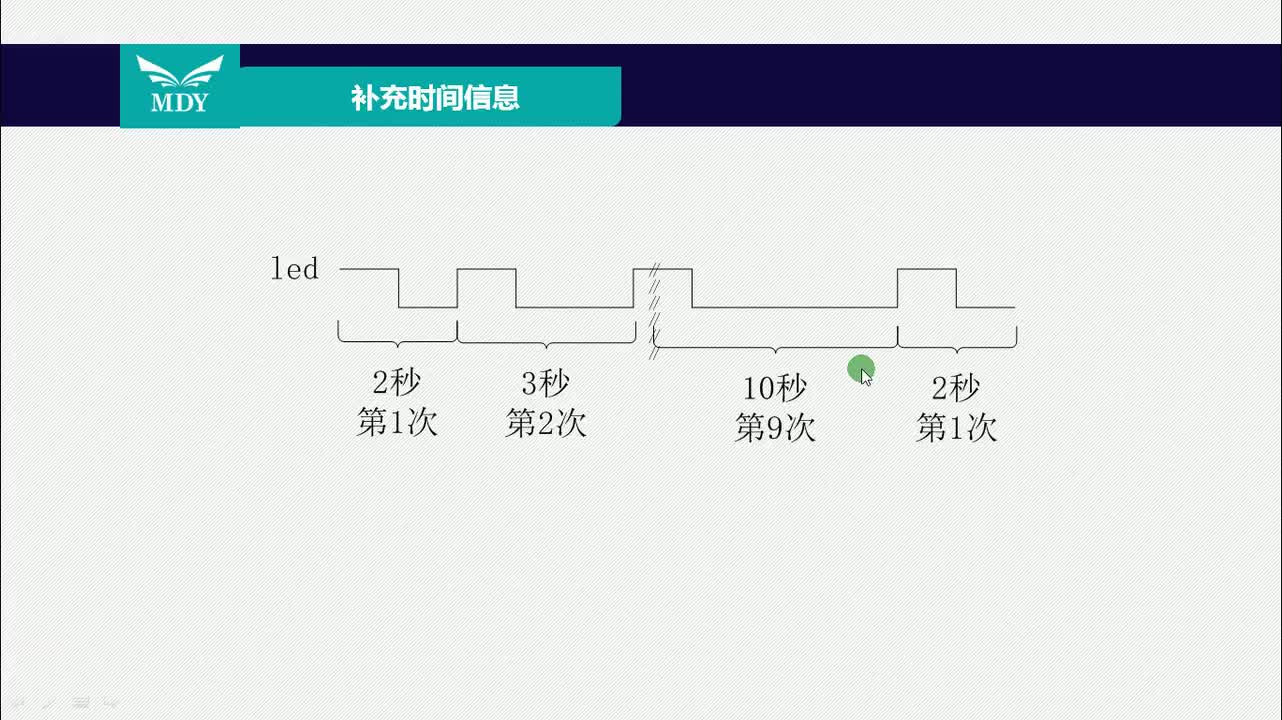

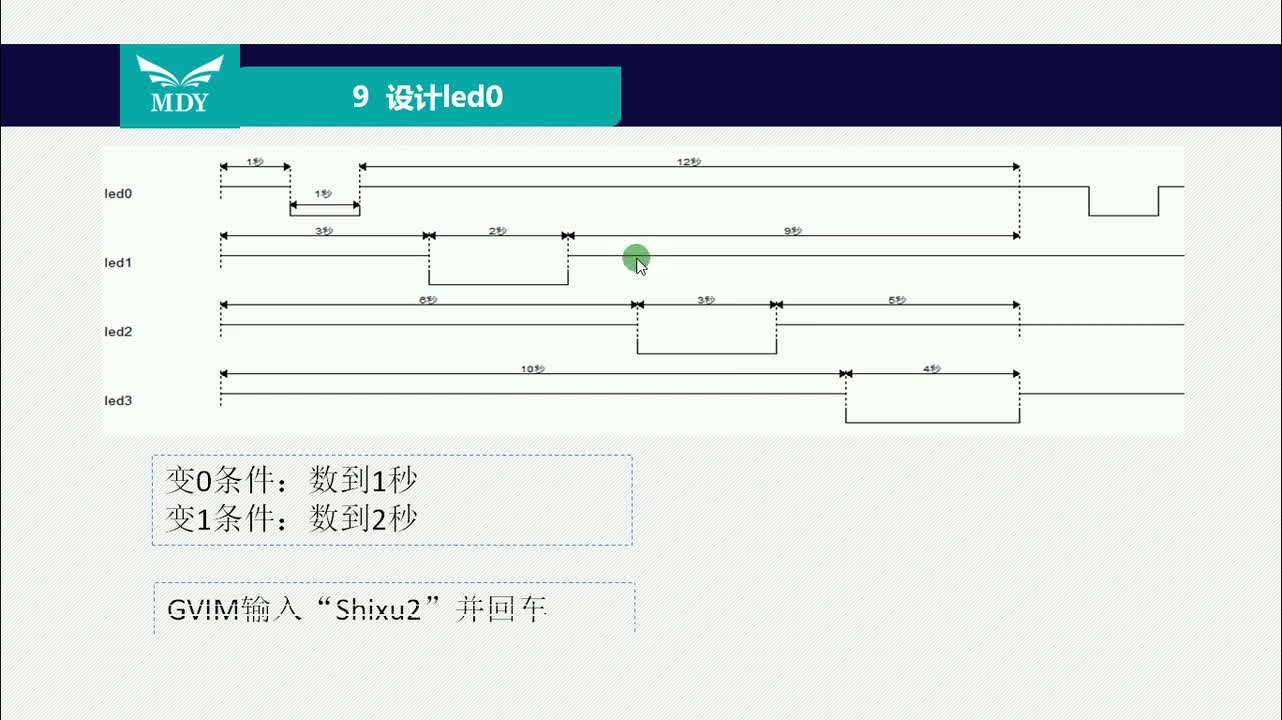

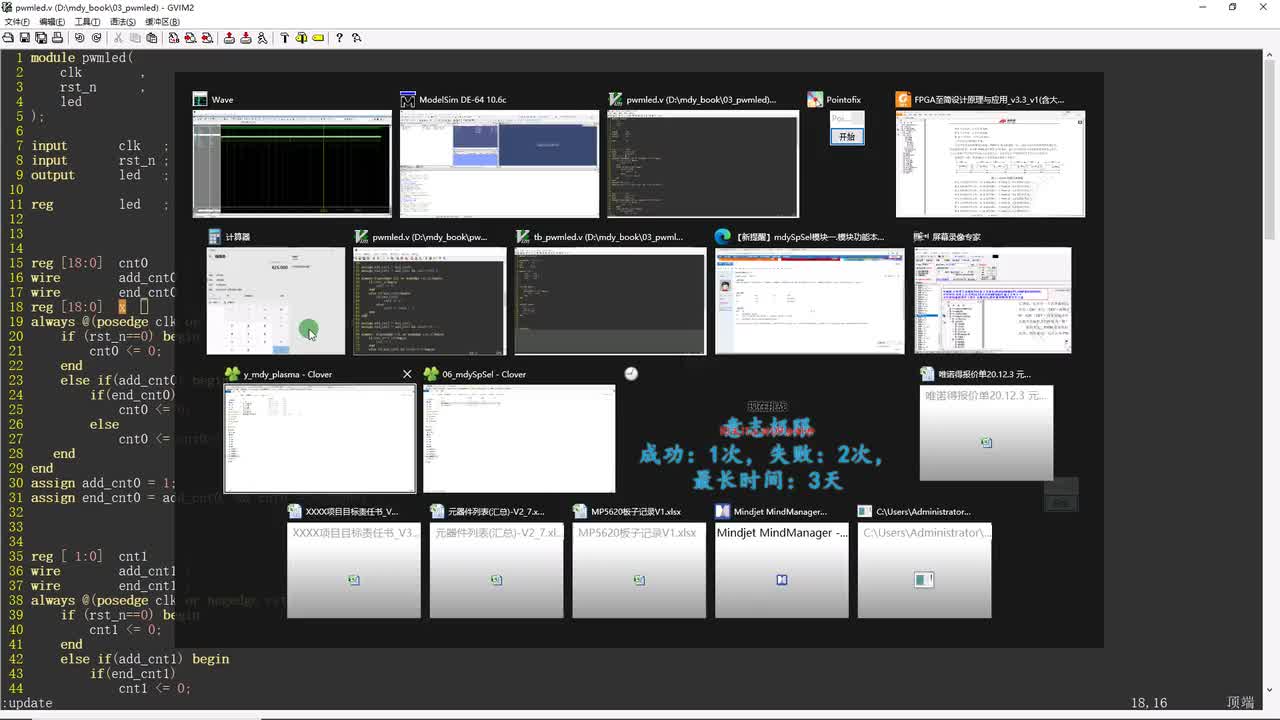

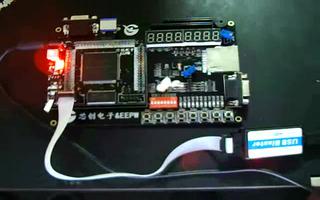

4位闪烁灯一、项目背景 LED灯的理论、教学板的原理图,已经在案例1位闪烁灯中有详细的描述,在此不再讲述,有兴趣的读者可以返回去阅读。 本工程使用4个LED灯---LED1~LED4,实现一个呼吸灯的功能。这4个灯具体的变化情况为: 第1个灯隔1秒后,亮1秒;然后第2个灯隔1秒后,亮2秒;然后第3个灯隔1秒后,亮3秒,最后第4个灯隔1秒,亮4秒。如此循环往复。 下面是波形图: 上板效果图如下图所示。 上板的演示视频,请登陆网址查看:。 我们先分析一下板子上的LED灯。每个LED灯都有一个信号来控制,该信号为0,则灯亮,如果该信号为1,则灯来。现在我们要控制4个LED灯亮灭,那就需要4个信号,假设分别为led0、led1、led2和led3。这4个信号分别连接到4个led灯上。如果要让LED0灯0亮,LED1~3灯来,那FPGA就让led0信号为0,led1~3信号都为1。 综上所述,我们这个工程需要6个信号:时钟clk,复位rst_n、led0、led1、led2和led3。 我们再分析一下功能需求,第1个灯隔1秒后,亮1秒;然后第2个灯隔1秒后,亮2秒;然后第3个灯隔1秒后,亮3秒,最后第4个灯隔1秒,亮4秒。如此循环往复。 上面的功能需求,也可以翻译成:对于LED0,复位后,先灭1秒,亮1秒,然后再灭12秒,循环往复;对于LED1,复位后,先灭3秒,亮2秒,然后再灭9秒,循环往复;对于LED2,复位后,先灭6秒,亮3秒,然后再灭5秒,循环往复;对于LED3,先灭10秒,亮4秒,循环往复。 再将其翻译成信号来理解: 复位后,让信号led0=1并持续1秒,然后让led0=0并持续1秒,然后让led0=1持续12秒。循环往复。 复位后,让信号led1=1并持续3秒,然后让led1=0并持续2秒,然后让led1=1持续9秒。循环往复。 复位后,让信号led2=1并持续6秒,然后让led2=0并持续3秒,然后让led2=1持续5秒。循环往复。 复位后,让信号led3=1并持续10秒,然后让led3=0并持续4秒。循环往复。 再将其翻译成波形如下图所示。 由图中可看到,信号led0~led3的变化单位最小是1秒,同时4个信号都是经过14秒后就循环一次。由至简设计法的思想,很容易就得出我们需要2个计数器,1个计数器用来计算1秒时间,另1个计数器用来计算14秒。有了这两个计数器,led0~led3的变化时间就有了标准。 我们用1个计数器用来计算1秒时间,该计数器名称为cnt0。本工程的工作时钟是50MHz,即周期为20ns,计数器计数到1_000_000_000/20=50_000_000个,我们就能知道1秒时间到了。该计数器是不停地计数,永远不停止的,可以认为加1条件一直有效,可写成:assignadd_cnt==1。综上所述,该计数器的代码如下。 我们再用1个计数器用来表示14秒,名称为cnt1。该计数器表示次数,自然是每隔1秒就加1,那就是end_cnt0。该计数器一共要数14次。所以代码为: 有了两个计数器,我们来思考输出信号led0的变化。概括起来,led0有两种变化点:变0和变1。变0的原因都是计数到1秒时间,也就是add_cnt1 &&cnt1==1-1时,led0变0。变1的原因,则是数到2秒时间时,即add_cnt1 &&cnt1==2-1时,led0变1。所以led0信号的代码如下: 接下来我们思考输出信号led1的变化。概括起来,led1有两种变化点:变0和变1。变0的原因都是计数到3秒时间,也就是add_cnt1 &&cnt1==3-1时,led1变0。变1的原因,则是数到5秒时间时,即add_cnt1 &&cnt1==5-1时,led1变1。所以led1信号的代码如下: 接下来我们思考输出信号led2的变化。概括起来,led2有两种变化点:变0和变1。变0的原因都是计数到6秒时间,也就是add_cnt1 &&cnt1==6-1时,led2变0。变1的原因,则是数到9秒时间时,即add_cnt1 &&cnt1==9-1时,led2变1。所以led2信号的代码如下: 接下来我们思考输出信号led3的变化。概括起来,led3有两种变化点:变0和变1。变0的原因都是计数到10秒时间,也就是add_cnt1 &&cnt1==10-1时,led3变0。变1的原因,则是数到14秒时间时,即add_cnt1 &&cnt1==14-1,也就是end_cnt1时,led3变1。所以led3信号的代码如下: 此次,主体程序已经完成。接下来是将module补充完整。 将module的名称定义为huxiled。并且我们已经知道该模块有六个信号:clk、rst_n、led0、led1、led2、led3。为此,代码如下: 其中clk、rst_n是输入信号,led0、led1、led2、led3是输出信号,并且六个信号都是1比特的,根据这些信息,我们补充输入输出端口定义。代码如下: 接下来定义信号类型。 cnt0是用always产生的信号,因此类型为reg。cnt0计数的最大值为500_000_000,需要用29根线表示,即位宽是29位。因此代码如下: add_cnt0和end_cnt0都是用assign方式设计的,因此类型为wire。并且其值是0或者1,1个线表示即可。因此代码如下: cnt1是用always产生的信号,因此类型为reg。cnt1计数的最大值为8,需要用4根线表示,即位宽是4位。因此代码如下: add_cnt1和end_cnt1都是用assign方式设计的,因此类型为wire。并且其值是0或者1,1根线表示即可。因此代码如下: led0、led1、led2、led3是用always方式设计的,因此类型为reg。并且其值是0或者1,1根线表示即可。因此代码如下: 至此,整个代码的设计工作已经完成。下一步是新建工程和上板查看现象。 首先在d盘中创建名为“huxiled”的工程文件夹,将写的代码命名为“huxiled.v”,顶层模块名为“huxiled”。 然后打开Quartus Ⅱ,点击File下拉列表中的New Project Wzard...新建工程选项。 3.再出现的界面中直接点击Next。 4.之后出现的是工程文件夹、工程名、顶层模块名设置界面。按照之前的命名进行填写,然后点击Next。

基于FPGA至简设计法的4位闪烁灯 附件更详细

相关推荐

热点推荐

16位复数乘法器 转发(内含代码 文档资料)

本帖最后由 taiyangyu_2 于 2017-4-14 15:16 编辑

明德扬首创全新FPGA设计技巧--至简设计法,教你如何一步一步去完成一个复杂电路的设计,里面很多有实用技巧,熟练

2017-04-12 19:39:43

4位闪烁灯设计就这么简单

4位闪烁灯设计1 项目背景LED灯的理论、教学板的原理图,已经在案例1位闪烁灯中有详细的描述,在此不再讲述,有兴趣的读者可以返回去阅读。2 设计目标本工程使用4个LED灯---LED1~LED4

2019-08-21 10:37:03

FPGA 1位闪烁灯设计

由FPGA独立控制。二、设计目标本工程使用1个LED灯---LED1,实现一个闪烁灯的功能。工程的工作时钟是50M,也就是时钟周期为20ns。当管脚AA4输出低电平时,LED1灯亮,输出高电平

2018-09-21 13:20:12

FPGA至简设计法为什么这么简单

由潘文明先生开创的IC/FPGA至简设计法,具备划时代的意义。这种设计方法不仅将IC/FPGA学习难度降到了最低,同时将设计过程变得简单,并规范了代码避免了混乱,将出错几率降到最低。下面我们来看

2017-12-15 15:10:57

FPGA至简设计法高效设计

本帖最后由 Stark扬 于 2018-9-26 16:52 编辑

至简设计法高效设计我们描述了明德扬的通用设计方法。在阐述案例过程中,我们画出了大量的波形图。有读者可能会问,在工作中,我们

2018-09-20 10:44:18

FPGA至简设计法高效设计[1241003385]

至简设计法高效设计上一节我们描述了明德扬的通用设计方法。在阐述案例过程中,我们画出了大量的波形图。有读者可能会问,在工作中,我们是不是也需要先大量地画波形图,再来写代码呢?不是的!工作中,我们要

2018-09-20 09:09:27

FPGA至简设计法案例2

FPGA至简设计法案例2例2. 当收到en=1后,dout间隔3个时钟后,产生宽度为2个时钟周期的高电平脉冲。 如上面波形图所示,在第3个时钟上升沿看到en==1,间隔3个时钟后,dout变1,再过

2019-08-01 09:58:24

FPGA至简设计法案例4

FPGA至简设计法案例4至简设计法经典案例4 案例4. 当收到en=1时,dout间隔1个时钟后,产生2个时钟周期的高电平脉冲,并且重复3次。上面波形图显示了描述的功能。第3个时钟上升沿收到en

2019-08-02 08:47:47

FPGA至简设计法经典案例

设计法在微观上,则制定得实用的规范。详细到,要不要添加信号;怎么添加信号;添加信号的名字规范等,我们都做了详细的规定。下面我们用4个经典例子,讲述了至简设计法的使用技巧。其他复杂功能,无论怎么变,都是这

2018-09-14 10:18:01

至简设计法之OV7670图像采集

本帖最后由 chunfen2634 于 2017-7-21 09:43 编辑

至简设计法之OV7670图像采集题目实现摄像头OV7670的配置及完成图像的采集。请读者考虑实现该功能需要哪些模块

2017-07-11 11:00:48

至简设计法完成数字时钟设计

,其风格也是五花八门,第一感觉是貌似能看懂,但就是不知道怎么设计出来的。其实如果有正确的设计思路和方法,其实现起来是非常简单的。下面我们就核心的数字模块为例,讲解如何使用至简设计法来实现。数字模块的功能

2020-02-22 18:17:23

至简设计原理与应用目录

至简设计原理与应用目录简介: 本书收集整理了作者在FPGA项目实践中的经验点滴。既有常用FPGA设计技巧;也有多个项目案例分析,小到闪烁灯,大到边缘检测,AD采集等项目,并且这些案例大都以特定

2019-07-24 12:00:04

至简设计法经典案例

制定得实用的规范。详细到,要不要添加信号;怎么添加信号;添加信号的名字规范等,我们都做了详细的规定。下面我们用4个经典例子,讲述了至简设计法的使用技巧。其他复杂功能,无论怎么变,都是这4个经典案例的变种

2019-07-31 17:17:27

FFT至简设计法实现法_FFT算法_蝶形运算_fpga

DIT-FFT至简设计实现法工程说明本设计讨论的是基于至简设计法实现按时间抽选的基2-FFT算法(即DIF-FFT)实现过程,支持N由8到1024。案例补充说明本案例无论是模块划分、计数器设计、还是

2017-08-02 17:32:27

《FPGA至简设计原理与应用》FPGA学习笔记——4位闪烁灯设计

《FPGA至简设计原理与应用》学习笔记——4位闪烁灯设计作者:一条咸鱼 本文为明德扬原创及录用文章,转载请注明出处!个人感想:本文首先分析了至简设计法案例—4位闪烁灯,然后通过该案例举一反三,实现了

2020-04-24 14:08:18

《FPGA至简设计原理与应用》学习笔记——1位闪烁灯设计

《FPGA至简设计原理与应用》学习笔记——1位闪烁灯设计 作者:一条咸鱼 个人总结及感悟:对于学习本案例,首先要理解案例的顶层框架,再是理解框架下面的逻辑,最后才是理解代码。这一点对于自己动手写代码

2020-04-15 11:35:54

【至简设计案例系列】基于FPGA的密码锁(XILINX ISE版)

至简案例系列:密码锁作者:造就狂野青春本文为明德扬原创及录用文章,转载请注明出处!一、总体设计1.概述 本文基于明德扬至简设计法和明德扬设计规范,设计了一个基于FPGA的数字密码锁,实现了在拨码开关

2020-04-24 14:40:00

【至简设计案例系列】基于FPGA的频率、电压测量

本文为明德扬原创及录用文章,转载请注明出处!一、总体设计1.概述本文基于明德扬至简设计法和明德扬设计规范,设计了一个基于FPGA的频率、电压测量仪器,实现了测量AD采集后的波形频率和电压(峰峰

2020-04-23 10:52:07

【教程】看完就懂!运用至简设计法进行呼吸灯设计

怎样控制led灯亮的频率呢?通过控制led灯亮的时间长度。Q3:怎样控制灯亮的时间?通过计数FPGA的时钟个数。Q4:该怎样计数FPGA的时钟个数?本设计的基本思想:我们让led灯在1s内由暗慢慢

2019-12-19 11:07:02

【明德扬】倾情分享海量FPGA设计技巧学习资料 转

的毕业设计题目,看看如何使用至简设计法来设计数字时钟。4.至简设计法中的四段式状态机现在流行的状态机设计,一般可分为一段式、两段式和三段式,然而我们明德扬却发明了四段式状态机,并制定了一些规则,从此设计再不

2017-03-27 19:20:53

【每周FPGA案例】至简设计法-电子密码锁

。基于明德扬至简设计法和明德扬设计规范,设计一个基于FPGA的密码锁、并将数值显示在数码管上,然后根据输入的键值判断密码是否正确。1.1.2 设计目标实现电子密码锁的功能,具体功能要求如下:1. 密码4位

2020-09-25 09:55:32

【每周FPGA案例】至简设计系列_基于FPGA的测距系统

概述学习了明德扬至简设计法和明德扬设计规范,本人用FPGA设计了一个测距系统。该系统采用超声波进行测量距离再在数码管上显示。在本案例的设计过程中包括了超声波的驱动、三线式数码管显示等技术。经过逐步改进

2020-08-19 21:50:19

【潘文明至简设计法】FPGA学习资料汇总,免费下载

` 本帖最后由 chunfen2634 于 2017-6-29 15:27 编辑

大家好,这里潘老师将精心录制和编辑的fpga学习系列教程——《至简设计法视频教程》分享给大家。教程充分考虑0

2017-06-29 15:19:35

【潘文明至简设计法】系列教程 GVIM视频教程

。明德扬的模板,包含了至简设计法的计数器、状态机、FIFO和模块结构等,这些是RTL代码最常见的部分。使用这些模板的时候,工程师只需按顺序填空,就能快速地进行设计,可节省大量时间。本视频介绍了明德扬

2017-06-15 11:22:29

华为内部资料:FPGA设计高级技巧(altera篇)以及代码书写规范

明德扬首创全新FPGA设计技巧--至简设计法,教你如何一步一步去完成一个复杂电路的设计,里面很多有实用技巧,熟练运用这些技巧,有助于你写出非常优秀的代码。例:4位流水线乘法器,例子采用了明德扬至简设计法中的方法技巧,非常简洁易读,欢迎比较![qq]3225224637[/qq]

2017-04-10 19:02:15

基于FPGA至简设计法的4位闪烁灯

4位闪烁灯一、项目背景LED灯的理论、教学板的原理图,已经在案例1位闪烁灯中有详细的描述,在此不再讲述,有兴趣的读者可以返回去阅读。二、设计目标本工程使用4个LED灯---LED1~LED4,实现一

2019-08-06 09:02:27

基于FPGA至简设计法的4位闪烁灯 附件更详细

4位闪烁灯一、项目背景LED灯的理论、教学板的原理图,已经在案例1位闪烁灯中有详细的描述,在此不再讲述,有兴趣的读者可以返回去阅读。 二、设计目标本工程使用4个LED灯---LED1~LED4,实现

2018-09-26 09:48:03

基于至简设计法实现的PWM调制verilog

明德扬分享的调制PWM驱动LED工程,利用脉冲宽度调制调制出几个不同宽度的脉冲来驱动LED灯,添加verilog文件即可使用。基于至简设计法实现的PWM调制verilog.rar (281.92 KB )

2019-01-18 06:35:18

基于至简设计法实现的闹钟工程

`本案例:明德扬首创全新FPGA设计技巧--至简设计法,教你如何一步一步去完成一个复杂电路的设计,里面很多有实用技巧,熟练运用这些技巧,有助于你写出非常优秀的FPGA设计代码。非常简洁易读,欢迎比较

2019-07-31 08:51:28

基于至简设计法的数字时钟设计

就是不知道怎么设计出来的。其实如果有正确的设计思路和方法,其实现起来是非常简单的。下面我们就核心的数字模块为例,讲解如何使用至简设计法来实现。 数字模块的功能,是产生6个信号,分别表示时十位、时个位

2017-02-15 17:32:23

基于至简设计法的数字时钟设计

模块为例,讲解如何使用至简设计法来实现。数字模块的功能,是产生6个信号,分别表示时十位、时个位、分十位、分个位、秒十位和秒个位的值。例如上述信号值依次为2、1、4、3、5、9时,则表示时间为21点43分

2019-07-24 09:54:17

明德扬FPGA项目实践1位闪烁灯设计

低电平时,LED7灯为暗。8个LED灯都可由FPGA独立控制。2设计目标本工程使用1个LED灯---LED1,实现一个闪烁灯的功能。工程的工作时钟是50M,也就是时钟周期为20ns。当管脚AA4输出低电平

2018-11-07 09:25:38

明德扬至简设计法原理与应用1.1FPGA简介

LUT可以看成一个有4位地址线的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入RAM,这样,每输入一个信号

2018-11-12 15:11:39

明德扬至简设计法资料大全

/id_XMjg3NjYyMDY1Ng==.html?spm=a2hzp.8253869.0.0明德扬 至简设计法教程FPGA定位问题案例4http://v.youku.com/v_show

2017-07-27 17:05:14

明德扬至简设计原理资料包(官方原版)

本帖最后由 W陈老师 于 2022-3-3 10:13 编辑

潘文明至简设计法,是以发明者名字命名的FPGA设计方法,综合采用多种科学、严谨的方法,将整个设计过程规范化,实现“至简”设计。其

2022-02-18 15:30:26

明德扬独创“至简设计法”介绍

潘文明至简设计法介绍潘文明至简设计法,是以发明者名字命名的FPGA设计方法,综合采用多种科学、严谨的方法,将整个设计过程规范化,实现“至简”设计。其专著《手把手教你FPGA》2017年由北京航天

2019-07-25 16:50:44

潘文明至简设计法之SPI接口至简代码设计

本帖最后由 chunfen2634 于 2017-6-22 14:31 编辑

我们的至简设计法,综合了运用多种科学、严谨的代码设计方法,将整个设计过程完整化、规范化,令学习方法至简、设计过程至

2017-06-22 10:20:39

潘文明至简设计法系列教程-Verilog快速掌握新版简介

使用的过程中容易犯一些错误。明德扬至简设计法由拥有多年FPGA代码编写经验的潘文明老师首创,不仅能让初学者在短时间内掌握Verilog语言,而且编写出的代码简洁无冗余、准确度高。我们将通过一系列

2017-06-12 11:58:50

用至简设计法进行PWM流水灯设计

本帖最后由 chunfen2634 于 2017-7-7 10:09 编辑

《用至简设计法进行PWM流水灯设计》脉冲宽度调制(pulse width modelation)简称PWM,利用

2017-07-06 10:25:51

用至简设计法进行PWM流水灯设计

波形图 一个周期为10ms,高电平为6ms,低电平时间为4ms的PWM,其占空比(高电平时间占整个周期的比例)为60%。 明德扬的FPGA开发板共有8个LED灯。产生8个管脚的PWM图,如图2-8所示

2019-07-26 14:15:16

转【明德扬FPGA学习指南】至简设计法之串行结构的FIR滤波器设计

各位童鞋,明德扬的革命性的FPGA设计方法----至简设计法,已经正式推出了。至简设计法,是明德扬培训时重点培训的内容,设计FPGA不用再盲目设计、反复修改,而是有思路、有步骤,争取一次性就设计正确

2017-05-23 10:11:26

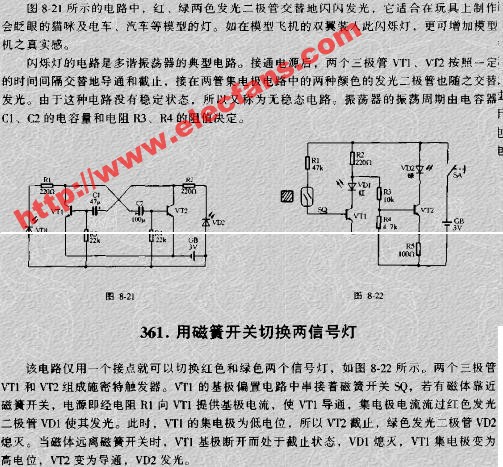

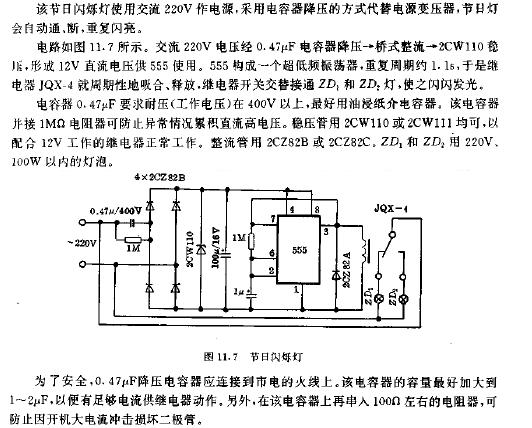

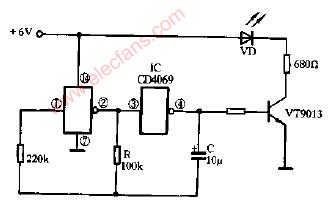

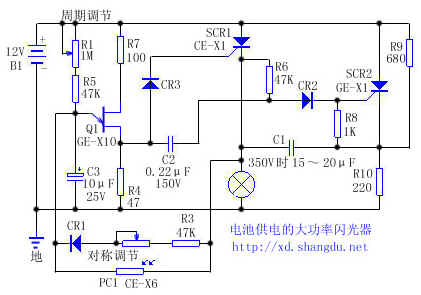

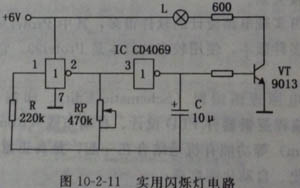

LED闪烁灯制作教程

本文将介绍LED闪烁灯,分为单组闪烁、两组交替闪烁和三组循环闪烁等类型。还介绍了单组闪烁灯电路、两组交替闪烁灯电路、三组循环闪烁灯电路图详解。

2018-02-22 11:02:00 26655

26655

26655

26655

最全关于关灯LED微亮和节能灯闪烁的问题分析

本文首先介绍了LED的原理与LED灯特点,其次介绍了节能灯原理,最后详细介绍了关于关灯LED微亮和节能灯闪烁的问题分析。

2018-05-18 11:20:18 14347

14347

14347

14347FPGA1位闪烁灯设计[1241003385]

1位闪烁灯设计 一、项目背景 LED(Light Emitting Diode),发光二极管,是一种能够将电能转化为可见光的固态的半导体器件,它可以直接把电转化为光。LED的心脏是一个半导体的晶片

2018-09-23 17:42:01 810

810

810

810LED灯闪烁是怎么回事

使用LED等是家家户户的选择,然而也有的人在安装LED等之后,灯就会不停的闪烁。在晚上的时候,就会觉得比较吓人,那么LED灯闪烁是什么原因呢?想要解决闪烁的问题,就一定要找对原因,才可以彻底的改善。下面就给大家介绍一下LED灯闪烁的原因吧。

2018-12-31 15:16:00 20419

20419

20419

20419基于FPGA至简设计法的4位闪烁灯

4位闪烁灯一、项目背景LED灯的理论、教学板的原理图,已经在案例1位闪烁灯中有详细的描述,在此不再讲述,有兴趣的读者可以返回去阅读。 二、设计目标本工程使用4个LED灯---LED1~LED4,实现

2019-01-10 11:26:54 498

498

498

498至简设计法:程序设计(2)

由潘文明先生开创的IC/FPGA至简设计法,具备划时代的意义。这种设计方法不仅将IC/FPGA学习难度降到了最低,同时将设计过程变得简单,并规范了代码避免了混乱,将出错几率降到最低。

2019-11-27 07:00:00 1471

1471

1471

1471至简设计法:运算符(3)

明德扬至简设计法,提取大量的实际项目,采用科学的手段统计分析,找出其内在通用性部分,并建立相关的体系,实现了“填空式”设计!首先,把复杂的代码划分成几种类型的模块,然后以统一规范的代码格式,通过相应的脚本语言建立可调用的通用模板。不仅如此,通过模板生成的代码可参数化定制,一旦生成无需修改。

2019-11-27 07:02:00 1514

1514

1514

1514LED灯闪烁的原因 LED灯闪烁故障解决方法

的疲劳和不适。然而,要解决LED灯的闪烁问题,并不是一件非常困难的事情。下面我将详细阐述LED灯闪烁的原因以及解决方法。 首先,我们来探讨一下LED灯闪烁的原因。LED灯闪烁可能有多种原因,下面我将主要介绍三种常见的原因。 第一,电流不稳定。

2023-12-11 15:31:23 55121

55121

55121

55121 电子发烧友App

电子发烧友App

评论