由于FPGA技术和ARM技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA并行总线显得尤为重要。本文设计的FPGA的ARM外部并行总线接口,满足了总线的时序要求,并在某航空机载雷达应答机中进行了应用.

2013-08-15 10:44:19 7204

7204

具有现场可编程能力,即使产品已经投入市场,也可根据特殊应用重新配置硬件; b)FPGA具有强大的并行处理能力; c)

2020-12-17 12:58:21 4094

4094 InTime。 前言 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着从 C 转化得到 RTL 基本不可能。其实,使用 FPGA 工具设置来优化设计可以最

2020-12-20 11:46:46 1416

1416

HLS 优化设计的最关键指令有两个:一个是流水线 (pipeline) 指令,一个是数据流(dataflow) 指令。正确地使用好这两个指令能够增强算法地并行性,提升吞吐量,降低延迟但是需要遵循一定

2021-01-08 10:26:01 7882

7882 虽然 FPGA 可使用 Verilog 或 VHDL 等低层次硬件描述语言 (HDL) 来编程,但现在已有多种高层次综合 (HLS) 工具可以采用以 C/C++ 之类的更高层次的语言编写的算法描述

2022-10-12 15:06:47 968

968 HLS任务级编程第一篇文章可看这里: HLS之任务级并行编程 HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。对于控制驱动

2023-07-27 09:22:10 732

732

HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。

2023-07-27 09:21:40 579

579

(HLS) 的帮助下,基于 C 语言的语言现在可用于 FPGA 设计。具体来说,AMD Vivado™ HLS 编译器提供的编程环境能够与标准处理器及专用处理器共享关键技术,用于优化 C 语言程序

2023-06-28 18:18:57

的物理管脚输出,同时还需保持设计的电气完整性。FPGA 复杂度增加也需要高级合成技术,如此才能更快达到时序收敛,最大程度地减少设计变更的影响以及解决特定应用要求。通过使用可选的 FPGA-PCB 优化技术

2018-09-20 11:11:16

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或 Block

2022-09-07 15:21:54

连接器)。外部以太网链路可以连接到任何交换层次结构。Suchconfiguration可以进行优化,以大规模实现textra大型模型并行性,并可以轻松处理数据并行性或模型和数据并行性的组合。

GAUDI

2023-08-04 06:06:14

利用所有可能的数据通信方式-没有功能概述,也没有对用户代码进行优化转换-支持代码报告得太晚了-在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测

2021-07-10 08:00:00

`fpga基础篇(二):三大并行结构最近小编比较忙,所以这期给大家介绍一个基础篇,比较简单,但却是FPGA编程的基础。我们知道FPGA与单片机最大的区别就是FPGA是并行执行的,而单片机是串行的,说

2017-04-13 10:23:27

的可编程性使得硬件设计变得更加灵活和可定制,缩短了设计周期,提高了设计效率;其次,FPGA的可重构性使得硬件系统可以随时进行升级和优化,无需更换硬件设备;此外,FPGA的并行处理能力和性能优势也使其成为一种

2023-11-13 15:43:00

并行编程模型是并行计算,尤其是并行软件的基础,也是并行硬件系统的导向,在面临多核新挑战的情况下,什么样的并行编程模型在未来能成为主流,还很难说。至少到目前,还处于百家争鸣的时代,很多模型提出,很多在应用,下面我们简单介绍一下当前的并行编程模型现状。

2019-07-11 08:03:33

;j++) {

b = 2;

}

}

由于这条指令的应用条件十分苛刻,因此很少使用。一般直接通过代码重构的方式对连续循环进行优化。

参考文档

官方vitis-hls的ug1399文档

FPGA并行编程

【流水线】FPGA中流水线的原因和方法

2023-12-31 21:20:08

编译和编程下载,这被称为数字逻辑电路的高层次设计方法。 作为现代电子系统设计的主导技术,EDA具有两个明显特征:即并行工程(Concurrent Engineering)设计和自顶向下

2008-06-26 16:16:11

,place and route)、仿真及特定目标芯片的适配编译和编程下载,这被称为数字逻辑电路的高层次设计方法。---作为现代电子系统设计的主导技术,eda具有两个明显特征:即并行工程(concurrent

2013-09-02 15:19:20

,Place And Route)、仿真及特定目标芯片的适配编译和编程下载,这被称为数字逻辑电路的高层次设计方法。---作为现代电子系统设计的主导技术,EDA具有两个明显特征:即并行工程(Concurrent

2008-06-27 10:26:34

Linux平台上如何进行通用计算并行优化

2021-03-12 07:43:40

资源。近年来,优化技术没有发生显著变化,但应用领域却以显著的速度迅速发展。在专业实践中成功嵌入优化的使用至少需要三个先决条件。它们包括设计问题的数学建模、计算机编程知识和优化技术知识。现在有许多特殊

2023-09-21 07:07:10

应用与生俱来的异构特性,使其需要软硬件相结合的实现方案。Vivado HLS视频库能加快OpenCV函数向FPGA可编程架构的映射。

2021-07-08 08:30:00

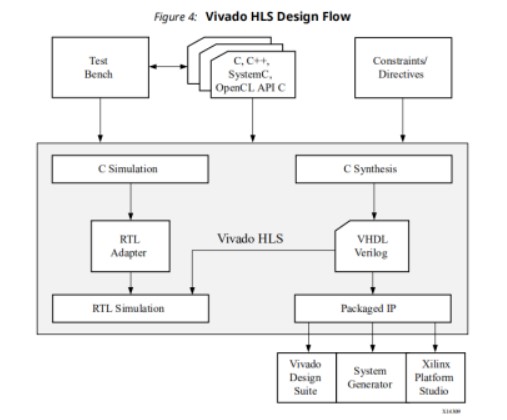

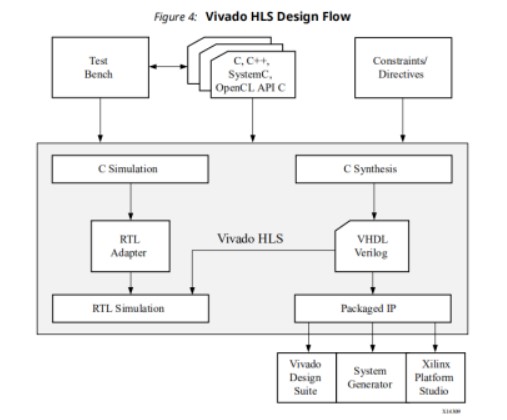

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

fpga的硬件换成我们自己的arm设备。不过经过研究这种设想不可行。个人看法,也许不对哦。!!!!arm是一款多核心,单进程处理器,目前为止arm处理器都不支持多线程。所以多线程概念不能将并行计算优化

2015-12-30 14:33:38

正在改变FPGA编程的方式,其中的新兴技术能够将图形化程序框图、甚至是C代码转换成数字硬件电路。各行各业纷纷采用FPGA芯片是源于FPGA融合了ASIC和基于处理器的系统的最大优势。 FPGA能够提供

2019-04-28 10:04:13

利用所有可能的数据通信方式-没有功能概述,也没有对用户代码进行优化转换-支持代码报告得太晚了-在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测

2021-07-06 08:00:00

Virtual Cable)调试FPGA逻辑

三、硬件加速之—使用PL加速FFT运算(Vivado)

四、硬件加速之—使用PL加速矩阵乘法运算(Vitis HLS)

后四期测评计划:

五、Vitis AI

2023-10-13 20:11:51

主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx推出的Vivado HLS工具可以直接使用C、C++或System C来对Xilinx系列的FPGA进行编程,从而提高抽象的层级

2020-10-10 16:44:42

HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或

2022-09-09 16:45:27

的时候,他们必须理解不断进步的技术,如多核处理器、现场可编程门阵列(FPGA)和高速数据总线,如PCI Express等等。通过将这些技术与NI LabVIEW并行化编程软件及NI TestStand

2014-12-12 16:02:30

复杂可编程逻辑器件—FPGA技术在近几年的电子设计中应用越来越广泛。FPGA具有的硬件逻辑可编程性、大容量、高速、内嵌存储阵列等特点使其特别适合于高速数据采集、复杂控制逻辑、精确时序逻辑等场合的应用。而应用FPGA中的存储功能目前还是一个较新的技术。

2019-10-12 07:32:24

其在设计思路和编程风格等方面也存在差异,这些差异会对系统综合后的电路整体性能产生重要的影响。在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源

2019-06-18 07:45:03

将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架对Xilinx可编程逻辑器件进行开发,可加速算法开发的进程,缩短产品上市时间。HLS基本开发流程如下:(1) HLS工程新建/工程

2021-02-19 18:36:48

多核技术下的并行编程模式课程议程多核时代所带来的优势与挑战化繁为简——多核编程的趋势LabVIEW并行编程模式[hide]多核技术下的并行编程模式.pdf[/hide][此贴子已经被作者于2009-12-16 9:21:54编辑过]

2009-12-16 09:21:39

我正在设计一个子板,上面有40个Artix 7(AC7A12T)设备。每台设备都应具有相同的图像。我不是一次编程链1中的每个器件的串行链,而是希望并行执行任务,以便所有FPGA同时进行编程。我似乎

2020-05-14 07:01:03

介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现方法,给出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC进行直接数字频率合成的VHDL源程序。

2021-04-30 06:29:00

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

了不缺钱。soc,架构开发等后面会提到。3.FPGA:就是硬件编程,入门很简单,做深很难,要对时序有非常深的理解和大量的项目开发经验,就算你做的特别好,前景还是不明确。FPGA近年的一大热门就是软件

2021-04-28 17:06:03

相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。Synphony HLS解决方案架构图

2019-08-13 08:21:49

和生成比特流以对FPGA进行编程4 - 将比特流导入并阻塞到SDK中,基于此生成板级支持包(BSP)并与Zedboard连接。顺便说一下,SDK的目标是成为我在Vivado HLS中的测试平台吗?即在计算机中观察Zedboard产生的结果是否为例外情况。

2020-03-24 08:37:03

的出现,并行设计和创新在硬件开发中成为可能,对所有企业,无论大或小,FPGA 的使用将变得越来越便宜和现实,也会得到越来越多的应用。业界对它的使用仍然停留在起步阶段,但随着使用量的增加,FPGA 将让每个企业,无论是单人初创企业还是已经成立的跨国企业,都可以利用高性能并行计算来持续推动技术创新。

2017-12-15 09:09:32

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

,在单芯片上提供了软/硬件和I/O可编程性。Zynq SoC在单个器件中集成了一个ARM®双核Cortex™-A9 MPCore™处理系统、FPGA逻辑和一些关键外设。这样,该器件就能帮助设计人员实现

2014-04-21 15:49:33

并行设计架构是如何构成的?请问并行设计技术有哪些应用?

2021-04-26 06:16:05

的生命周期。第二个原因是速度。微控制器只能按顺序一次执行一条指令。由于硬件特性,FPGA 结构本身是并行的。因此它能同时执行多个指令,这对于 FFT 或图形处理等操作非常有用,因为在按顺序执行的处理器上

2018-10-31 11:33:29

,目前主流的异构并行计算平台是X86+GPU(Graphics Processing Unit,图形处理器)和X86+FPGA(Field-Programmable Gate Array,现场可编程

2017-09-25 10:06:29

的文章将适合HLS加速的应用场景出发,重点讲解数据传输的架构优化以及如何编写高效的硬件描述C代码。 写在最后: “为现场可编程门阵列的高层次综合建立的算法基础”曾获IEEE计算机分会年度技术成就奖

2021-01-06 17:52:14

可扩展并行计算技术、结构与编程

2006-03-25 16:43:55 61

61 并行硬件技术概览:多处理器、超线程、双核、多核与FPGA 1-2多线程与多任务的区别 3-5借助LabVIEW应对多核编程的挑战 6-9升级至多核后,我的LabVIEW程序是否能更快地运行? 10-

2010-07-01 10:43:29 0

0 说明:适用于没用烧写ATmega8并行编程器的朋友,初用ATmega8的工程师常常在串行编程时写错熔丝位,及加密位,造成不能再串行编程的不便,没并行编程将无法再使用,本人就是因此

2010-07-16 13:04:07 97

97 本文提出了如何实现在硬件上直接对信号做并行处理,比如测量波形周期、占空比、滤波等;并提出了如何优化FPGA资源。运用NI FPGA提供的可重配置测量I接口技术和可控制底层硬件的

2010-07-17 17:57:07 21

21 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

供的数据类型,直接用HLS翻译成硬件的话,可能会造成硬件效率的下降。 举一个常见的例子。在xilinx FPGA中普遍含有DSP48,它可以提供18x18bit的乘法器,假如你的设计只需要17bit的乘法器,那么从FPGA实现角度,只需要1个DSP48就够了。但是由于标准C没有提供17bit的数据类型,

2017-02-08 02:50:11 637

637

相信通过前面5篇fir滤波器的实现和优化过程,大家对HLS已经有了基本的认识。是时候提炼一些HLS的基本概念了。 HLS支持C,C++,和SystemC作为输入,输出为Verilog(2001

2017-02-08 05:23:11 674

674

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 1961

1961

本实验练习使用的设计是实验1并对它进行优化。 步骤1:创建新项目 1.打开Vivado HLS 命令提示符 a.在windows系统中,采用Start>All Programs>Xilinx

2017-02-09 05:07:11 411

411

本文介绍了FPGA电源设计并行工程的合理性,讲解了并行工程(CE)技术及其作用,讨论了FPGA电源系统设计的复杂性和不确定性。

2017-10-13 13:00:35 5

5 DSP并行系统的并行粒子群优化目标跟踪

2017-10-20 10:54:00 6

6 在使用高层次综合,创造高质量的RTL设计时,一个重要部分就是对C代码进行优化。Vivado Hls总是试图最小化loop和function的latency,为了实现这一点,它在loop

2017-11-16 14:44:58 3362

3362 NI LabVIEW图形化编程方法不仅省时,还很适合对多核处理器和其他并行硬件[如:现场可编程门阵列(FPGA)]进行编程。 其中一项优势是:通过2个、4个或更多核将应用程序自动扩展至CPU,通常

2017-11-16 19:30:41 1287

1287

针对大容量固态存储器中数据错“位”的问题,目前大多采用软件ECC 模型进行检错和纠错,但这势必会极大地影响存储系统的读写性能。基于ECC校验原理,提出一种并行硬件ECC 模型,并采用FPGA 实现。仿真分析和实验结果表明:该模型不仅具有良好的纠错能力,而且显著地提高了存储系统的读写性能。

2017-11-18 10:32:51 5228

5228

Vviado-HLS基于Xilinx FPGA对C的解析,综合原理。Vivado-HLS FPGA并行与处理器架构 与处理器架构相比,FPGA结构具有更高的并行。Vivado-HLS对软件C程序编译时与处理器编译是不一样的执行机制。

2017-11-18 12:23:09 2377

2377

(COTS)计算机集群的日益普及。 直至最近,尚无商业高级工具可以支持针对高性能系统的科学计算应用程序的开发。并行编程是一门深奥的技术,只有那些旨在通过利用自定义设置和低级库以及通过为特定硬件调优应用程序,来实现最高性能

2017-12-02 09:49:13 280

280

为应对大数据时代中组合优化问题的求解,基于云计算框架Spark,借助其基于内存、分布式的特定,提出一种并行蚁群优化算法。其思路是通过将蚂蚁构造为弹性分布式数据集,由此给出相应的一系列转换算予,实现

2018-01-02 14:11:58 0

0 HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

2018-06-04 01:43:00 7171

7171

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS为FPGA流程提供集成化设计与开发环境,率先支持5G无线应用。

2018-08-30 10:09:32 7368

7368 有效并行缩减和扩展并行性的编程技术。

2018-11-01 06:24:00 1933

1933 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着

2018-12-16 11:19:28 1435

1435

我们将继续介绍 Vivado HLS 所支持的 “for循环” 的优化方法。在默认情况下,Vivado HLS 并不会对顺序执行的 for 循环优化为并行执行,LOOP_MERGE 约束提供了这样一种可能:for 循环并行执行。本讲结合案例介绍了循环合并的三个主要规则。

2019-08-01 16:59:21 2567

2567 RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构。Xilinx官方文档表示利用HLS进行设计可以大大加速设计进度:

2019-07-31 09:45:17 6232

6232

应用能够有更高的性能,您需要熟悉如下介绍的硬件。另外,将会介绍编译优化选项,有助于将您的 OpenCL 应用更好的实现 RTL 的转换和映射,并部署到 FPGA 上执行。

2020-07-16 17:58:28 6015

6015

Unroll 指令在 for 循环的代码区域进行优化,这个指令不包含流水线执行的概念,单纯地将循环体展开使用更多地硬件资源实现,保证并行循环体在调度地过程中是彼此独立的。

2021-01-14 09:41:31 2343

2343 HLS 优化设计的最关键指令有两个:一个是流水线 (pipeline) 指令,一个是数据流(dataflow) 指令。正确地使用好这两个指令能够增强算法地并行性,提升吞吐量,降低延迟但是需要遵循一定的代码风格。

2021-02-01 06:28:14 7

7 提出了一种基于FPGA实现的全并行结构FFT设计方法,采用XILINX公司最新器件VirtexII Pro,用硬件描述语言VHDL和图形输入相结合的方法,在ISE6.1中完成设计的输入、综合、编译

2021-03-31 15:22:00 11

11 本系列教程演示如何使用xilinx的HLS工具进行算法的硬件加速。

2021-06-17 10:20:33 5489

5489

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和并行DAC芯片。

2022-04-21 08:55:22 5774

5774 FPGA的布局布线软件向来跑得很慢。事实上,FPGA供应商已经花了很大的精力使其设计软件在多核处理器上运行得更快。

2022-05-25 09:50:10 959

959 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

基于硬件描述语言HDL,抽象出HLS(High-Level Synthesis)(翻译为高层次综合?怎么听起来都沉得别扭)技术,通过高层设计去隐藏很多底层逻辑和细节,让FPGA的开发更加简单。

2022-09-05 09:12:48 704

704 软件编译器讲高级语言翻译成为机器语言。主要关注的语言的语法转换规则,相比之下,HLS 的翻译难度更大一些,模块中的语句形式上是前后顺序排列。但是HLS尽力转换成为并行执执行的硬件逻辑。

2022-10-10 14:50:29 1240

1240 电子发烧友网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 中来实现,无缝的将硬件仿真环境集合在一起,使用软件为中心的工具、报告以及优化设计,很容易的在 FPGA 传统的设计工具中生成 IP。 传统的 FPGA 开发,首先写 HDL 代码,然后做行为仿真,最后做综合

2022-12-02 12:30:02 2570

2570 对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

2022-12-29 14:46:14 928

928 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 1

1 软硬件工程之间的界限比我们看到的更模糊。称之为现场可编程门阵列 (FPGA) 的器件,其物理属性可通过使用硬件描述语言 (HDL) 来操控,该器件可在软硬件编程之间架起一座桥梁。 但人们通常认为

2023-07-04 08:35:01 1512

1512

本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS 工具生成的在 FPGA 部分执行的硬件功能模块。

2023-08-04 11:00:43 335

335

电子发烧友网站提供《Vitis HLS:使用任务级并行性的高性能设计.pdf》资料免费下载

2023-09-13 17:21:04 0

0 电子发烧友网站提供《基于FPGA的ARM并行总线设计原理.pdf》资料免费下载

2023-10-10 09:31:31 0

0 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0 AMD Vitis 高层次综合 ( HLS ) 已成为自适应 SoC 及 FPGA 产品设计领域的一项颠覆性技术,可在创建定制硬件设计时实现更高层次的抽象并提高生产力。Vitis HLS 通过

2023-12-05 09:10:14 190

190

FPGA(Field-Programmable Gate Array)是一种可编程逻辑技术,它使用可重构的硬件单元(如门阵列和查找表)来实现电路功能。相比传统的专用集成电路(ASIC),FPGA具有

2024-02-04 15:26:30 338

338

电子发烧友App

电子发烧友App

评论