经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不失真采集,根据奈奎斯特定理, 采样频率必须为信号频率的2 倍以上,但在电阻抗多频及参数成像技术中正

2023-09-15 09:45:01 1054

1054

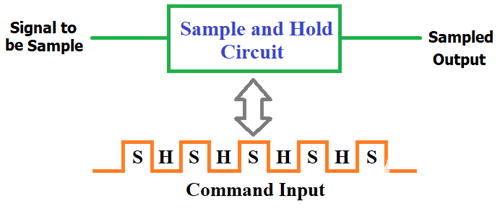

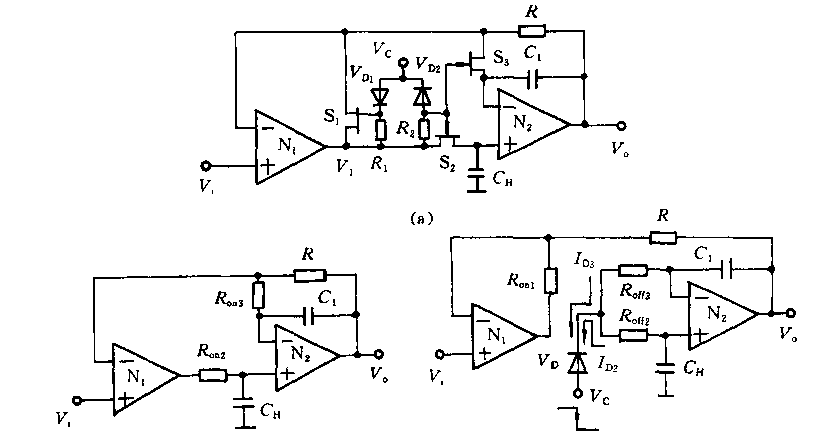

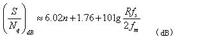

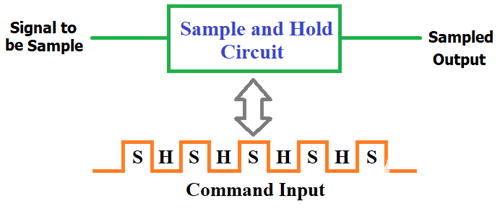

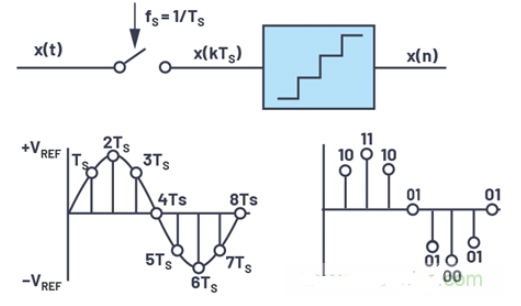

本文主要介绍了采样保持电路图大全(五款采样保持电路设计原理图详解),采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。采样保持电路即为实现这种功能的电路。

2018-02-23 09:59:44 95716

95716

采样保持电路从模拟输入信号中获取样本并保持特定时间段,然后输出输入信号的采样部分。该电路仅对几微秒的输入信号进行采样。

2022-11-08 17:29:18 6704

6704

作者:Wasim Shaikh 和 Srikanth Nittala 本文介绍连续时间Σ-Δ ADC,通过简化信号链来有效解决采样问题。采用这种方法无需使用抗混叠滤波器和缓冲器,并可解决与额外组件

2020-12-30 17:06:17 3456

3456

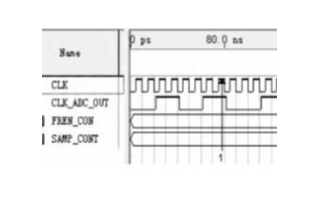

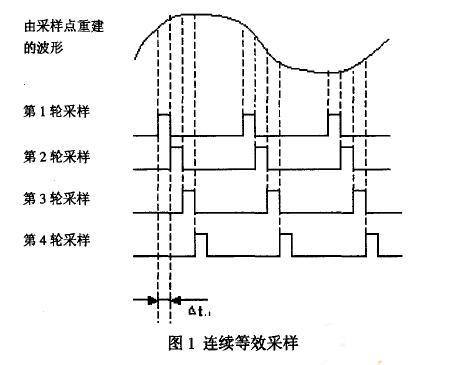

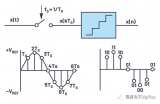

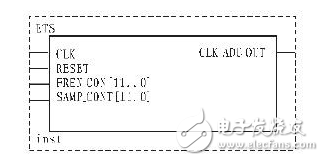

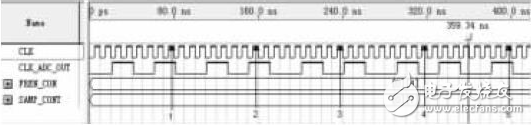

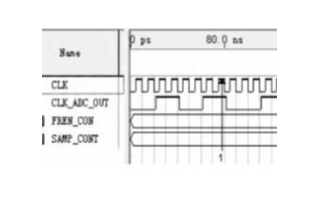

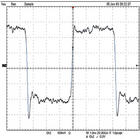

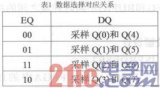

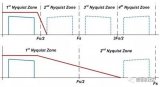

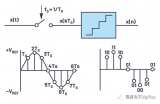

,分频后的时钟波形在时钟的上升沿对信号进行采样,那么就会得到如图1(a)中所表示的等效时间采样。等效时间采样技术的原理作用及采用FPGA器件实现系统的设计图1 等效时间采样示意图2 、基于FPGA的等效

2020-10-21 16:43:20

等效时间采样中应用的ADC,应该注意哪些问题呢?一般采样速率有何限制?对于ADC的模拟输入带宽呢?

2023-12-25 06:42:31

AD值存到SPI FLASH中。 我发现采样频率是4K时还是比较准的。当采到10K时,由于SPI FLASH的写入的函数比较浪费时间,导致整个采样的时间不对。 大家有没有什么好办法来存数啊?我要存100K左右的数据。多谢各位啦~

2020-08-20 08:00:14

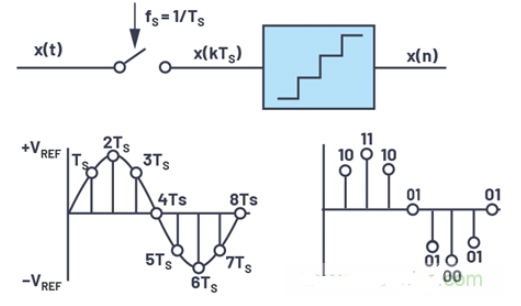

电路中经常用到AD采样,但对于AD采样的原理有没有想进一步了解下,以显示下自己不止于小白呢,那么请往下看。----AD采样的分类----包括并联比较型(也叫Flash型)、SAR型(逐次逼近型

2022-01-26 06:49:44

STM32——ADC采样时间、采样周期、采样频率计算方法ADC转换:单片机将采集到的模拟量信号,通过ADC控制器转换成数字量。采样周期:单片机读取数字量必须等转换完成后,完成一个通道ADC读取(采样

2021-12-10 06:16:05

ADC_RegularChannelConfig(ADC1, ADC_Channel_10, 1, ADC_SampleTime_55Cycles5); //设置指定 ADC 的规则组通道,设置它们的转化顺序和采样时间 ADC_Cmd

2020-08-28 08:00:16

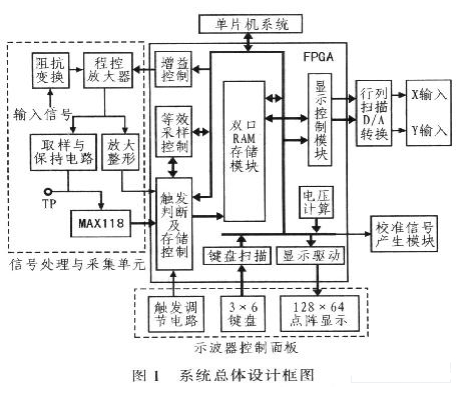

项目名称:等效随机采样的数字存储式示波器试用计划:利用fpga驱动高速adc模块,构成数字存储式示波器

2017-06-20 11:19:18

高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。高采样率需要高速的模/数转换器(ADC)。目前市场上单片高速ADC的价格昂贵,分辨率较低,且采用单片超高速ADC实现的数据采集对FPGA的性能和PCB布局布线技术提出了严峻的挑战。

2019-11-08 06:34:52

你好,这是原理图

我使用FPGA对AD7606进行采样,每次采样的值总是再下一次采样时出现,请问这是什么问题?

2023-12-14 08:06:06

,采取等位移多点取样法,完全克服了以上方法的缺点,具有很高的识币能力。同时,还能对硬币的直径进行检测。由于采样时间和采样间隔都很短,对系统的高速性和可靠性有较高的要求,用传统的单片机难以满足要求,在该设计中,通过FPGA完成对数据的高速采样和处理。

2018-11-09 11:00:49

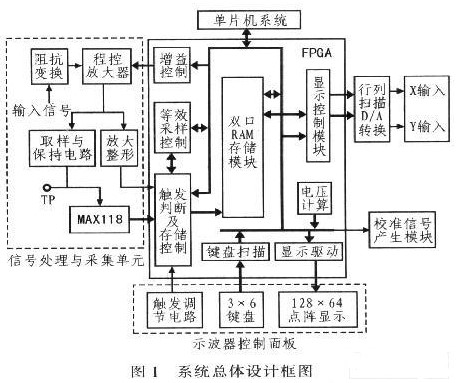

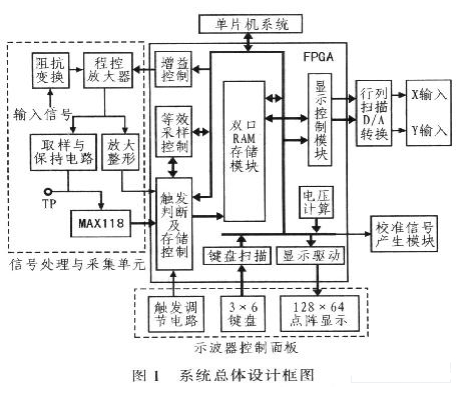

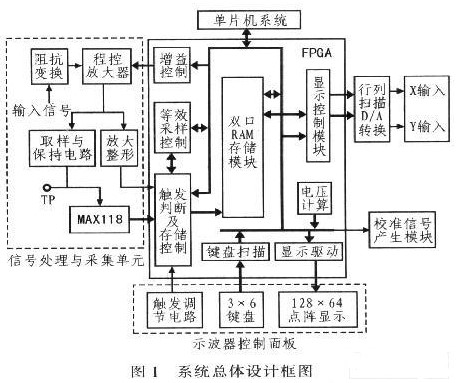

本文介绍一种基于等效和实时采样的数字示波器设计。

2021-05-17 06:00:57

请教各路大神,在ucos里若是AD采样时间需要很准确,例如50us采样一个数据,有什么解决方法呢? 单分配一个AD采样任务貌似不太合理。

2019-08-09 04:15:59

Hello,我利用2812的AD对一个200Hz的正弦信号进行采样,要求每个周期采20个点,然后在Ad的中断服务子程序中进行处理,虽然经过计算可以设置AD的采样频率,但是因为中断服务子程序的执行时间不好控制,我想问一下,如何能够保证我的Ad采样频率?谢谢!

2018-08-19 07:40:23

等效时间采样中应用的ADC,应该注意哪些问题呢?一般采样速率有何限制?对于ADC的模拟输入带宽呢?

2018-11-26 09:46:09

实时技术到底有什么意义?到底选择实时采样还是等效时间采样?

2021-05-10 06:57:27

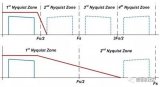

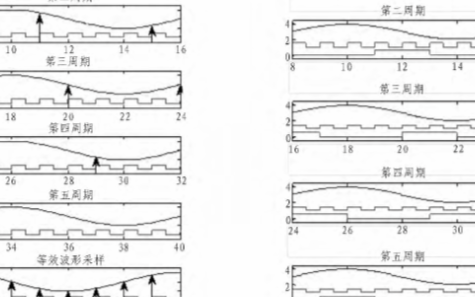

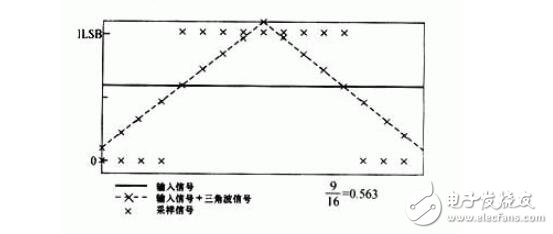

在数字示波器技术中!常用的采样方法有两种" 实时采样和等效采样# 实时采样通常是等时间间隔的!它的最高采样频率是奈奎斯特极限频率# 等效采样$3456789:;<$8=>96;?% 是指

2010-07-08 16:30:04 42

42 本文在介绍了等效采样的原理和方法的基础上提出了一种基于EDA技术的实现方案。借助高速发展的EDA技术,可以方便地产生采样信号,大大简化采样触发电路,解决了传统等效采样

2010-08-03 10:48:54 19

19 针对四通道时间交叉采样对时钟的严格要求,提出了使用时钟分配器AD9516给四个交叉采样的模数转换器AD9445提供四路在相位上严格相差90°的110 MHz的采样时钟。在介绍AD9516特

2010-12-16 16:08:58 0

0 摘要:介绍了基于单片机系统的精密时钟发生电路对高频信号(1MHz~80MHz)进行等效采样的方法,设计并实现一个模拟带宽为1Hz~80MHz的简易数字示波器。

2006-03-24 13:13:02 1373

1373

采样保持放大器

采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这

2009-03-11 18:29:56 3785

3785

采样保持电路(S/H)原理

A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。为此,在ADC前加入采样保持电路,如图8-30所示。采样保持电路有两种

2009-04-12 12:01:35 22785

22785

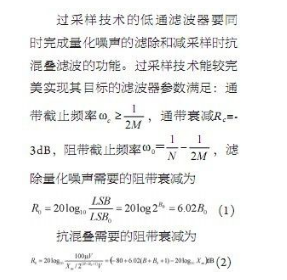

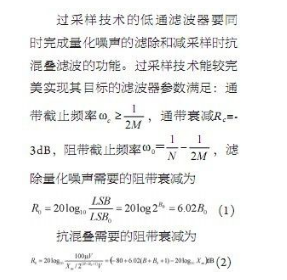

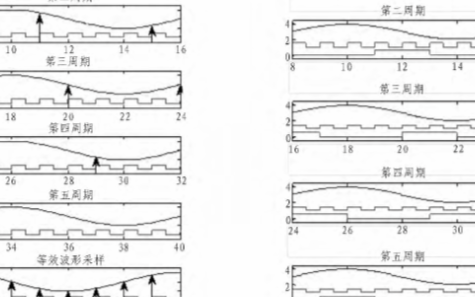

过采样技术原理介绍

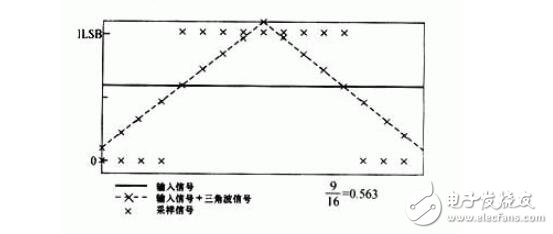

假定环境条件: 10位ADC最小分辨电压1LSB 为 1mv 假定没有噪声引入的时候, ADC采样上的电压真

2009-05-04 19:23:53 13146

13146 什么是过采样

过采样是使用远大于奈奎斯特采样频率的频率对输入信号进行采样。设数字音频系统原来的采样频率为fs,通常为44.1kHz或48kHz

2009-05-04 19:27:55 4259

4259

什么是采样频率?什么叫采样频率

采样频率:即取样频率,指每秒钟取得声音样本的次数.它的采样频率越高,声音的

2009-05-04 19:42:42 20344

20344

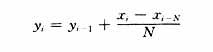

基于DSP的过采样技术

在使用DSP进行数字信号处理时,应用过采样技术可以增加其内置模数转换器的分辨率。讨论了应用过采样技术的原理、如何使

2009-05-04 21:22:37 923

923

DSP的过采样技术原理

在使用DSP进行数字信号处理时,应用过采样技术可以增加其内置模数转换器的分辨率。讨论了应用过采样技术的原理、如何

2009-05-04 22:40:17 2745

2745

在使用DSP进行数字信号处理时,应用过采样技术可以增加其内置模数转换器的分辨率。讨论了应用过采样技术的原理、如何使用TMS320LF2407来实现过采样,以及在软件上的实现方法

2009-05-09 12:19:05 681

681

图像子采样

对彩色电视图像进行采样时,可以采用两种采样方法。一种是使用相同

2009-07-31 14:22:59 4908

4908 什么是采样的频率/采样的位数?

采样频率是指录音设备在一秒钟内对声音信号的采样次数,采样频率越高声音的还原就越真实越自

2010-02-05 09:54:04 2088

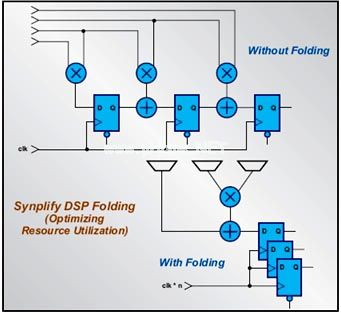

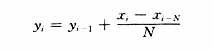

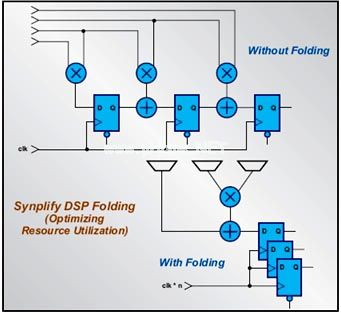

2088 用FPGA实现音频采样率的转换

如今,即使低成本FPGA也能提供远远大于DSP的计算能力。目前的FPGA包含专用乘法器甚至DSP乘法/累加(MAC)模块,能以550MHz以上的时钟速度处理

2010-03-01 10:50:05 3788

3788

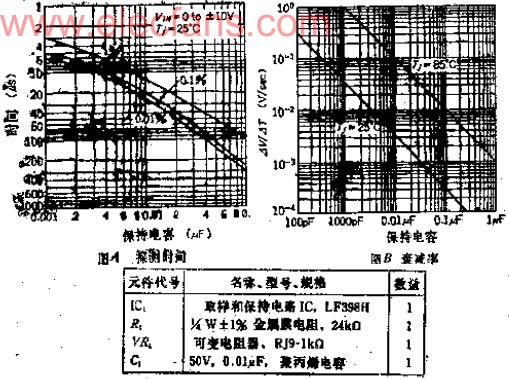

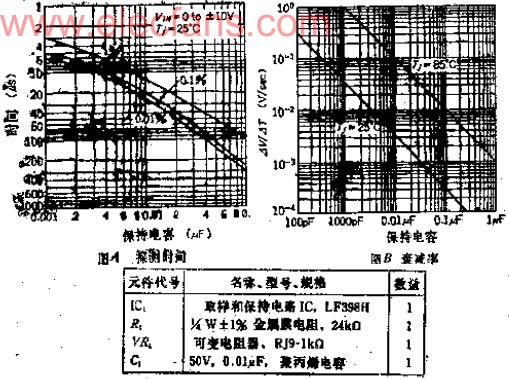

采样时间为20US的中速采样和保持电路

电路的功能

所谓采样和保持

2010-05-05 15:53:51 1382

1382

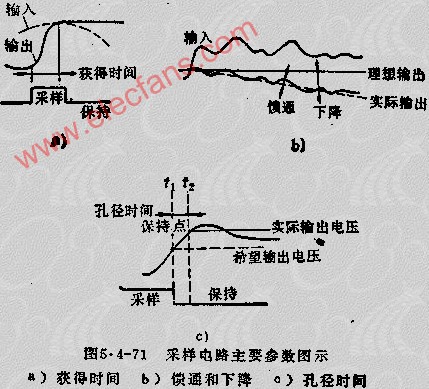

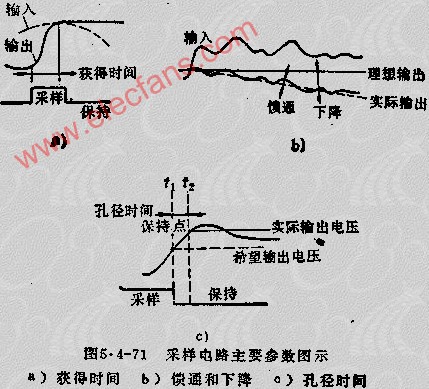

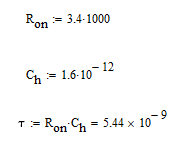

采样电路的特性参数

为了衡量采样电路的工作特性,一般要考查以下的儿个主要参数。

1、获得时间

2010-05-23 17:42:56 1573

1573

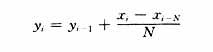

提出了一种应用于便携式数字存储示波器等效采样的实现方案。详细讲述了FPGA和微处理器LPC2138对高频信号随机等效采样的处理过程,利用一种全新的方法即主要利用FPGA内部逻辑单元完成对触发时刻到与下一采样时刻的时间间隔的测量。给出了FPGA对采样点的处理方

2011-03-16 12:12:35 126

126 为了降低系统成本和功耗, 采用基于ARM 系统的精密时钟发生电路对高频信号(6. 25MHz~100MHz) 进行等效采样, 配合高速AD、F IFO 和FPGA 电路设计并实现一个手持式存储示波表。该样机在人机

2011-06-21 16:33:41 114

114 本内容提供了2812片内ADC采样时间计算。1)序列采样模式(SMODE = 0)[attach]12497[/attach]

2011-09-05 11:39:36 3094

3094 对超宽带系统中采样门前置电路进行了理论分析和系统研究,对其产生电路中输入信号的幅度和宽度、采样信号的宽度和上升时间、等效采样的时间间隔等因素的影响进行了分析,给出

2011-10-11 14:58:57 28

28 利用过采样技术可在不需片外ADC器件的情况下,达到同样的采样效果。将Cortex-M3内核与过采样技术相结合,不仅能够降低成本,而且提升了系统的运行速率、可靠性与稳定性。

2012-02-06 16:41:07 41

41 在使用DSP进行数字信号处理时,应用过采样技术可以增加其内置模数转换器的分辨率。讨论了应用过采样技术的原理、如何使用TMS320LF2407来实现过采样,以及在软件上的实现方法。

2012-03-20 14:10:09 15

15 2015-08-24 18:14:00 18

18 基于FPGA多通道采样系统设计资料,有兴趣的同学可以下载学习

2016-04-28 14:29:56 48

48 基于FPGA实现变采样率FIR滤波器的研究

2017-01-08 15:59:09 19

19 基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦

2017-01-18 20:23:58 12

12 等效采样

2017-03-04 17:52:58 13

13 基于ARMCortex_M3的过采样技术

2017-09-29 09:58:20 4

4 基于ARM Cortex-M3的过采样技术

2017-10-30 16:39:17 8

8 ADC转换就是输入模拟的信号量,单片机转换成数字量。读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。采样周期一般来说=转换时间+读取时间。转换时间=采样时间+12.5个时钟周期。采样时间是你通过寄存器告诉STM32采样模拟量的时间,设置越长越精确。

2017-11-14 14:52:57 30137

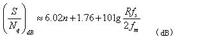

30137 的2倍以上,但在电阻抗多频及参数成像技术中正交序列数字解调法的抗噪性能对信号每周期的采样点数决定,采样点数越多,抗噪性能越高。当采样信号频率很高时,为了在被采样信号的一周期内多采样,就需要提高采样时钟的频率,但是由

2017-11-16 16:12:18 7

7 针对LVDS接口,研究并实现了一种基于FPGA的LVDS过采样技术,重点对LVDS过采样技术中系统组成、ISERDESE2、时钟采样、数据恢复单元、时钟同步状态机等关键技术进行了描述

2017-11-18 05:13:01 6915

6915

项目背景及可行性分析 1.项目名称、项目的主要内容及目前的进展情况 项目名称: 基于FPGA的高速采样显示电路的实现 主要内容:通过对被测信号的实时采样,利用等效采样原理,可以将采样率为1MHz等效

2017-11-22 11:18:29 14

14 由于存在内部热噪声、孔径抖动和渡越时间不确定性等因素,面临采样速度和精度相互制约的影响,出现了瓶颈。而由多通道时间交织ADC(Time-lnterleaved ADC.TIADC)采用M个相同型号的ADC单元依次交替完成采样。理论上,TIADC的采样率可以到达单ADC的M倍,同时保持采样精度基本不

2018-02-07 13:51:17 2

2 RF采样转换器可捕获高频信号和大带宽信号;但是,并非每种应用都能利用需要极高速采样的信号。就带宽或输出频率不过高的情况而言,利用RF采样转换器的高采样速率能力仍存在一大优势。

2018-05-02 09:30:50 7852

7852

误差、增益误差以及时间相位误差将严重降低数据采集系统性能[2]。基于数字信号处理方法的数字后端修正技术可有效抑制以上失配造成的失真。近年来,已有文献应用FPGA实现数字后端修正技术。文献[3]采

2018-06-25 11:45:00 7047

7047

数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部实现。为实现多路并行采样,可选用多片A/D器件并行处理的方式,在FPGA的高速状态机控制下,完成模拟信号经过

2018-08-28 10:16:07 12734

12734

选择实时采样和等效采样相结合的方式,实时采样速率小于1 MS/s,水平分辨率至少为20点/div,故系统50 kHz以下采用实时采样方式,而50 kHz~10 MHz采用等效时间采样方式,最高等效采样速率可达到200 Ms/s。

2019-05-05 08:19:00 2266

2266

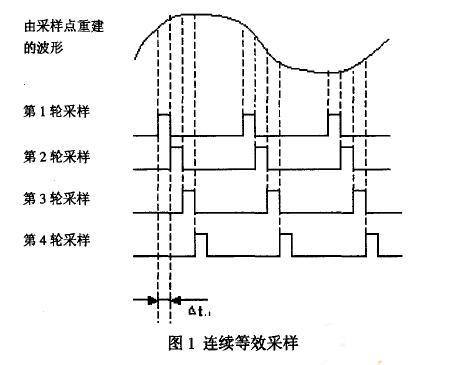

有两种等效采样的方法:随机等效采样和连续等效采样。连续等效采样在每个触发捕获一个样值,而不依赖于时间/格的设置和扫描速度,每发现一个触发经过一个虽然很短却明确的延迟(deltat) ,就获得

2018-11-08 08:40:00 6715

6715

过采样技术是数字信号处理者用来提高模数转换器(ADC)性能经常使用的方法之一,它通过减小量化噪声,提高ADC的信噪比,从而提高ADC的有效分辨率[1]。过采样技术不但没有增加额外的模拟电路,而且由于提高了有效分辨率还能简化模拟电路,并且简单易行,因而被数字信号处理实践者广泛应用于测控领域

2018-12-19 09:55:55 2321

2321

过采样技术在通信信号处理中的应用龙雄摘要:过采样技术应用能够促使各类通信信号能够趋于平稳循环化发展,更利于技

2019-02-24 08:42:00 4837

4837

输入系统的有正有负的模拟信号在AD采样前,会加上了直流偏置变成全正信号才输入AD的,所以在AD采样后送给FPGA的信号是无符号数。

2019-08-11 11:43:39 2821

2821 采样电阻是电流采样和对电压采样。对电流采样则串联一个阻值较小的电阻,对电压采样则并联一个阻值较大的电阻。采样电阻又被称为合金电阻、电流检测电阻、取样电阻等。

2019-11-08 08:47:34 8954

8954 的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。

2020-03-12 10:22:48 2628

2628

信号传输中,数字信号将对模拟信号产生干扰,目前采用的解决方法是利用单片机来实现模拟信号和数字信号在单线中的混合传输,而这其中的测试和调试就要求示波器必须能够对数字信号和模拟信号同时进行分析和显示。因此,这里介绍一种基于等效和实时采样数字示波器的设计。

2020-08-18 10:25:05 2001

2001

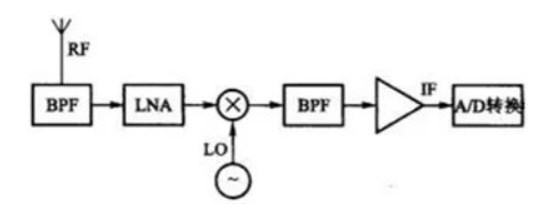

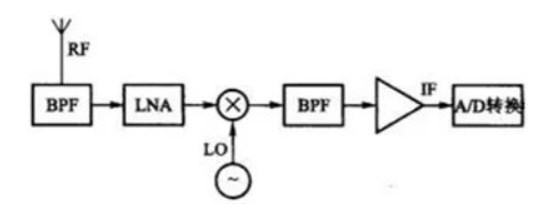

一、什么是中频采样,什么是IQ采样 射频接收系统通常使用数字信号处理算法进行信号解调和分析,因此需要使用ADC对信号进行采样。根据采样频率的不同,可以分为射频直接采样、中频采样、IQ采样。射频采样

2020-12-02 14:03:25 9031

9031 本文档的主要内容详细介绍的是基于FPGA的AD采样的实现免费下载。

2021-01-21 15:33:54 31

31 AN-1543:ADuCM4050中用于时间同步的SensorStrobe和输入采样、传感器数据采样

2021-04-27 18:50:18 1

1 最终为此牺牲系统目标。 本文将会从采样技术的基础知识说起,重温模数转换的基本运作方式,并帮助大家理解现实中会遇到的问题。在接下来的后一篇文章中,我们会进一步介绍如何通过连续时间Σ-Δ ADC简化信号链,有效地解决采样中遇

2021-06-25 11:28:04 2582

2582

利用FPGA控制ADC0809采样电压(长城电源技术(山西有限公司)-利用FPGA控制ADC0809采样电压,并通过数码管显示电压数值

2021-09-28 11:05:04 36

36 烟气剖析仪的采样体系分为惯例采样体系和加热采样体系。 1、惯例采样体系:一般选用耐酸碱,耐高温的塑料管,确保对气体无吸附。 适用状况:含水量较低样气的短时间测验;不含酸性气体的样气的短时间测验

2021-11-02 17:17:02 338

338 在A/D转换器中,因为输入的模拟信号在时间上式连续的,而输出的数字信号代码是离散的。所以A/D转换器在进行转换时,必须在一系列选定的瞬间(时间轴上的一些规定点上)对输入的模拟信号采样保持,然后再

2021-11-11 12:36:05 3

3 STM32: ADC采样频率及相应时间的确定

2021-11-26 20:36:05 19

19 ADC转换就是输入模拟的信号量,单片机转换成数字量。读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。采样周期一般来说=转换时间+读取时间。而转换时间=采样时间+12.5个时钟周期。采样

2021-11-26 20:36:06 88

88 STM32 ADC 过采样技术

2021-12-08 16:21:06 41

41 第一:前言用STM32 采集数据必须依据信号源设置采样频率。根据奈奎斯特定律,采样率必须是信号源最大频率的2倍以上,但是在实际的需求当中,采样率应该是Fs>3Fmax .采样周期=转换时间

2021-12-14 18:57:51 42

42 对过采样技术的理解与记忆

2022-02-07 15:36:06 663

663 射频接收系统通常使用数字信号处理算法进行信号解调和分析,因此需要使用ADC对信号进行采样。根据采样频率的不同,可以分为射频直接采样、中频采样、IQ采样。射频采样和中频采样只需要一路ADC,采样结果

2022-07-28 09:05:47 2626

2626 示波器采样频率,又称采样速度或采样率,定义了每秒从连续信号中提取并形成离散信号的采样数量,它使用赫兹(Hz)来表示,采样频率倒数为采样周期或采样时间,即采样间隔,一般来说,采样频率是指计算机每秒采集多少个信号样本。

2022-09-14 15:38:13 2709

2709 评估快速和超快速数据转换器动态性能的最有用技术之一是相干采样。这种技术提高了快速傅立叶变换(FFT)的光谱分辨率,并且在满足某些条件时无需进行窗口采样。但是,如果不能满足相干采样的条件,则可

2023-02-25 10:07:07 2822

2822

本文分析数字电源ADC采样时间的原理、误差来源、改善方法。

2023-03-08 15:01:00 3182

3182

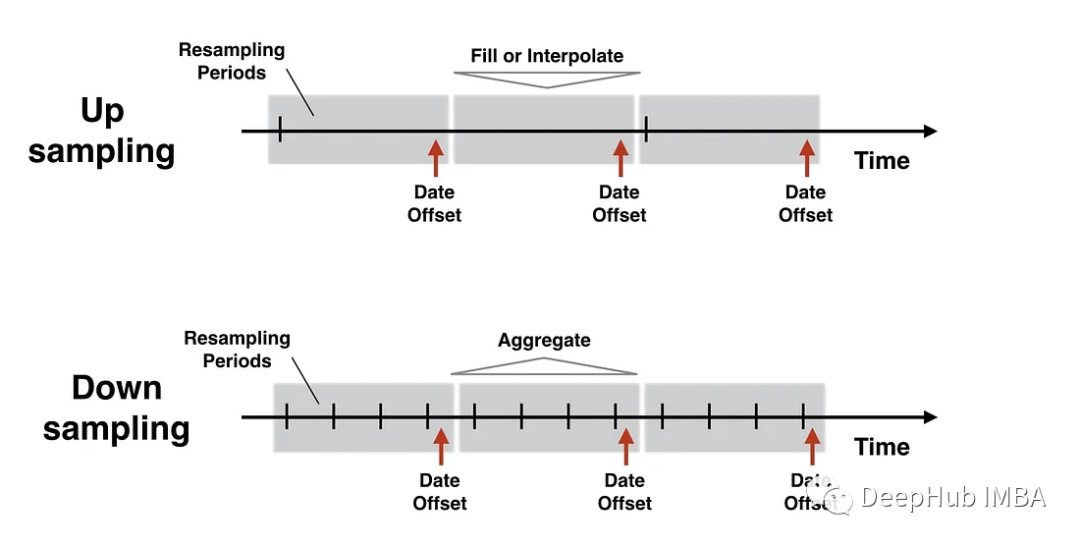

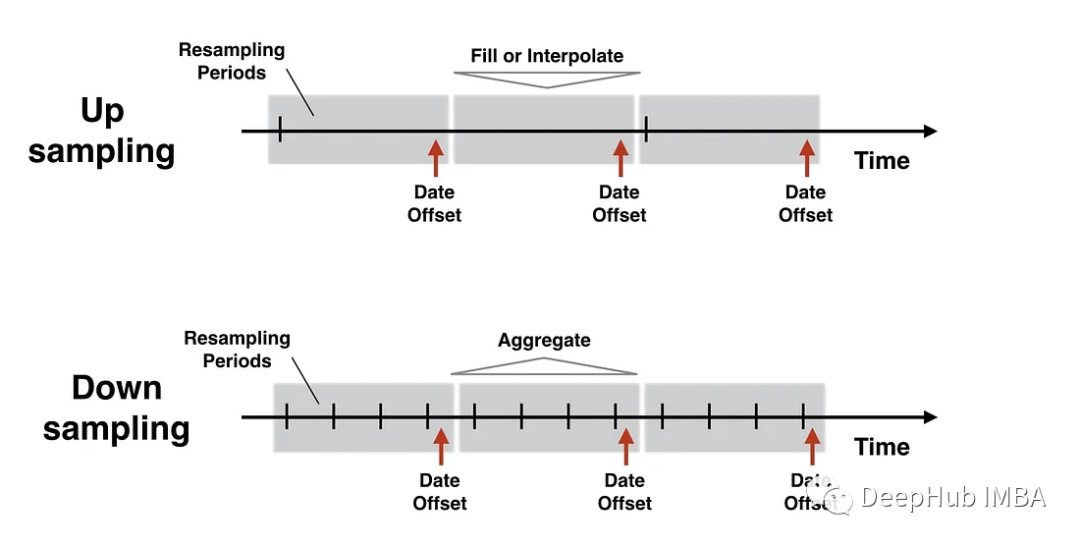

点击上方 蓝字 关注我们 采样就是采集模拟信号的样本。通常采样指的是下采样,也就是对信号的抽取。其实,上采样和下采样都是对数字信号进行重采,重采的采样率与原来获得该数字信号的采样率比较,大于原信号

2023-06-08 17:15:03 732

732 用于等效时间采样应用的空间多路单腔双光梳激光器1介绍双光学频率梳(简称双光梳)[1]的概念在光频梳被提出后不久被引入[2-4]。在时域上,双光梳可以理解为两个相干光脉冲序列,它们的重复频率有轻微

2022-05-26 09:47:05 460

460

更改信号采样率是数字信号处理中的一个重要操作,它涉及对信号进行重新采样,以改变信号的采样率。

2023-06-20 14:44:37 2543

2543 ,就需要提高采样时钟的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。 1 等效时间采

2023-07-29 09:00:01 537

537

对于相同的信号周期(下述圆),每隔一段时间采样点移动一次为采样率,表格为三种不同采样率。由表知采样率1采样速度最慢,采样率2最快,采样率3居中

2023-08-17 10:11:13 1799

1799

重采样是时间序列分析中处理时序数据的一项基本技术。它是关于将时间序列数据从一个频率转换到另一个频率,它可以更改数据的时间间隔,通过上采样增加粒度,或通过下采样减少粒度。

2023-09-19 17:06:15 1204

1204

什么是示波器的实时采样率? 什么是示波器的等效时间采样? 示波器是一种测试仪器,用于显示波形和信号的性质。实时采样率是指示波器在一个时间单位内(通常是1秒),可以将信号进行采样的次数。它是示波器

2023-10-17 16:16:07 920

920 示波器采样时间怎么设置 示波器的采样率有什么意义? 一、示波器采样时间的设置 1. 示波器采样时间的概念 示波器的采样时间指的是示波器通过在指定时间段内获取的样本数量来描述示波器的性能。示波器采样

2023-10-17 16:16:10 2207

2207 中频采样是什么意思?中频采样与基带采样的区别 中频采样与基带采样都是数字信号处理中常用的采样技术,它们的区别在于采样信号的频率不同。基带采样是指在信息原始频域内进行采样,而中频采样是指在信号已经

2023-10-22 11:24:39 1146

1146 什么是中频采样?什么是IQ采样?中频采样和IQ采样的比较和转换 中频采样和IQ采样是数字信号处理中非常重要的概念。在数字信号处理中,模拟信号需要经过采样变成数字信号,这样才能让数字电路加以处理

2023-10-22 11:24:42 2240

2240

2023-11-07 08:31:41 0

0 电子发烧友网站提供《奈奎斯特准则如何运用于基带采样、欠采样和过采样应用.pdf》资料免费下载

2023-11-28 09:25:33 0

0 示波器实时采样与等效采样有何区别 示波器实时采样和等效采样是示波器在测量电信号时使用的两种不同的方法。它们在采样速度、信号还原精度、存储和处理能力等方面有所不同。下面将详细介绍这两种采样方法的区别

2023-12-21 14:02:19 319

319 等效时间采样示波器与实时示波器的对比,有什么不同? 等效时间采样示波器和实时示波器是电子测试设备中常用的两种示波器。它们在运行原理、应用场景、优点和缺点等方面存在一些显著差异。 一、等效时间采样

2024-01-19 11:29:28 321

321

正在加载...

电子发烧友App

电子发烧友App

评论