大家好,欢迎Vivado的一个快速演示,它是xilinx新的设计套件,应用到7系列和以上的系列器件。

2012-04-25 08:55:55 2192

2192 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 1526

1526 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

21-36]从C:/Xilinx/Vivado/2013.1/data/parts/arch.xmlParsing RTL基元文件[C:/Xilinx/Vivado/2013.1/data/parts

2018-11-27 14:30:08

嗨,我们刚刚将实施工具从Vivado 2013.1更新到2013.2。使用2013.2软件,我们无法运行实施流程。该工具在综合时崩溃,在安全IP的许可证检查中出现致命错误。请参阅随附的屏幕截图。通常

2018-11-30 11:12:34

[0x3b0060ebe0] /pkg/xilinx-vivado-/2013.4/Vivado/2013.4/lib/lnx64.o/librdi_timing.so(HASTNetworkImpl

2018-10-18 14:40:02

嗨,我下载Vivado2014.3并尝试申请30天的评估许可证!当我通过vivado许可管理器工具连接到xilinx许可证网站时,我将网站显示为附件。1)基于证书的许可证只有3个:ISE

2018-12-06 11:31:19

此消息:bp @ bp:/opt/Xilinx/Vivado/2016.1$ source settings64.shbp@bp:/opt/Xilinx/Vivado/2016.1$ bin

2018-12-21 10:58:20

操作系统:Debian 8工具:Vivado 2016.2(系统设计)我已经下载了xilinx.lic并将许可证复制到我的vivado工具,“查看许可证状态”没有问题,完成块设计后,运行Synthesis,然后合成失败!!附加是信息,是否有人可以修复它!?

2020-05-25 13:25:05

我们非常高兴地宣布Vivado 2017.3的发布 - 包含许多功能。您可以从Xilinx的下载页面下载Vivado 2017.3版本,并参考以下用户指南,了解有关Vivado 2017.3版本

2018-12-28 10:52:15

个图标,我可以成功打开它以启动一个新项目。当我下载vivado 2017.4更新1并双解压缩并运行安装程序时,它会返回一条消息:“没有有效的Xilinx安装,可以应用此更新。”。我已卸载软件并多次重新

2019-01-04 11:14:26

我对Vivado工具如何决定如何映射(例如,从GPIO外部制作的“led”端口到实际引脚而不指定XDC文件中的名称感到困惑。在我看来,只要指定一个引脚,vivado就会以某种方式将一个阵列中的所有

2018-10-30 18:02:44

的。来获取关于原始的 ISE 设计套件以及 Xilinx 在 Vivado 中对这些开发工具做改进的理由的讨论。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的设备,但是

2021-01-08 17:07:20

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

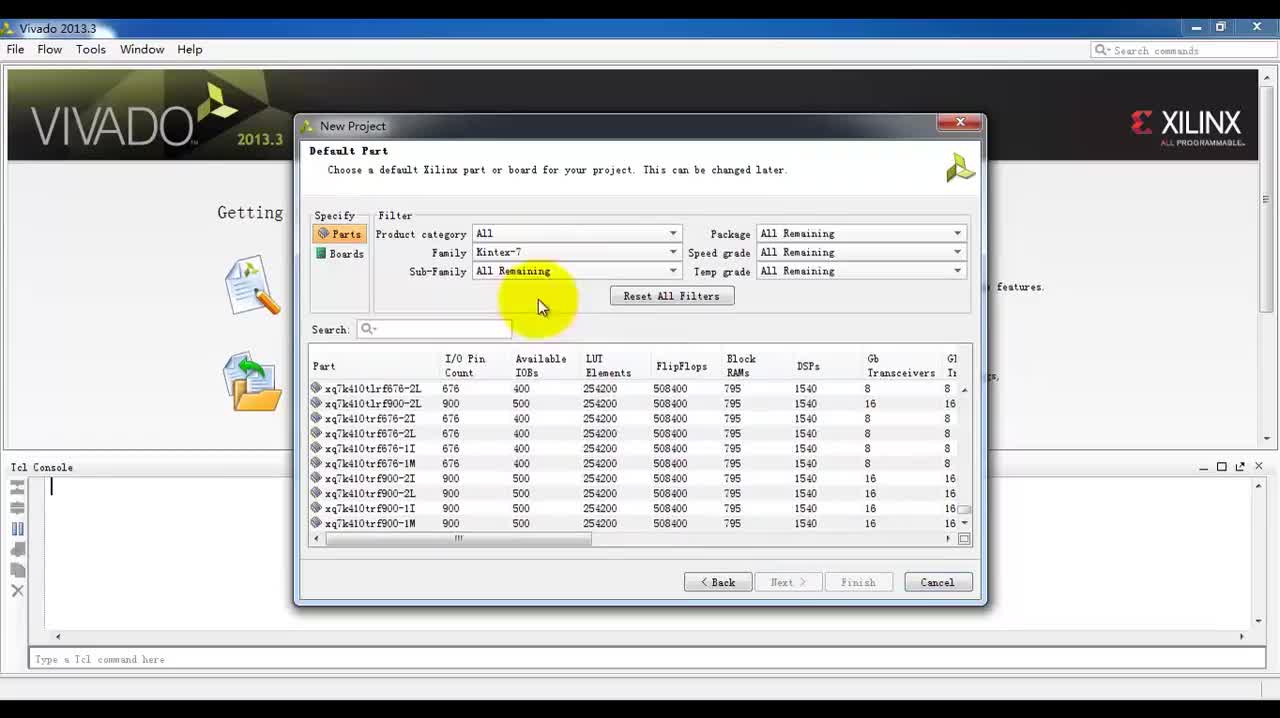

的的Vivado 工具把各类可编程技术结合在一起,能够扩展多达1 亿个等效ASIC 门的设计。Vivado设计界面如下图:图1. Vivado设计界面1.2芯片支持Vivado支持Xilinx的IC如下

2019-07-18 15:40:33

的的Vivado 工具把各类可编程技术结合在一起,能够扩展多达1 亿个等效ASIC 门的设计。Vivado设计界面如下图:图1. Vivado设计界面1.2芯片支持Vivado支持Xilinx的IC如下

2023-09-06 17:55:44

Vivado工具(2016.2)可以独立路由Xilinx IP核DDR3 SDRAM控制器(rdf0223-ac701-mig-c-2015-1.zip)。将mydesign添加到路由可以在合成阶段

2020-05-06 10:32:02

Xilinx设计工具ISE设计套件系统版+ Vivado系统版14.3是否可以为此版本的软件进行静默安装?任何意见,将不胜感激干杯以上来自于谷歌翻译以下为原文Xilinx Design Tools

2018-12-28 10:53:04

你好,我们在2016年3月购买了Xilinx-Vivado / Ise的完整版本。我的同事将我添加为“管理员”,因此我也可以创建许可证。但它没有显示在我的xilinx帐户中,因此我无法生成许可证。我

2018-12-21 11:00:57

嗨,我的同事为我添加了“admin”作为许可证(Vivado / ISE-System) -2016年3月购买的产品。当我登录Xilinx许可时,它没有显示出来。我收到了Xilinx发送的关于将我

2018-12-21 10:58:55

亲爱的Xilinx, 我有一台Windows 8.1联想G500笔记本电脑,我试图安装最新的Xilinx Vivado Webpack + SDk。安装成功完成,但是当我尝试安装许可证时,许可证

2019-11-08 08:56:31

我现在运行了几个项目我观察到安装了程序Xilinx ISE和Vivado的目录高达50 GB,因为我想在运行项目期间生成的文件。我不记得一开始是不是那么多。请告诉我哪些可以删除的“运行时”文件以及

2018-12-20 11:20:46

Xilinx工具:vivado在该图中,TX_CLK_i连接到pll_x1模块的输入时钟。然后,pll_x1的输出时钟连接到ODDR。接下来,ODDR的输出引脚将连接到I / O引脚

2020-05-04 08:04:41

您好。我无法运行Xilinx许可证管理器以使用Ise 14.7加载我的许可证(_xlmc.exe已停止..)。安装Vivado Design Suite 2014.1后出现此错误。我该如何解决?,我可以使用vivado许可证管理器使用Ise工具加载我的许可证吗?

2020-03-12 06:39:47

哪位大神能够分享一下关于xilinx vivado 2013.4 的教程啊,小弟感激不敬!!!

2014-03-26 21:38:02

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?买了一个第三方的IP,给出了端口列表和核心模块发射机的.edf已经综合过的网表文件,该网表文件里面富含了大量的信息,我想知道edf文件怎样添加到Vivado工程中去?要不然的话,总是提示核心模块实例化失败!

2016-09-07 11:34:10

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

申请理由:项目描述:本人之前一直从事Altera FPGA的学习套件的教程资料研发,如今转向Xilinx,考虑Xilinx现在主推的工具是vivado,而S6系列芯片无法使用,为了使自己的教程资料

2016-10-11 18:15:20

关于Xilinx Vivado工具,相信对于接触FPGA开发的工程师应该并不陌生。今天来讲讲Vivado的安装详细步骤。 Vivado设计套件,是FPGA厂商Xilinx(赛灵思)公司2012年发布

2020-05-31 10:20:03

您好,我想下载Xilinx Vivado 2017.1但是,每次我收到以下错误:“由于您的帐户导出合规性验证失败,我们无法满足您的要求。”谁能帮我?提前致谢以上来自于谷歌翻译以下为原文Hello

2018-12-27 10:41:52

嗨,我正在寻找有关如何使用Xilinx Vivado创建Hard宏的示例。了解如何在设计中修复路由并在阅读pdf(下面)时,提到可以根据要求提供示例,这将非常有帮助。我是否可以收到一些此实施的示例

2018-11-12 14:42:01

请问一下Xilinx公司发布的vivado具体的作用是什么,刚刚接触到,以前一直用quartus ii,没有使用过ise,后来今天听说了vivado,不知道是做什么用的,希望大家都能参与讨论中,谢谢。

2015-04-15 16:51:00

Vivado工具使用流程和Basys3板卡使用Xilinx FPGA基础知识简介以计数器(或流水灯)实验为例,完成Vivado设计流程Basys3板卡简介Vivado设计在Basys3上的实现2

2019-02-19 10:56:07

,但现在有了Vivado,我没有看到这样的应用程序我希望Xilinx不要像许多其他应用程序那样放弃这个应用程序以上来自于谷歌翻译以下为原文Hello everyone Can I Install

2018-12-27 10:57:02

.Vivado 2016.4与Spartan-6不兼容。据Xilinx称,Vivado不支持任何早于7系列的设备系列。)根据以下说明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

你好,我在CentOS 7中安装了Vivado v2015.2(64位)。但是,Vivado工具在第二次出现时出现以下错误消息。 /opt/Xilinx/Vivado/2015.2/bin

2018-12-13 10:36:45

尽管Debian是Xilinx工具不受支持的平台,但如果我们使用其衍生工具(Ubuntu等),它就是一个widley分发版。经过一些工作,我已经能够在Debian上使用Vivado。这是我所做的以防

2018-12-05 11:00:34

/Xilinx/Vivado/2013.2/tps/lnx64/jre/lib/amd64/server/ libjvm.so /opt/Xilinx/Vivado/2013.2/tps/lnx64

2018-12-10 10:29:37

`基于 FPAGxilinx vivado 仿真模式介绍本文介绍一下xilinx的开发软件 vivado 的仿真模式, vivado的仿真暂分为五种仿真模式。分别为:1. run

2018-01-24 11:06:12

嗨,我正在使用Xilinx Vivado工具对带有MCS文件的Spansion配置闪存进行编程,并且需要以0x100(256)的偏移对其进行编程。我需要最初的256个字节来编程其他信息,并要求从地址

2020-06-09 10:28:14

你好,我对Xilinx工具的自下而上合成流程有一些疑问。由于我对这个领域很新,所以我只知道ISE和XST。在我的顶级设计中,我实例化了几个优化的多线程(不是库中的标准乘法器),但我不希望它们在综合

2019-03-22 06:51:51

当我试图在Ubuntu的Synplify中调用xilinx for P& R时,它说XILINX变量尚未设置。我把它分配到vivado中的bin文件夹,但似乎是错误的。看起来Synplify

2018-12-19 11:04:40

大家好,在将vivado 2016.1安装到d:\ xilinx时,发生以下错误:提取存档D时遇到错误:\ Xilinx_Vivado_SDK_2016.1_0409_1 \ payload

2018-12-20 11:23:44

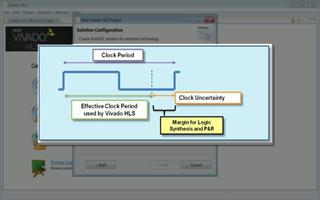

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

xilinx.notification@entitlenow.com with the ‘get license’ links. The installation steps require Vivado Design Suite\Vivado

2018-12-19 11:21:19

:Edition选择安装:Vivado HL WebPACKWARN:指定的值在InstallOptions的配置文件中(启用WebTalk for SDK将使用情况统计信息发送到Xilinx)丢失或无效。警告

2018-12-19 11:16:14

嗨,我是Xilinx工具的新手,现在正在学习FPGA设计。如果Xilinx Vivado是使用和学习的最佳工具,有人可以指导我吗?如果是这样,哪个版本可以免费使用,如果可能的话链接。谢谢,

2020-04-17 07:38:59

that is compatible with the version of Xilinx software that you are using. Please note that Vivado

2019-01-04 11:06:38

我在Digilent论坛上看到有关于学习Vivado软件菜单基础知识的Xilinx PDF,我在哪里可以找到PDF?此外,当我安装Vivado时,我安装了所有内容,我是初学者,如果我只是安装一个简单的Vivado菜单,那将是最好的,但我如何恢复它,这会以任何方式搞砸我的许可证?traymond

2020-04-30 09:32:35

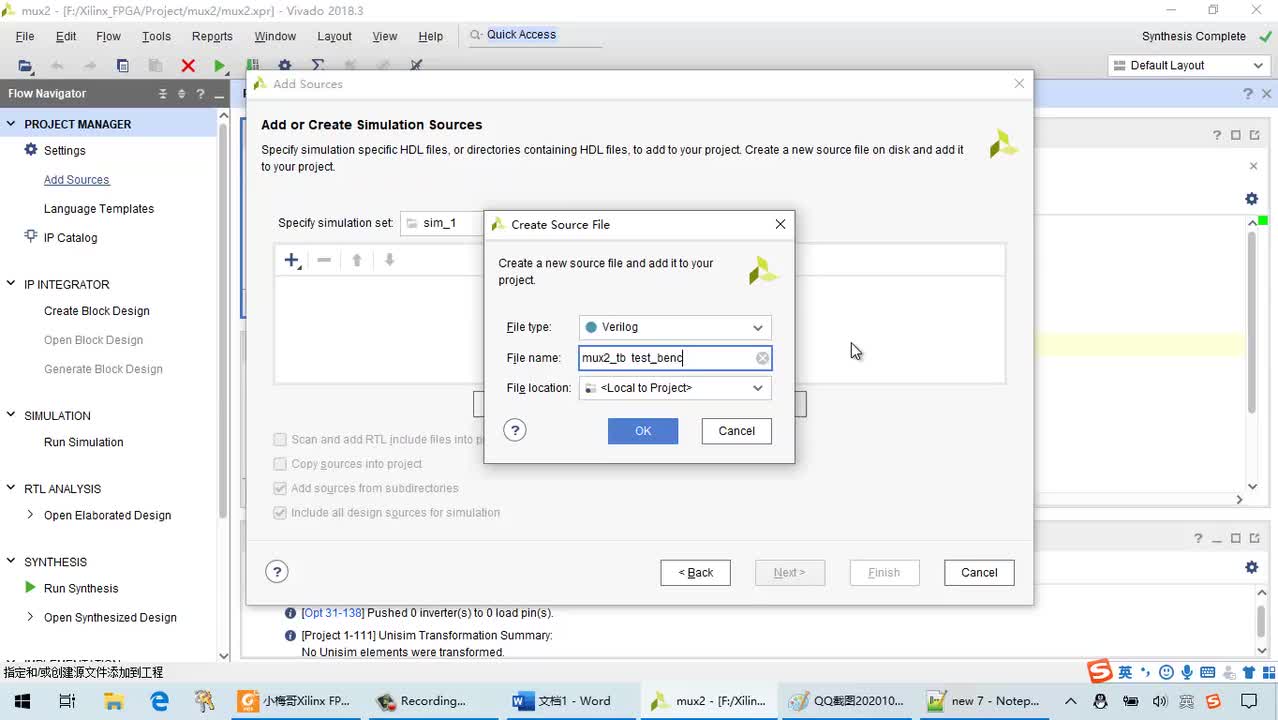

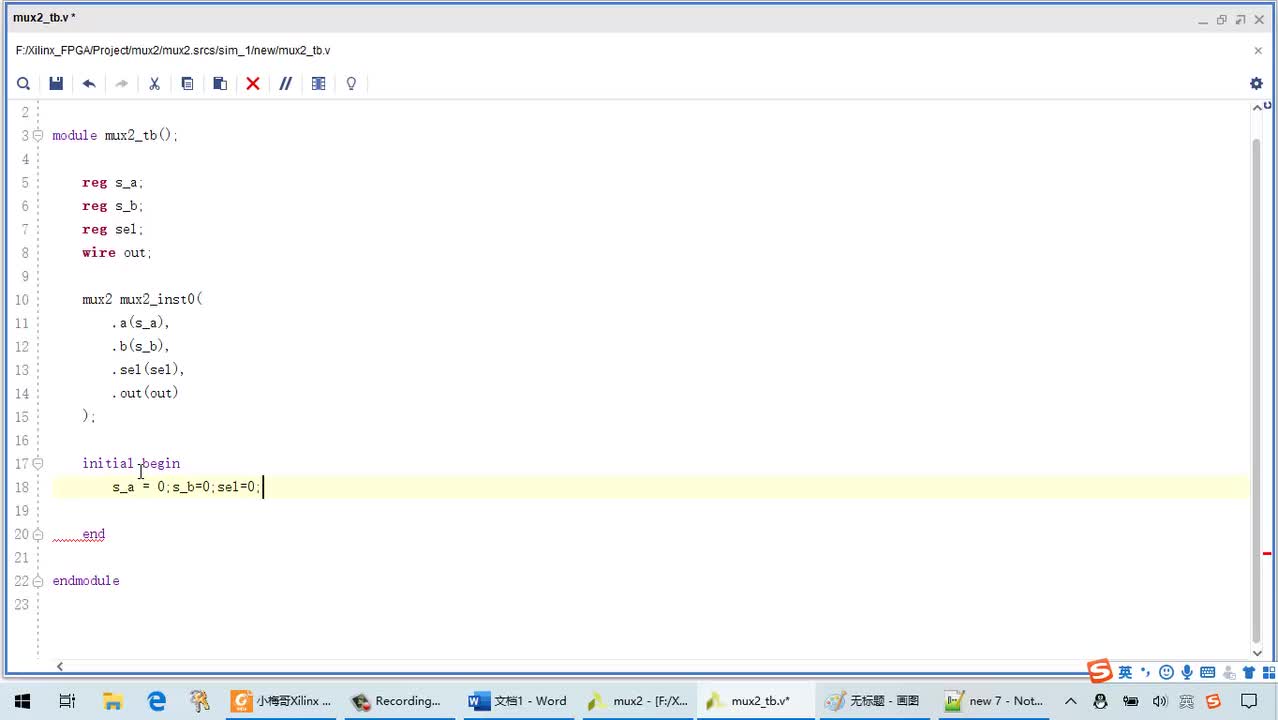

由各自的testbench,分类管理更一目了然。图2 Vivado中testbench文件管理 2. Vivado自带的Simulation/Simulator工具与Altera索性放弃自己的内置

2016-01-13 12:04:16

嗨,你能告诉我在闪存存储器MT29F1G08ABADAWP-IT:D的vivado工具中设置的设置,来自制造商Micron与Xilinx Zynq Soc XC7Z020-2CLG400I一起

2019-03-27 10:14:33

你好,我安装了Xilinx vivado 2015.2,我将开始为USRP x310编写计算引擎。为此,我需要一个完整的Xilinx设计许可证。首先,我想澄清一下本网站末尾发布的许可是否合适,因为我

2020-05-06 07:58:17

RIO设备的FPGA编程,安装了LabVIEW 2015 FPGA Module Xilinx Tools Vivado 2014.4安装此工具包时选择了评估版本,目前正常使用,不知道评估期是多久。LV已经激活了专业版,请问怎样彻底激活这个编译工具包啊?LV Licence管理器中没有出现这个模块。

2015-08-28 22:20:22

Xilinx发布Vivado Design Suite 2013.3版本,新增最新UltraFast设计方法及新一代即插即用IP和部分重配置功能,丰富设计流程,实现前所未有的IP易用性, 进一步提高设计生产力

2013-12-24 17:51:23 1193

1193 Xilinx采用先进的 EDA 技术和方法,提供了全新的工具套件Vivado,面向未来“All-Programmable”器件。Vivado开发套件提供全新构建的SoC 增强型、以IP和系统为中心

2017-02-08 04:10:11 457

457 一年一度的 Club Vivado 用户群大会即将在全球 9 大城市举行。Xilinx 诚挚欢迎全球的 Vivado 用户参与到这一免费活动中。您将有机会与 1,000 多位设计工程师同行

2017-02-08 06:04:03 204

204 美国赛灵思官方授权培训伙伴依元素科技,以赛灵思最新的客户培训课程,通过Webex在线举办免费培训。近期推出的在线免费培训是 “Vivado设计套件工具流程”。 Xilinx采用先进的 EDA 技术

2017-02-08 11:58:12 423

423 Virtex和Kintex UltraScale架构的FPGA和Vivado开发工具的一些主要的看点: • 基于UltraScale架构的FPGA实现数据传输机制是通过将高性能的并行专用IO接口和高速的串行收发器结合起来实现的,UltraScale架构的串行

2017-02-08 12:33:07 495

495 很久没有更新vivado+zedboard系列的博客了。前面的十篇博客主要介绍了Xilinx vivado工具的使用流程,vivado+zedboard裸机开发的方法以及部分Xilinx官网的实例

2017-02-08 16:20:11 1058

1058 众所周知 Hackaday.com 网站上聚集着众多极客(Geeker),他们打破传统,标新立异,敢于尝试新的东西,今天这篇文章搜集了这些极客对Xilinx Vivado HLS工具使用经验和心得

2017-02-08 20:01:59 550

550

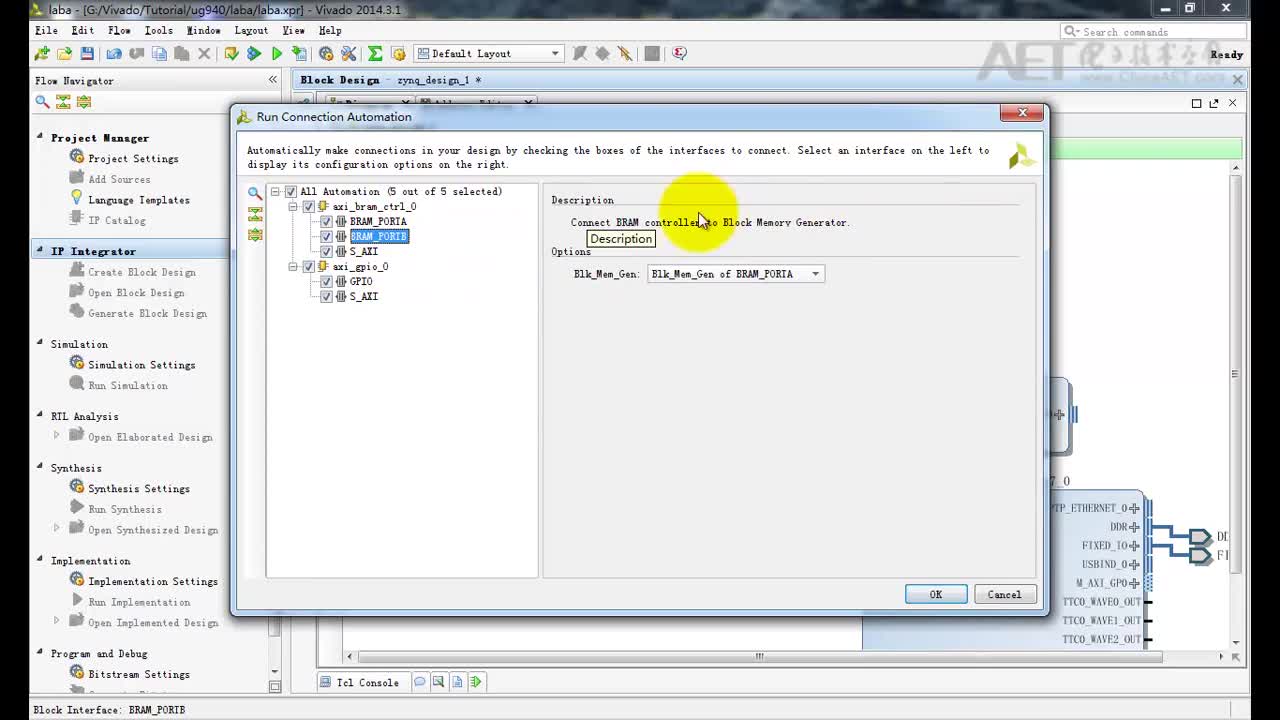

无缝集成在其设计中的工作。该 IP 集成工具支持针对所有 Xilinx 器件提供,其中包括最新 UltraScale 器件系列,可充分满足 Vivado 设计套件工具 2014.4 以及更高版本的要求。 了解更多 »

2017-02-09 08:12:36 319

319

随着xilinx公司进入20nm工艺,以堆叠的方式在可编程领域一路高歌猛进,与其配套的EDA工具——新一代高端FPGA设计软件VIVADO也备受关注和饱受争议。

2017-02-11 19:08:00 4986

4986 Xilinx Vivado工具支持仅将系统设计的一部分进行综合,即OOC(out of context)综合方式。OOC综合方式的流程就是将设计的某个模块单独完成综合操作,这会带来如下可能性

2017-03-21 09:50:30 5424

5424 无论此刻你是一个需要安装Xilinx Vivado工具链的入门菜鸟,还是已有license过期的Vivado老铁,今儿咱就借着这篇文章,把学习「Vivado如何获取License」这档子事儿给说通透咯~ 手把手教程,分三部分讲述。

2018-07-03 09:54:00 58889

58889

在ISE中称为ChipScope而Vivado中就称为in system debug。下面就介绍Vivado中如何使用debug工具。 Debug分为3个阶段: 1. 探测信号:在设计中标志想要查看的信号 2. 布局布线:给包含了debug IP的设计布局布线 3. 分析:上板看信号。

2017-11-17 14:05:02 56687

56687

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 4873

4873 Xilinx公司讲述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47:00 3416

3416

Vivado HLS 是 Xilinx 提供的一个工具,是 Vivado Design Suite 的一部分,能把基于 C 的设计 (C、C++ 或 SystemC)转换成在 Xilinx 全可编程芯片上实现用的 RTL 设计文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 6326

6326

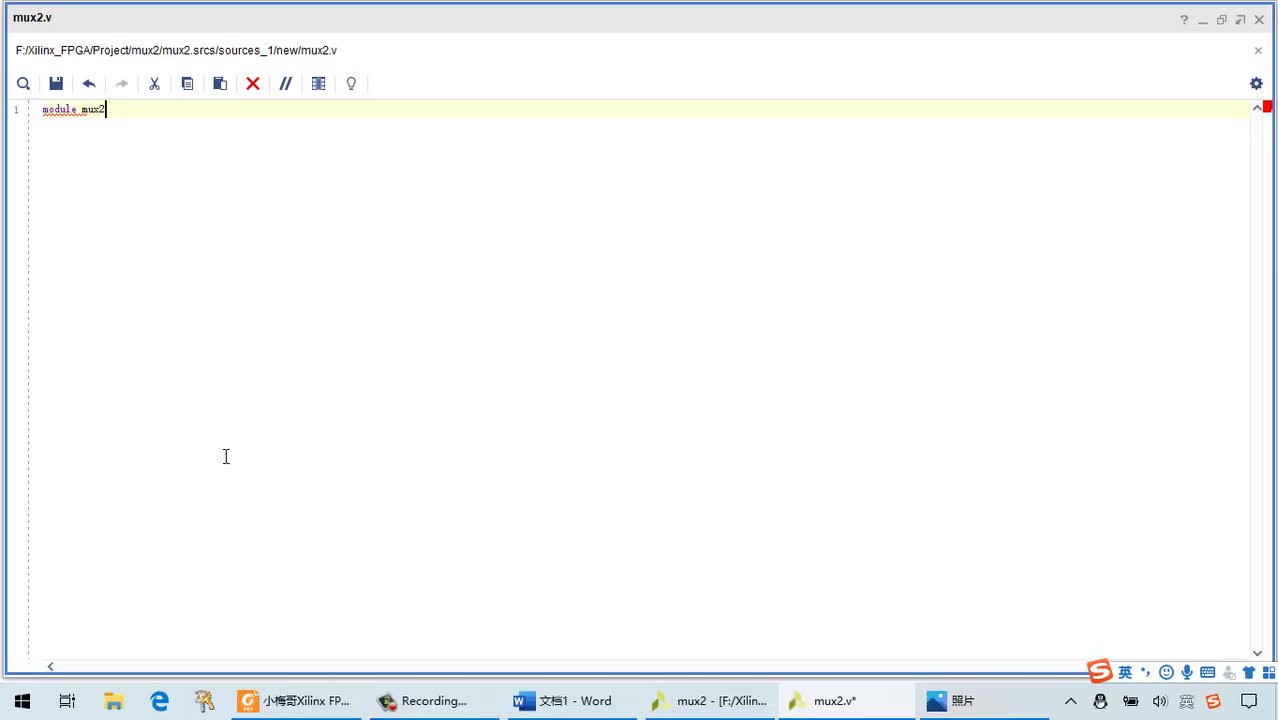

Vivado不仅是xlinx公司的FPGA设计工具,用它还可以学习Verilog描述,你造吗?

2018-09-20 09:29:22 9427

9427 本文通过一个简单的例子,介绍Vivado 下的仿真过程。主要参考了miz702的教程,同时也参考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 37132

37132 了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3062

3062 了解如何使用新的激活许可为Vivado工具生成浮动或基于服务器的许可证。

此外,了解如何查看,提供甚至将这些许可证返还给Xilinx

2018-11-22 07:06:00 3563

3563 介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 xilinx的Vivado工具也一直在更新,到本人记录此文的时候,Vivado已经有2017.3版本了,建议大家使用最新的Vivado工具。

2021-01-12 17:31:53 10

10 Xilinx_Vivado_zynq7000入门笔记说明。

2021-04-08 11:48:02 70

70 LOCK_PINS 是 Xilinx Vivado 做物理约束的属性之一。用来将LUT的逻辑输入(I0,,I1,I2...)绑定到其物理输入pin上(A6,A5,A4...)。

2023-01-11 10:52:24 768

768 Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 4755

4755 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 958

958 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

电子发烧友网站提供《为EBAZ4205创建Xilinx Vivado板文件.zip》资料免费下载

2023-06-16 11:41:02 1

1 Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

Xilinx Vivado工具的配置约束隐藏得比较深,如图1所示,在进入配置页面前,首先需要点击PROGRAM AND DEBUG->Generate Bitstream执行工程的全编译,然后点击IMPLEMENTATION->OpenImplemented Design进入实现页面。

2023-12-02 12:19:19 220

220

电子发烧友网站提供《使用P4和Vivado工具简化数据包处理设计.pdf》资料免费下载

2024-01-26 17:49:11 0

0

电子发烧友App

电子发烧友App

评论