0 引 言

由于数字逻辑系统功能复杂化的需求,单片系统的芯片正朝着超大规模、高密度的方向发展。对于一个大规模的数字系统而言,系统规模是基于各种逻辑功能模块的组合。但是,无论是时序逻辑系统,还是组合逻辑系统,或者组合/时序混合系统,从时间轴上来看,系统中的各个功能模块并不是时刻都在工作,而是根据系统外部的整体要求,轮流或循环地被激活或工作。并且,随着数字逻辑规模的扩大,在相同速度条件下,在一定的时间区间,其功能模块的平均使用率将下降。因此,系统设计应该从传统追求大规模、高密度的方向,转向如何提高资源利用率,用有限的资源实现更大规模的逻辑设计上来。可重构计算技术能够提供硬件的效率和软件的可编程性,它综合了微处理器和ASIC的特点,在空间维和时间维上均可变。

1 可重构技术概述

1.1 可重构的定义

可重构就是在电子系统的工作状态下,动态地改变电路的结构。这主要通过对系统中的可编程逻辑器件进行重新配置或者局部重新配置来完成。利用可重构技术,能在只增加少量硬件资源的情况下,使系统同时具有软件实现和硬件实现的优点。

1.2 可重构方式的分类

按照重构的方式,系统重构可以分为静态系统重构(Static Reconfiguration)和动态系统重构(Dynamic Reconfiguration)。

1.2.1 静态系统重构

静态系统重构是指目标系统的逻辑功能静态重载,只能在运行前配置的系统,如图1所示。

FPGA功能在外部逻辑的控制下,通过存储于存储器中不同的目标系统数据重新下载,从而实现芯片逻辑功能的改变。

1.2.2 动态系统重构

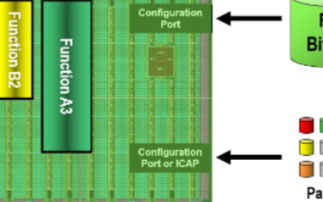

动态系统重构是指能在运行过程中实时配置的可重构系统,如图2所示。

对于时序变化的数字逻辑系统,其时序逻辑的发生不是通过调用芯片内不同区域、不同逻辑资源组合而成的,而是通过对具有专门缓存逻辑资源的FPGA进行局部或全局的芯片逻辑的动态重构而快速实现的。动态系统结构的FPGA具有缓存逻辑(Cache Logic),在外部逻辑的控制下,通过缓存逻辑对芯片逻辑进行全局或局部的快速修改,通过有控制重新布局布线的资源配置来加速实现系统的动态重构。就动态重构实现面积的不同,又可以分为全局重构和局部重构。

(1)全局重构。对FPGA器件或系统能且只能进行全部的重新配置。在配置过程中,计算的中间结果必须取出存放在额外的存储区,直到新的配置功能全部下载完为止,重构前后电路相互独立,没有关联。

(2)局部重构。对重构器件或系统的局部重新配置,与此同时,其余局部的工作状态不受影响。局部重构对减小重构的范围和单元数目,大大缩短重构时间,占有相当的优势。

2 基于FPGA的局部动态可重构技术

2.1 具有局部动态可重构功能的FPGA

过去大家普遍进行动态重构研究的FPGA主要有Xilinx公司的XC6200系列和Atmel公司的AT6000系列等。它们也是基于SRAM结构,但是SRAM的各个单元能够单独访问配置,即局部重构。它们的功能互不影响,因而具有局部重构的特征。这样做的优点显著,但也会付出增大硬件电路规模和功耗的代价。最终要实现电子系统的完全实时重构,应采用结构上具有动态局部重构功能的FPGA器件,如Xilinx公司的Virtex-4系列。

2.2 基于FPGA局部动态可重构技术主要特征及典型原理

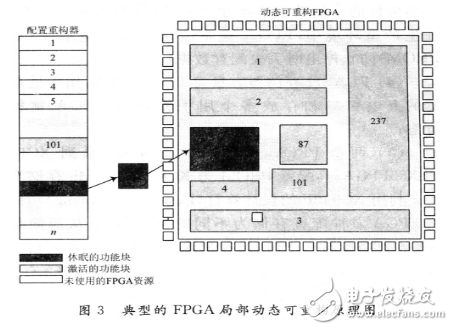

FPGA局部动态可重构技术的特征就是将整体按功能或按时序分解为不同的组合,并根据实际需要,分时对芯片进行局部动态重构,以较少的硬件资源实现较大的时序系统整体功能。图3给出一种典型的FPGA局部动态可重构。由图3可以看出,在外部逻辑的控制下,可以实时动态地对芯片逻辑实现局部重构。通过控制布局、布线的资源,实现系统的动态重构。

2.3 FPGA实现局部动态可重构的结构要求

要使FPGA有效地实现实时系统动态重构,FPGA在结构上必须满足以下要求:

(1)不仅具有可重新编程能力,同时可动态进行系统资源地重新配置,而不会破坏器件中全局或局部逻辑操作能力。很多传统的FPGA把配置数据存放在外部的串行EPROM中。这种方式有3个缺点:重构之前整个FPGA必须停止工作;只是对整个FPGA进行重构;重构时FPGA中以前的内部状态无法保存。新的能够实现动态可重构的FPGA不需要在重构之前触发复位信号,而是将FPGA芯片中的一局部逻辑电路的时钟关闭,然后重新配置逻辑电路,最后恢复时钟信号。

(2)FPGA内部配置信息对称,记载任何时刻,任何通用的基本逻辑功能可以配置于器件的任何一个位置,运用简单模型组合去实现设汁中的复杂功能。

3 基于FPGA的可重构演示系统的设计与实现

3.1 演示验证系统的硬件组成及各部分功能

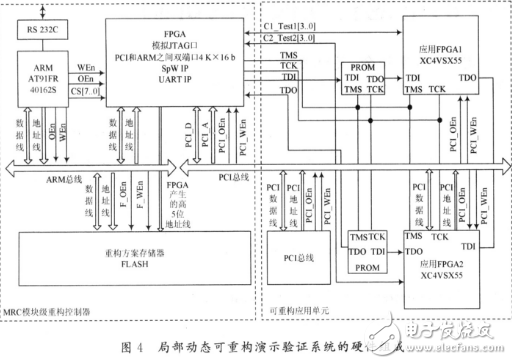

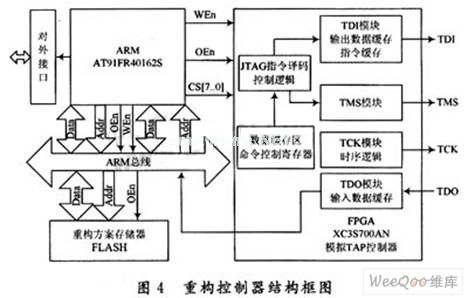

(1)演示验证系统的硬件组成,如图4所示。ARM处理器片内具有256 KB的片上SRAM存储器、2 MB容量FLAsH存储器。主要是对sPARTEN-3AN系列的FPGA进行控制,控制其调取FLASH存储器中的重构方案;FLAsH存储器的并行数据通过ARM转换成串行;ARM中自带的FLAsH存储器用来存放程序;

(2)SPARTEN3AN系列的FPGA,是基于非易失性存储的FPGA,主要作为PCI总线和ARM处理器之间的双端口;放置Spw IP核、UART IP核、1553 IP核;模拟JTAG口;

(3)两个XCVSX55的FPGA专用JTAG,进行配置文件的下载。Xilinx FPGA基于SRAM技术,因此是易失性的。如果关掉器件的电源,其配置就会丢失。在生产型环境中,FPGA通常使用外部存储器件(如PROM)防止停电时丢失配置数据;

(4)FLASH存储器容量为16 M×32 b,用于处理器的上电引导和存放多个用于模块级FPGA重构方案;

(5)两个PROM-XCF32P。Virtex4系列XC4-VSX55FPGA,其配置PROM为XCF32P,32 Mb存储容量。利用XCF32P的设计修订(Design.Revisiorling)功能将FPGA多种配置存储为不同的修订版本,从而简化FPGA配置更改。上电时,由配置PROM的内部逻辑对设计修订版本选择输入(引脚或控制位)进行采样;

(6)两组测试线,每组4根,cl_Test[3..O]和C2-Testl[3..O]分别测试两个XCVSX55系列FPGA的重构和反馈重构结果;

(7)两通道的PROM控制信号线,C1(C2)_PROG,C1(C2)_DIN,C1(C2)_DONE,C1(C2)_INT,C1(C2)_CCLK用于实现两个XCVSX55系列FPGA的PROM方式的下载。由于JTAG(边界扫描)链在其中一个部件发生故障时会影响整个JTAG链的正常功能,因此多使用:PROM的下载方式备用;

(9)PCI总线,通过该总线实现计算机与外界交互的外部接口。

3.2 演示验证系统的工作原理

3.2.1 上电复位

在上电复位时,要确保ARM和FPGA同步复位。Xilinx公司的FPGA上电时需要200 ms左右的配置时间,在此期间I/O引脚处于三态状态,因此对关键的输入/输出信号(如IRQx,NWAIT,2.56兆输出数据及输出时钟)有必要采取的上下拉,以确保ARM及外围接口信号处于正常的状态,避免信号冲突。

3.2.2 初始化

主要的初始化工作有2部分,分别由ARM和FPGA完成。

(1)ARM执行的初始化工作。包括监控程序自举→监控程序执行ARM内部寄存器初始化→硬件自检→加载标志检测→(软件更新加载)→FPGA参数设定→用户软件加载及完整性正确性校验→控制权叫用户软件→用户软件初始化→用户软件运行。

(2)FPGA执行的初始化工作。主要有FPGA内部寄存器和逻辑状态的初始值、内部缓冲区数据清零依靠复位信号来完成。其中的“FPGA参数设定”由监控程序负责执行或由FPGA使用缺省参数完成。数据融合格式、输入/输出码速率等FPGA参数存储在ARM的片内FLASH中的FPGA参数区中,上电或复位时有监控软件负责加载和初始化。

3.2.3 重构过程

可重构演示验证系统的结构如图4所示,当出现错误和发生故障时,由ARM处理器读取FLASH存储器中的重构方案。但是,FLASH存储器取舍众多重构方案却是受外部1553B,Spw,UART的控制。由ARM处理器更新FLASH存储器或给完成并/串转换的FPGA发出控制命令来对可重构应用单元进行操作。模拟JTAG口的FPGA与两个应用FPGA的JTAG口边界扫描链(Boundary-Scan Chain),在ARM处理器的控制下,对被重构的FPGA进行重构。FPGA的主要任务是通过ARM控制器将事先存入FLASH中逻辑系统的不同功能配置信息,按用户的系统时序要求和外部控制,逐一下载到SRAM编程的FPGA之中,以实现系统功能的动态局部重构。在系统工作过程中,FPGA将根据不同的要求,在处理器的控制下,不断重构其逻辑功能,通过模板级重构,满足不同数字图像处理和其他逻辑运算的要求。

3.3 实现局部动态可重构的FPGA的选型和配置模式

3.3.1 Xilinx公司的Virtex-4系列FPGA

在选择器件时,必须保证器件资源留有一定余量,这样不仅可以避免布线拥挤,也便于测试修改和功能扩展。根据系统的需求和扩展性,选择Virtex-4系列FPGA。它是Xilinx公司推出的一系列实现动态局部重构的FPGA芯片,也是基于查找表的。Virtex-4系列芯片将高级硅片组合模块(ASMBL)架构与种类繁多的灵活功能相结合,大大提高了可编程逻辑设计能力,从而成为替代ASIC技术的强有力产品。采用Virtex-4选用Xilinx公司的Virtex-4系列产品XC4VSX55。XC4VSX55具有128列×48行阵列,55 296个逻辑单元,24 576个Slice,最大分布式RAM384 KB,512个XtremeDSPSlice),320个18 KB块RAM,最大块RAM存储容量5 760 KB,8个DCM,4个相位匹配时钟分频器(PMCD),13个I/O组,最大用户I/O数640个。根据目前已有的算法,其性能和资源可以较好地满足图像匹配算法和目标识别算法对硬件资源(逻辑门数、RAM大小、乘法加法器等)的需求。Virtex-4硬IP核块的庞大阵列包括PowerPC处理器(带有新型APU接口)、三态以太网MAC,622 Mb/s到6.5 Gb/s串行收发器、专用DSP S1ice、高速时钟管理电路和源同步接口块。

3.3.2 Virtex-4系列FPGA在该系统中的配置模式

Virtex-4器件的配置方法是用串行从模式、串行主模式、SelectMAP从模式、SelectMAP主模式、边界扫描模式(JTAG)之一将比特流载入内部配置存储器的:在该系统中采用可重构应用单元的FPGA配置模式有两种:

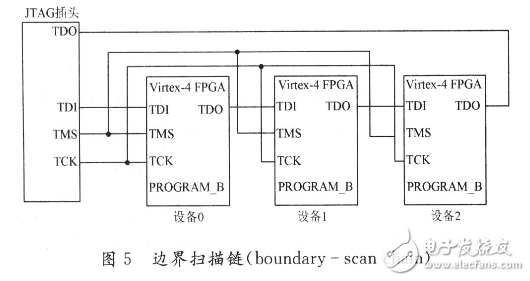

(1)JTAG方式(边界扫描方式)

通过SPARTEN-3AN系列中FPGA提供的外部逻辑驱动JTAG专用引脚与同样4个JTAG引脚的两个应用FPGA及配置它们的PRROM串联起来,形成边界扫描链(Boundary-Scan Chain)将配置数据下载到FPGA中。在这种模式下,数据以每TCK一位的速度加载,如图5所示。

JTAG或边界扫描模式是一种行业标准的(IEEE1149.1或1532)串行编程模式。该模式通过电缆、微处理器或其他器件提供的外部逻辑驱动JTAG专用引脚TCK和JTAG测试时钟输入。当TCK保持在零状态时,测试逻辑状态应保持不变;TMS为测试模式选择,控制JTAG状态。出现在TMS的信号在TCK的上升沿由测试逻辑采样进入测试访问口(Test AccessPort,TAP)控制器;TDI:测试数据输入,测试数据在TCK的上升沿采样进入移位寄存器(SR);TD0:测试数据输出,测试结果在TCK的下降沿从移位寄存器(SR)移出,输出数据与输入到TDI的数据应不出现倒置。这种模式因其标准化程度和可通过同样4个JTAG引脚为FPGA编程的能力而广泛使用。JTAG方式常用于实现在线编程(In-System Programma-ble,ISP),对FPGA进行编程。

JTAG在线编程的特征也改变了传统生产流程,将以前先对芯片进行预编程再装到板上的工艺简化为先固定器件到电路板上,再用JTAG口进行编程。Xilinx的Virtex-4系列支持在一个边界扫描(JTAG)链中配置多个FPGA,每次,只配置链中的1个FPGA,大大降低了实现难度。

(2)PROM配置模式,是由SPARTEN3AN系列FPGA为每一个Virtex-4系列FPGA配置一组PROM控制线实现FPGA的下载。SPARTEN3AN系列FPGA和可重构应用单元的每一个virtex-4系列FPGA之间分别有一组PROM的控制线,每组都包括DIN(配置数据输入)、CCLK(配置时钟)、DONE(FP-GA配置完成)、PROG(触发重配置)、INT(配置初始化)5个信号,通过这些信号将配置数据下载到Virtex-4系列FPGA中去。两种方式互补,在边界扫描链发生断裂影响到整个链的功能时,可以使用PROM模式替补,提高了重构过程的可靠性。

4 结 语

基于SRAM的FPGA的问世标志着现代可重构技术的开端,并极大地推动了其发展。可编程FPGA可以根据不同算法设计合理的硬件结构,以达到提高执行效率的目的。动态可重构FPGA可以在程序运行中动态完成FPGA的不同配置电路功能,在不同时段执行不同的算法,实现了虚拟硬件可重构计算技术。这里提出的通过微处理器加FPGA结合串行菊花链实现可重构的方式,实现了动态可重构FPGA结构设计的一种应用。另外,该验证演示了系统中可重构控制器还可以结构模块化,能够工程化应用于其他设计中,具有灵活及可移植性强的优点。

电子发烧友App

电子发烧友App

评论