英商康桥半导体宣布全新的一次侧感应 (PSS) 返驰式控制晶片系列,可以大幅度降低高功率应用设计的系统成本及零组件数量,同时也提供绝佳的轻载及待机效率性能。

2012-09-11 09:26:16 1862

1862 在FPGA上使用OpenCL标准,与目前的硬件体系结构(CPU、GPU,等)相比,能够大幅度提高性能,同时降低了功耗。此外,与使用Verilog或者VHDL等底层硬件描述语言(HDL)的传统FPGA

2014-05-26 09:10:18 3967

3967 降低至少一半;性能与容量翻番;采用的目标设计平台则大幅度提高了生产率;并且越来越少的设计人员选择使用ASSP;ASIC同样也难逃厄运。总之,其前景可谓是一片“光明”。 当然,想要一直保持“光明”状态

2012-09-21 13:46:16

可编程逻辑的灵活性。可以有效降低系统功耗和成本,减小电路板面积,同时满足性能要求。而且采用内置纠错码(ECC)和存储器保护功能,保护用户的系统不受硬件或者软件错误的影响,从而提高了系统可靠性

2014-08-01 14:12:39

电源引脚布局减小了22%,功耗降低了35%。图1 2.有效应对噪声敏感输入 因为FPGA中许多模块对供电电源噪声非常敏感,而噪声会导致产生抖动,随之带来很高的误码率(BER),降低了电路性能,而

2018-10-23 16:33:09

,采用低K值电介质工艺,不仅提高了性能还降低了寄生电容。结构的改变,如增强的逻辑单元内部互连,可实现更强大的功能,而无需更多的功耗。StraTIx II更大的改变是采用了六输入查找表(LUT)架构,能够

2015-02-09 14:58:01

µs减小到5µs。这意味着显著提高了功效,对应驱动90%的总体运行成本。在这个例子中,SoC的功耗大约比三芯片方案低37%。图4a图4bSoCFPGA增强了系统功能,通过集成降低了系统总成本。通过在一

2021-07-14 08:00:00

30多年,但是由于 HDL 是一种用形式化的语言描述极其复杂的数字系统的,抽象级别较低,因而大大提高了编程难度,限制了FPGA 的推广和普及。其次随着系统级 FPGA 和片上系统(SoC)的出现

2018-08-10 09:16:48

多年,但是由于 HDL 是一种用形式化的语言描述极其复杂的数字系统的,抽象级别较低,因而大大提高了编程难度,限制了FPGA 的推广和普及。其次随着系统级 FPGA 和片上系统(SoC)的出现和迅速发展

2018-08-13 09:31:45

复杂度日益增加的系统设计要求高性能FPGA的设计与PCB设计并行进行。通过整合FPGA和PCB设计工具以及采用高密度互连(HDI)等先进的制造工艺,这种设计方法可以降低系统成本、优化系统性能并缩短

2018-09-21 11:55:09

集成度、高性能、低功耗FPGA器件的需求。设计人员更喜欢网络通信而不是点对点通信,这意味着可能需要额外的控制器用于通信,进而间接增加了BOM成本、电路板尺寸和相关NRE(一次性工程费用)成本。总体拥有成本

2019-06-24 07:29:33

期中看不到明显的数据变化。这类方法能够显著降低功耗,不需要来自系统其它部分的任何输入,对性能也不会有任何影响。其它方法则需要来自系统管理硬件或者软件的大量帮助。一个例子是动态电压频率调整(DVFS

2014-09-02 14:51:19

变系统逻辑的情况下接地或接电源。(4)对单片机使用电源监控及看门狗电路,如:IMP809,IMP706,IMP813, X25043,X25045等,可大幅度提高整个电路的抗干扰性能。(5)在速度能

2015-05-07 14:26:19

应用系统使用了更多的功率元件,以及封装密度的不断提高,先进的冷却技术变得更加重要。我们用独特的方法把热界面材料和电路板的屏蔽产品结合起来,用于制造更加可靠的电子产品,例如PDA、 移动电话和便携式DVD

2018-08-31 11:53:58

够集成整个芯片系统(SoC),与分立的MCU、DSP、ASSP以及ASIC解决方案相比,大幅度降低了成本。不论是用作协处理器还是SoC皆具备不可取代的独特优势。那么,这些器件之间差异性在哪里呢?一位资深

2014-07-24 11:18:05

SoCFPGA器件在一个器件中同时集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA方法的优点。

2019-09-26 07:59:27

通过最大化可用的电压和降低功耗(请参阅下面的温度计比较),理想二极管桥简化了电源设计和降低供电成本,尤其是在低电压应用。一个理想二极管桥也消除了热设计问题,昂贵的散热片,并大大降低了印刷电路板面积。

2019-10-23 09:10:25

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2020-03-05 07:01:34

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2019-09-24 07:09:13

宽压供电设计。MM32F系列是灵动微新一代MM32系列中率先升级推出的通用高性能MCU平台。全新MM32F系列和经典MM32F引脚兼容,并在系统性能、功能扩展、可靠性、稳定性上获得了大幅度提升,ESD

2021-09-02 08:16:20

。Quartus II软件v13.1大幅度优化了算法,增强了并行算法,提高了您的多处理器计算机上多个内核的性能。 图1显示了自从2011年以来,高端器件在Quartus II软件上的基准测试结果。 图

2013-11-13 15:34:26

This paper discusses how Vivace Networks uses ScanWorks at the benchtop and at in-circuit test to reduce test costs and accelerate time to market in a competitive environment.

2019-08-08 07:07:06

进行远程监测、远程控制、远程维护和管理。内嵌于设备的Web服务器可以提供统一的基于浏览器方式的操作和控制界面,界面直观易操作,大大降低了软件系统和通信系统的设计、维护工作量,节省了人员培训费用,提高了现场监测和控制设备的管理水平。

2019-08-02 08:19:18

从Xilinx公司推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其

2019-09-20 06:33:32

MPCoreTM处理器,以及丰富的硬件外设,从而降低了系统功耗和成本,减小了电路板面积。基本描述如下: (1)28nm FPGA实现了业界最低系统成本和功耗 (2)三种型号:仅逻辑、3G收发器和5G收发器

2012-09-21 13:49:05

的功耗。对于第二种挑战,通常通过降低产品原材料 (BOM)中元器件的成本来降低现有成功产品的成本。设计团队的另一选择是重新设计产品,不是针对新功能,而是要大幅度的降低成本。

2019-08-09 07:41:27

TriQuint是一个高性能射频解决方案的领导者,其产品涉及复杂移动设备、国防与航天应用以及网络基础设施等方面。现在,TriQuint通过使用GaAs、GaN、SAW和BAW技术为世界各地的组织提供创新的解决方案。工程师和科学家借助TriQuint的创新提高了产品的性能,并降低了其应用的总成本。

2019-08-16 08:14:37

本文介绍双通道数字式磁隔离器ADUM1201在CAN总线通信系统中的应用,由于ADUM1201的优良特性,用ADUM1201代替传统的光电隔离器件,降低了系统功耗,简化系统结构,增加了系统稳定性,提高了系统的性能。

2021-05-31 06:52:41

反对法多福多寿发的发大幅度反对法大幅度

2013-09-13 23:18:54

µs减小到5µs。这意味着显著提高了功效,对应驱动90%的总体运行成本。在这个例子中,SoC的功耗大约比三芯片方案低37%。图4a图4bSoCFPGA增强了系统功能,通过集成降低了系统总成本。通过在一

2021-07-12 08:00:00

CPU内核。如何大幅度减少实施时间?我有什么选择可以改变以加快它吗?以上来自于谷歌翻译以下为原文The implementation process is a time-consuming

2018-10-17 11:59:47

本文基于Viitex-5 LX110验证平台的设计,探索了高性能FPGA硬件系统设计的一般性方法及流程,以提高FPGA的系统性能。

2021-04-26 06:43:55

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

的TCO 直接提高了毛利润,从而减缓了当今大部分设计团队所面临的压力。图1. 有利于降低TCO 的一些构建模块FPGA 降低了TCO为阐述Altera Cyclone 系列FPGA 是怎样降低TCO

2013-11-13 11:17:35

复杂器件专业技术相结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。此外,TPACK提供的芯片解决方案可以导入到最新的FPGA中,进一步降低功耗。最终实现

2019-07-31 07:13:26

有什么方法可以提高片上系统级集成吗?有什么方法可以降低物料成本吗?

2021-05-14 06:20:23

对于各种不同的数据中心工作负载,FPGA 可以显著提高性能,最大程度减少附加功耗并降低总体拥有成本 (TCO)。

2019-10-10 07:46:05

能保持静止,然后过一会儿突然一下就大幅度的来回走动,然后重新启动后就直接大幅度来回走动了。设定的movement=0;if(Turn_Off(Angle_Balance,Voltage)==1

2019-05-19 21:36:39

自己做了一个电路板,因为功耗除了点问题,怎么降低电路板功耗呢

2019-08-07 22:21:34

从当前嵌入式消费电子产品来看,媒体处理与无线通信、3D游戏逐渐融合,其强大的功能带来了芯片处理能力的增加,在复杂的移动应用环境中,功耗正在大幅度增加。比如手机,用户往往希望待机时间、听音乐时间,以及看MPEG4时间能更长。在这样的背景下,如何降低入式芯片的功耗已迫在眉睫。

2019-08-28 08:27:58

从当前嵌入式消费电子产品来看,媒体处理与无线通信、3D游戏逐渐融合,其强大的功能带来了芯片处理能力的增加,在复杂的移动应用环境中,功耗正在大幅度增加。比如手机,用户往往希望待机时间、听音乐时间,以及看MPEG4时间能更长。在这样的背景下,如何降低嵌入式芯片的功耗已迫在眉睫。

2019-09-18 06:22:27

本文运用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技术构建软件无线电平台。大大提高了数字信号处理的能力和速度,并且降低了系统功耗,缩小了系统体积,为更高层次的3G无线通信要求提供了解决方案。

2021-05-06 06:21:24

据的擦除、修改,只需更改代码,无需改变电路结构,降低了系统成本,同时简化了系统的复杂性,提高了系统工作的稳定性。

2021-05-20 07:00:52

蒸汽轮机或水轮机的发电原理是什么?有什么方法可以大幅度提升发电机的发电量呢?

2021-06-30 06:49:48

性以及高可靠性,它是一个被广泛使用的针对于FPGA上的单粒子翻转(Single-EventUpset,SEU)的容错技术。文献中表明TMR大幅度提高了FP-GA在SEU影响下的可靠性。尽管TMR能有效提高

2019-08-27 07:28:32

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2021-04-26 07:01:55

nm SoC封装到一个20 nm管芯中,结果是减小了芯片间延时,降低了I/O功耗,以及电路板级成本,这说明单位晶体管成本的提高是有好处的。而不明显的是,规划人员通过使用晶体管来提高性能或者能效。一个

2014-09-01 17:26:49

发发大幅度发大厦

2015-11-28 11:22:20

,会使系统的稳定性大幅度提高。一般应在电源进入印刷电路板的位置和靠近各器件的电源引脚处加上几十到几百IlF的电容,以滤除电源噪声。还要注意在器件的电源和地之间加上0.1μF左右的电容,用来滤除元器件工作

2018-09-05 16:38:26

Altera20nmArria10FPGA和SoC中,以及14nmStratix10FPGA和SoC中。该新功能支持设计人员以相同的定点性能和效率在浮点中实现其算法,且不会对功耗、面积或者密度产生任何影响,也不会损失定点特性或

2019-07-03 07:56:05

被动门禁 (Passive Entry, PE)系统在汽车舒适度和安全性方面正在引领一个新的发展趋势。尽管这种技术几年前就已经问世了,但直到最近才开始快速流行,主要是因为系统集成度不断提高,使系统成本得以大幅度降低。

2019-08-23 06:03:43

。面向 Arria 10 等高端 FPGA 的电源管理解决方案应该谨慎选择。 一个经过精心计划的电源管理设计可以减小 PCB 尺寸、减轻重量并降低复杂性,同时降低功耗和冷却成本。这对优化系统性能而言

2018-10-15 10:30:31

端 FPGA 的电源管理解决方案应该谨慎选择。 一个经过精心计划的电源管理设计可以减小 PCB 尺寸、减轻重量并降低复杂性,同时降低功耗和冷却成本。这对优化系统性能而言是必不可少的。 例如,为图

2018-11-20 10:46:52

,大幅度降低了成本。不论是用作协处理器还是SoC,Altera FPGA在您的工业应用中都具有以下优点: 1. 设计集成——使用FPGA作为协处理器或者SoC,在一个器件平台上集成 IP和软件堆栈

2014-11-05 14:03:37

是,硬核IP模块功耗降低了65%,而性能提高了50%,表1列出了Cyclone V FPGA中的硬核IP功能,以及通过硬核实现所节省的资源量。表1 Cyclone V FPGA中的硬核IP功能 硬核IP

2015-02-09 15:02:06

工业电子产品的发展趋势是更小的电路板尺寸、更时尚的外形和更具成本效益。由于这些趋势,电子系统设计人员必须降低印刷电路板(PCB)的尺寸和成本。使用现场可编程门阵列(FPGA)和片上系统(SoC

2019-03-08 06:45:06

在高速电路中推荐使用多层电路板。首先,多层电路板分配内层专门给电源和地,因此 具有如下优点: · 电源非常稳定; · 电路阻抗大幅降低; · 配线长度大幅缩短。 此外,从成本角度考虑

2018-11-23 16:04:04

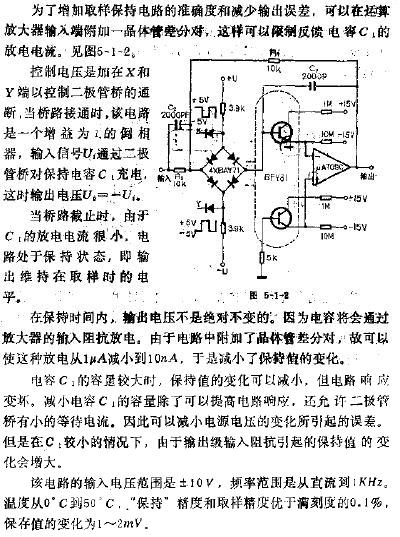

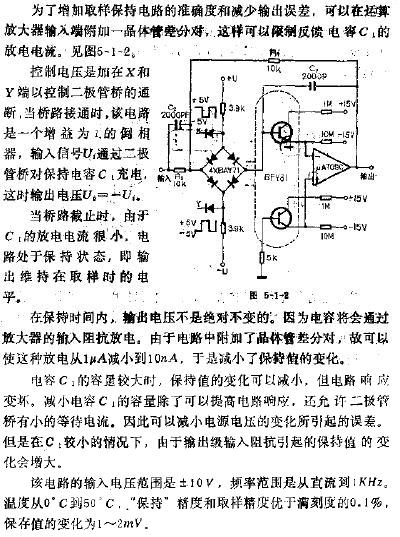

提高了准确度的取样保持电路

2009-04-11 10:51:58 668

668

光纤接入组网方案让网速大幅度提高

随着网吧行业的发展,竞争也越来越激烈,要在激烈的竞争中立于不败之地,设计和组建一个稳

2010-04-14 13:51:56 1886

1886 MAX6581 精度、8通道温度传感器,有效降低电路板面积

2010-09-17 13:23:04 973

973 自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。降低FPGA功耗是缩减封装和散热成本、提高器件可靠性以及打开移

2011-03-15 14:58:34 31

31 2012年4月11号,北京——Altera公司(Nasdaq: ALTR)今天宣布,goHDR作为FPGA OpenCL计划的早期试用客户,通过Altera的FPGA OpenCL计划,大幅度缩短了开发时间,显著提高了性能。与Altera密切

2012-04-12 08:58:10 705

705 Cadence公司宣布Renesas微系统有限公司已采用Cadence Encounter RTL Compiler用于综合实现。其优势在于将复杂ASIC设计的芯片利用率提高了15%,面积减少了8.4%,加速了实现周期并降低了成本。

2012-12-14 10:59:15 1008

1008 接通功能,集成了闪存,适用于远程更新和系统管理功能。

模数转换器(ADC),降低了系统成本,减小了电路板面积。

小外形封装,集成器件,减小了引脚布局。

可定制处理器外设组,提高了功效。

2016-01-06 10:22:08 39

39 楔式制动器设计提高了线控刹车的性能

2017-01-24 15:44:12 12

12 那么这项很吓人的技术到底是什么,现在似乎也有了些眉目。根据内部人士的爆料,这项“很吓人的技术”就是借助黑科技使得图形图像的性能,以及玩游戏的性能得到极大幅度的提升,据说速度快到不可思议。当然,这里所说的黑科技借助对系统底层的优化,辅以芯片上的支持,从而逆转过去麒麟处理器在GPU性能方面的不足。

2018-05-28 12:32:00 4503

4503 如何让汽车上的LED适应越来越严苛的环境?近日全球知名半导体制造商ROHM发布了业界首款完全无银的高亮度红色LED“SML-Y18U2T”,大幅度的提高了汽车灯具尤其是刹车灯在严酷环境下使用的可靠性

2018-05-30 11:35:00 2119

2119 Vivado HLS有助于降低整体系统功耗,降低材料成本,提高系统性能并加快设计生产率。

我们将向您展示如何使用C,C ++或SystemC创建更高效的规范。

2018-11-27 06:43:00 3392

3392 特斯拉大幅度降价 为何

2019-03-04 14:48:02 687

687 Altera公司今天宣布,NEC将使用Altera的 28nm FPGA,进一步提高了其长期发展(LTE)基站的性能,支持无线服务供应商高效的管理他们的网络。

2019-05-14 15:34:45 774

774 对于电动汽车而言,电池占据了车辆30%到40%左右的用车成本,如果电池成本大幅度下降,电动车会逆袭燃油车吗?

2019-12-26 10:07:58 780

780 2月28日,美国泛林公司宣布与ASML阿斯麦、IMEC比利时微电子中心合作开发了新的EUV光刻技术,不仅提高了EUV光刻的良率、分辨率及产能,还将光刻胶的用量最多降至原来的1/10,大幅降低了成本。

2020-02-29 11:20:58 3228

3228 的笔记本电脑和台式机提供最高的BOM集成度,在缩小电路板面积的同时,还能降低OEM厂商的成本。此外,新的EZ-PD控制器还支持最新的USB4™标准和Intel Thunderbolt™平台。

2020-03-04 14:16:15 2594

2594 在PCB电路的开发阶段,通常要经历几次电路设计送代,包括测试、再设计、重新加工电路等。这些多次的更改可能导致成本上升项日从开始开发到推出市场经历4次到8次的更改并不少见。比较惯用的方式是使用电路仿真软件做好精确的仿真从而可以大幅度减少变更次数和相关成本。

2020-07-17 10:25:00 3

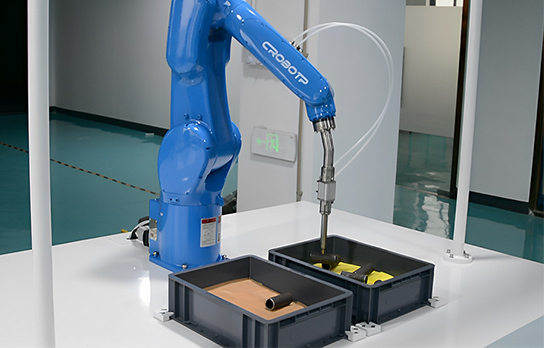

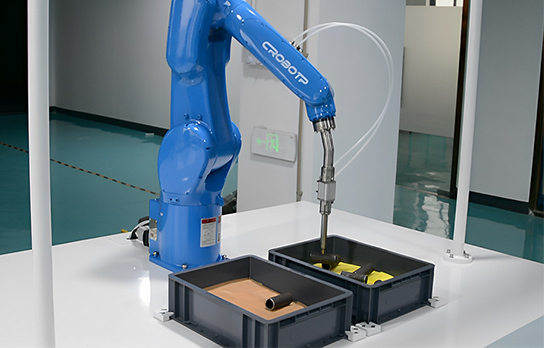

3 视觉系统和机器人移动机构,实现了抓取不同尺寸、形状和重量的零件,并且可以在保证生产节拍的同时实现无损拾取,大大提高了生产企业的效率,降低了成本。 danikor的研发团队在材料的选型和制备上进行了系统化的探索,通过对各种高分子材料的配比

2020-12-11 08:46:04 810

810 高线性度下变频混频器使 3G 和 4G 无线基站的性能提高并降低了功耗

2021-03-21 10:18:10 3

3 高精度(±1°C)温度传感器提高了系统性能和可靠性

2021-05-27 09:56:09 2

2 集电容式触控和主机控制器功能,节约时间、成本以及电路板空间

2022-11-01 08:25:27 0

0 带抽头电感的离线降压转换器提高了性能

2022-11-14 21:08:21 1

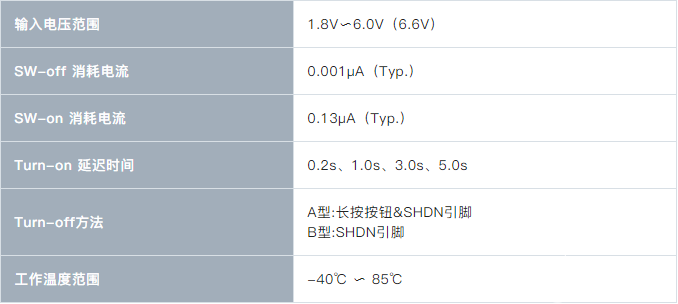

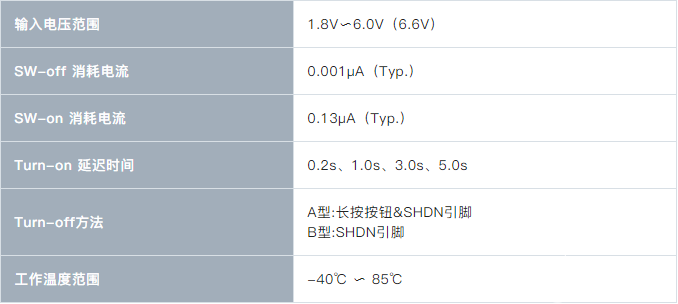

1 XC6193/XC6194系列产品是能大幅度降低出厂后待机时及电源OFF时消耗的电力、并且在系统死机时能关闭电源的智能负载开关。有利于机器节电、延长工作时间。

2022-11-19 19:04:21 315

315

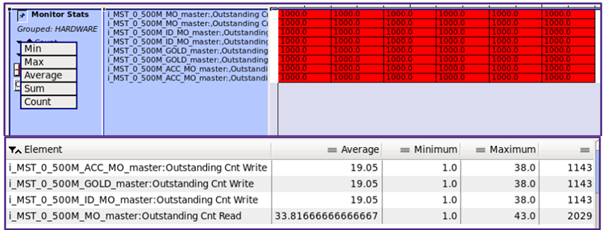

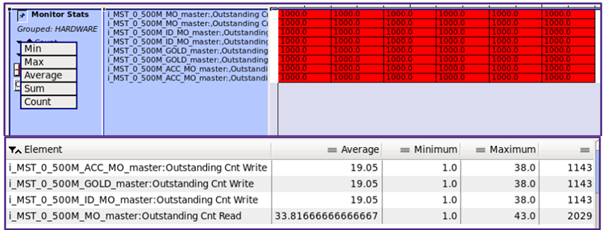

在使用 AXI 总线移动大量数据的 SoC 中,AXI 总线的性能可能会成为整体系统性能的瓶颈。SoC 中日益增加的复杂性和软件内容,因此需要使用实际数据有效载荷在硅前进行左移性能验证。硬件辅助验证

2023-05-25 15:37:52 544

544

3D视觉引导金属圆管无序抓取,不仅提高了生产效率,降低了成本,还大幅度提升了作业的精确性和安全性。

2023-07-11 15:54:44 206

206

电子发烧友App

电子发烧友App

评论