在需要多个FPGA芯片的应用中,如果JTAG链上所有FPGA采用相同配置,可以通过“成组”加载方式同时加载;

2023-02-20 10:18:27 3783

3783

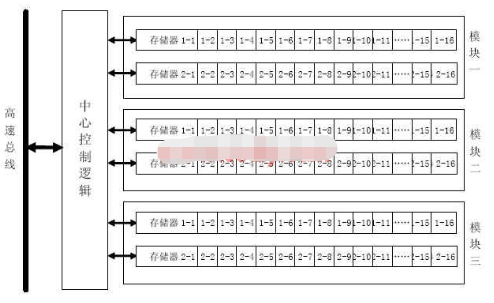

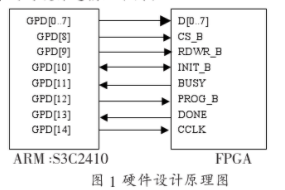

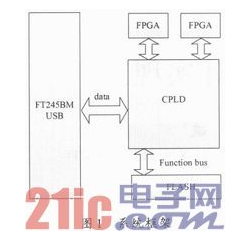

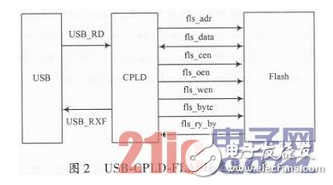

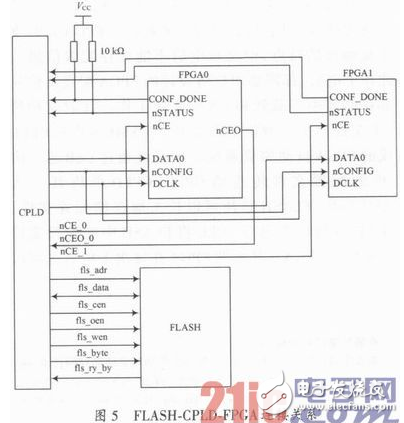

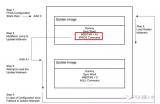

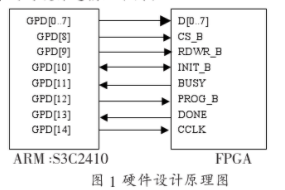

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。##在设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示。

2015-01-30 16:54:39 2847

2847 大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2019-07-01 17:16:45 16228

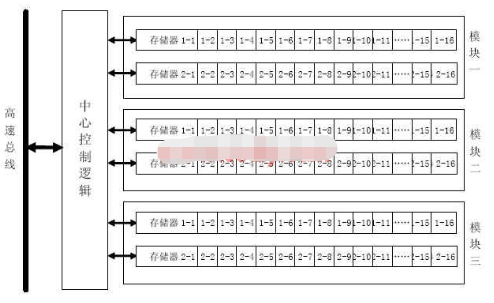

16228 本文介绍了一种以FPGA作为控制器,FLASH MEMORY作为主存储器的大容量高速存储系统方案,并对关键技术及实现途径进行了论述,在存储容量及存储速度上实现了突破。

2020-07-30 17:53:54 1917

1917

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2022-10-24 14:52:00 612

612 目前,大多数 FPGA 芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常

2022-12-26 18:10:00 1780

1780 本帖最后由 eehome 于 2013-1-5 09:51 编辑

9222方案设计资料

2012-08-20 11:35:26

FPGA(Field Programmable GateArray)即现场可编程门阵列,随着微电子技术的发展,FPGA的性能变的越来越优越,应用空间也变得越来越广。FPGA具有支持重复编程的特点

2019-09-25 07:12:16

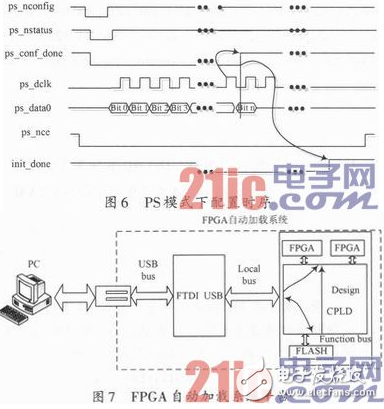

的FPGA 从并加载方案,相对于其它几种加载方式,虽然加载管脚增多,但加载时间大大缩短,并且如果提高CPU 局部总线的写速度,加载速度有进一步提高空间,满足通信系统快速启动的要求,具有很高的实用价值。

2019-07-12 07:00:09

1 SPARTAN-6 从并加载流程3]4]5 结束语使用基于CPLD 的FPGA 从并加载方案,相对于其它几种加载方式,虽然加载管脚增多,但加载时间大大缩短,并且如果提高CPU 局部总线的写速度,加载速度有进一步提高空间,满足通信系统快速启动的要求,具有很高的实用价值。

2019-06-14 06:00:00

1. 如何实现FPGA局部动态加载。2. pcie部分不变,实现部分程序加载。3. 目前是通过JTAG线,通过PCIE加载的FPGA程序。4. 现在是想通过更改bin文件,不通过JTAG的方式加载。

2021-03-08 09:32:33

, 为企业的现代化管理提高效率。 1称重系统总体方案设计 首先, 利用由电阻应变式传感器组成的测量电路测出压力信号, 经过信号的放大、滤波, 然后以模拟信号的方式传送到A /D转换器。其次, 将经

2018-11-05 11:09:37

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行

2019-07-18 08:10:11

详解赛灵思All Programmable Smarter Vision解决方案

2021-06-02 06:56:12

AG6310方案设计原理是什么?AG6310技术应用是什么?怎么实现DP转HDMI方案的设计?

2021-05-28 06:15:12

`MTK方案设计出来了`

2019-10-17 11:34:03

OpenHarmony 小型系统中提供基础组件image,但是只能加载png或者jpg类型的图片,有什么方案可以加载gif的图片?

2022-04-19 10:13:55

ROCm移动WLAN解决方案详解

2021-06-01 06:34:35

在工业、电力、自动化及仪器仪表实际应用中,RS-485总线标准是目前业内应用最广泛的物理层总线设计标准之一。为了确保数据端口能够在极其恶劣的电磁环境中正常运行,RS-485端口防护方案必须符合相关

2020-01-03 17:34:38

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

2020-12-22 07:58:55

曾经参加过“第九单片机活动”:【WIZnet竞赛方案设计类】--电梯远程监控系统! 因为时间有限 没有实物,只是方案,流程和硬件图纸!这次希望能有W5500模块的支持 把项目搞上去!资料见附件!

2014-04-29 16:15:25

总线广泛地应用于工业控制、军用系统、航空航天、交通运输和医疗领域。本文提出了基于FPGA的VME总线和CAN总线之间的传输转换方案,满足一些特殊工业环境的需要,具有一定的研究意义和实用价值。

2019-06-28 08:24:19

关于一种完整的USB芯片方案设计

2021-06-03 06:09:00

文中介绍了几款用于白家电各功能模块的高能效方案设计。

2021-05-10 06:06:25

分享一款不错的基于几种模拟信号的视频控制方案设计

2021-06-02 06:08:00

分享一款不错的智能门禁系统方案智能门禁系统方案设计原则是什么?

2021-06-15 09:11:52

分享一种不错的远程无钥匙系统方案设计

2021-05-12 06:16:16

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

会受一定的影响。?本文所提出的基于DSP+FPGA的控制系统方案,利用FPGA的容量大、可编程实现很多功能,结合DSP具有高速的信息处理能力的特点,使得本控制系统非常简洁,结构灵活,通用性强,系统也易于维护和扩展。该方案基于软件无线电的思想,是采用通用平台的设计。?

2019-07-29 06:08:47

是基于 PC 机,另外一种是基于 DSP 和FPGA。基于 PC 机的车牌识别系统功耗和体积大,基于 DSP 和 FPGA 的车牌识别方案设计复杂,成本高昂。应广大客户的需求,北京迅为推出 iTOP-3399 核心板,用于替代传统的 PC、DSP 和 FPGA 方案。

2020-12-29 07:45:46

113【电路方案】基于单片机射频RFID卡公司考勤系统方案设计【资源下载】下载地址如下:https://docs.qq.com/doc/DTlRSd01BZXNpRUxl功能描述:本设计由

2021-11-10 06:12:52

如何实现光伏发电光照自动跟踪系统总体方案设计?

2021-10-25 06:10:56

小白求助,求一个MTK MT7622 64位芯片方案设计

2021-10-27 06:21:18

怎么实现基于MRF24J40的IEEE802154无线收发器电路方案设计?

2021-05-25 07:00:15

你好我正在使用ZC706板传输调制信号。我们以文本和mat格式的形式提供这些调制信号。我想将这些调制信号加载到FPGA中,所以有没有办法直接将数据加载到FPGA中,当我们生成.bit文件时,这些数据

2019-05-06 07:25:49

技术实现的目标文件。本文将以 vxworks 操作系统作为通用处理器的基础软件环境,以 FPGA 目标文件、DSP 目标文件以及 GPP 目标文件组成的波形文件为目标,通过分析一般波形加载流程及其面临

2018-02-22 09:58:09

智能仪器仪表方案设计分享具体的规格书、型号参数、封装等如有询问,可以留言。我也可以提供给各位。

2016-06-03 11:31:31

电子方案设计类似seo教程必须优化设计?设计线路尽量优化,不要太冗余,造成工作效率不够。

2014-01-11 10:36:03

本人多年设计经验 主要从事 功率电力电子 fpga dsparm 单片机模拟电路步进电机永磁同步电机 无刷电机 多轴系统 等伺服电机控制 提供方案设计 偏向 各种电机控制(自己设计驱动器)自动

2016-02-20 14:16:10

本帖最后由 tangzhongming 于 2015-8-31 16:04 编辑

移动电源方案设计分享

2015-08-31 16:02:49

你好,我将使用一个NoBL SRAM(CY7C147BV33)在我的PCB设计中使用VixTy-5 FPGA。是否有NoBL SRAMs的参考方案设计推荐文件?最好的, 以上来自于百度翻译 以下

2019-07-04 09:47:52

介绍了氨纶工程DCS 系统方案设计的主要性能、基本原理和基本构成。提出了基于间歇式聚合生产工艺流程的DCS 系统方案设计原则和内容,并将其应用于生产实际中.

2009-04-07 11:49:27 13

13 机械系统运动方案设计, 拟定机械的工作原理,执行机构设计,原动机的选择,传动系统的设计,方案评价与选择,机构运动尺寸设计,机构性能分析,机构运动简图绘制一、拟定机械

2009-05-14 23:28:06 56

56 减压活门性能试验台系统方案设计:主要介绍了减压活门性能试验台的实现机理、采用的方案。关键词* 工控机; 位置传感器; 载荷传感器; 智能计数器; 液压伺服系统; +,

2009-06-06 17:53:05 23

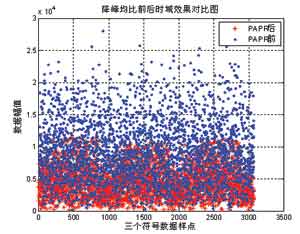

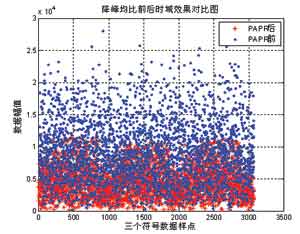

23 WiMAX 系统降低峰均功率比的方案设计作者:哈尔滨工程大学 张在兴 焦淑红摘要本文比较了各种降低峰均比方法的优缺点,最后针对WiMAX 系统自身的特点,提出了一种用预留

2010-02-06 17:10:19 0

0 WiMAX 系统降低峰均功率比的方案设计作者:哈尔滨工程大学 张在兴 焦淑红摘要本文比较了各种降低峰均比方法的优缺点,最后针对WiMAX 系统自身的特点,提出了一种用预留

2010-02-06 17:10:20 33

33 基于ARM+FPGA的可重构控制器设计及其在加载系统中的应用:文章提出了一种基于ARM+FPGA结构的可重构控制嚣的设计方法.并采用此方法开发了用于加载系统的2通道电液伺服控制器

2010-03-02 12:03:21 29

29 WiMAX系统降低峰均功率比的方案设计

引言宽带无线接入技术作为下一代通信网络中最具发展潜力的接入技术之一,正受到业界越来越多的关注。WiMAX(Worldwide Interoperability

2009-02-08 09:57:44 539

539

一种基于DSP+FPGA的控制系统方案设计

一、前言 ?

本文提到的控制系统控制通信设备的正常工作,是整个通信设备的重要组成部分。该控制系统要实现的功能

2009-12-22 17:44:41 870

870

基于载波检测的认知无线电方案设计.

2011-01-25 19:13:05 34

34 介绍了一种基于SRAM技术的FPGA可编程逻辑器件的编程方法,能在系统复位或上电时自动对器件编程。有效地解决了基于SRAM的FPGA器件掉电易失性问题,针对当前系统规模的日益增大,本文提出了一种用单片机对多片FPGA自动加载配置的解决方案.

2011-03-15 16:41:22 21

21 芯片的烧写与自加载是一个DSP系统能够顺利运行的基本条件。在DSP加载技术方面已经有大量文献和工作成果,比较好地解决了DSP自加载方面的许多基本问题。

2011-05-26 11:10:08 932

932

无线通信 FPGA方案设计:随着头部代码移动到新的位置,不会再和内核的目标地址冲突,可以开始内核自身的搬移了。此时r0寄存器存放的是内核长度(严格的说是长度外加128Byte的栈)

2011-06-21 17:51:54 40

40 雷达接收机灵敏度自动测试方案设计在GPTS软件上对 雷达接收机 灵敏度的自动测试进行方案设计,该方案包括测试平台设计、测试流程设计、测试速度与测试精度的设计。给出实验结果对

2011-07-24 11:48:01 89

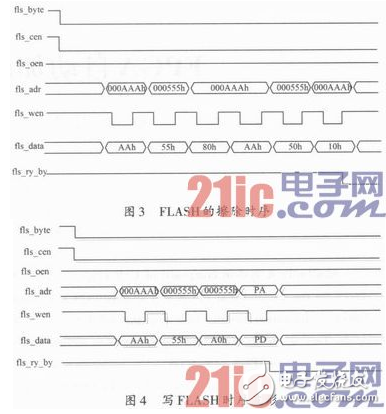

89 根据FPGA芯片加载时序分析,本文提出了采用通过市面上常见的Flash ROM芯片替代专用PROM的方式,通过DSP的外部高速总线进行FPGA加载;既节约了系统成本,也能达到FPGA上电迅速加载的目的

2011-08-16 16:26:14 1558

1558

本文旨在依据公理化设计理论进行生产系统的方案设计,利用先进的设计理念解决自动组装生产线系统这一难题。

2012-02-20 15:42:30 2815

2815

耳温枪设计方案设计耳温枪设计方案设计耳温枪设计方案设计

2015-11-13 15:58:16 0

0 智能插座方案设计CC2541蓝牙BLE方案

2015-12-18 14:20:13 65

65 电能计量远程抄表系统方案设计,供大家参考

2016-07-12 17:00:20 3

3 某转台伺服系统方案设计

2017-02-08 02:00:27 15

15 RF IC自动测试方案设计

2017-01-12 22:02:49 14

14 基于MCGS的货物分拣系统监控方案设计与实现_耿瑞芳

2017-03-18 09:11:39 5

5 芯片的烧写与自加载是一个DSP系统能够顺利运行的基本条件。在DSP加载技术方面已经有大量文献和工作成果,比较好地解决了DSP自加载方面的许多基本问题。而传统的烧写/加载方案在调试、更新程序时需要反复

2017-10-31 11:00:43 0

0 如今,随着FPGA工艺的进步,性能提升和成本缩减均得到极大的改善,这使得FPGA芯片的使用越来越广泛。因此为了达到降低系统维护和升级的成本,通常我们都会通过网络传送最新的下载文件,让用户在现场直接

2017-12-25 18:14:11 6339

6339

本文档内容介绍了基于xilinxFPGA选型详解,供参考查阅

2018-03-15 15:58:01 4

4 本文主要介绍了数电模电知识之短跑计时器系统方案设计.

2018-06-28 08:00:00 10

10 Atmel - SAM4L方案设计简介

2018-07-09 00:48:00 2001

2001 FPGA 的配置数据通常存放在系统中的存储器件中,上电后控制器读取存储器中的bit 文件并加载到FPGA 中,配置方式有JTAG、从并、从串、主从4 种,不同厂家叫法不同,但实现方式基本都是一样的。

2018-10-30 08:58:00 7921

7921

FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12:00 17251

17251 可编程的双重优点,被广泛应用于通信领域中。FPGA在上电后,需要加载配置文件对内部各功能模块进行初始化,而配置文件加载的效率直接影响系统的初始化时间。因此如何设计一种高效的FPGA加载方案,是通信系统设计中的一个重要环节。

2019-02-19 14:49:08 1900

1900

在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,从外部专用的 读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且 FPGA要加载的程序可以

2019-03-22 16:20:14 952

952 鼎盛合的脂肪秤方案设计及原理图。

2019-08-16 16:17:00 1464

1464 FPGA在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,FPGA从外部专用的 EPROM读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且

2020-08-13 17:16:46 1805

1805

智慧农村污水站点监控方案设计

2021-07-23 09:36:17 2

2 RFID手持终端智能巡检系统方案设计及应用

2021-08-31 15:47:09 28

28 DC电源转换方案设计(电源技术期刊查询)-该文档为DC电源转换方案设计总结文档,是一份不错的参考资料,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-22 12:35:26 5

5 高温DCDC电源-方案设计(电源技术论坛)-该文档为高温DCDC电源-方案设计总结文档,是一份不错的参考资料,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-22 12:49:48 53

53 FPGA-DCM使用详解(通信电源技术期刊编辑部电话)-该文档为FPGA-DCM使用详解文档,是一份还算不错的参考文档,感兴趣的可以下载看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 电子发烧友网站提供《安路EG4X FPGA从动串行加载模式.pdf》资料免费下载

2022-09-27 10:55:18 1

1 电子发烧友网站提供《安路EG4X FPGA从动并行加载模式.pdf》资料免费下载

2022-09-27 10:44:27 1

1 在不带内置ARM核的AMD FPGA产品系列中,FPGA的程序加载方式并没有发生大的变化

2023-07-07 14:14:58 981

981

电子发烧友网站提供《AP1682系统解决方案设计指南和应用说明.pdf》资料免费下载

2023-07-25 15:41:28 0

0 电子发烧友网站提供《基于GPS和TTS的自动报站器方案设计.pdf》资料免费下载

2023-10-08 10:21:26 0

0 电子发烧友网站提供《基于国密算法的CPU卡的门禁系统的解决方案设计.pdf》资料免费下载

2023-10-25 10:04:45 0

0 电子发烧友网站提供《基于ZigBee无线技术的城市路灯照明系统解决方案设计.doc》资料免费下载

2023-10-26 09:59:16 0

0 电子发烧友网站提供《一种基于线阵CCD扫描的车辆图像系统的方案设计.pdf》资料免费下载

2023-11-06 09:44:46 0

0 电子发烧友网站提供《基于DSP的车载语音识别系统方案设计.pdf》资料免费下载

2023-11-08 09:14:38 0

0 电子发烧友网站提供《压电驱动电源系统的方案设计.pdf》资料免费下载

2023-11-14 09:39:24 3

3

正在加载...

电子发烧友App

电子发烧友App

评论