以市场观点来看,许多人只会重视FPGA的大量型应用,例如用FPGA取代ASIC。

但就技术角度来看,FPGA的应用拓展就更为多样且具意义,这包括用FPGA加速高效运算、用FPGA加速电路设计验证、用FPGA取代大量性的DSP运算。

由于掩膜成本的指数性攀升,许多中等用量规模(约50万颗以下)的芯片无法如过去般以ASIC方式投产,且不得不改以FPGA投产,如此使近年来FPGA的市场不断增长。

FPGA侵蚀原有ASIC市场的用量极为可观的,此也成为近年来众人关注FPGA的首要焦点,不过也因为过于聚焦在高用量、大市场的观察,使FPGA的其它新应用发展被人所忽略,但这些应用却也极具意义。所以,以下本文将针对FPGA的新应用进行更多的了解与说明。

高效运算(High Performance Computing;HPC)

高效运算所指的即是军方、政府机关、学术研究单位所用的超级计算机(Supercomputer),另外部分企业内的工程、科技运算也含括在内,这类型的计算机拥有极高的运算效能,然近年来为了进一步提升系统效能,因此开始将FPGA运用于系统中。

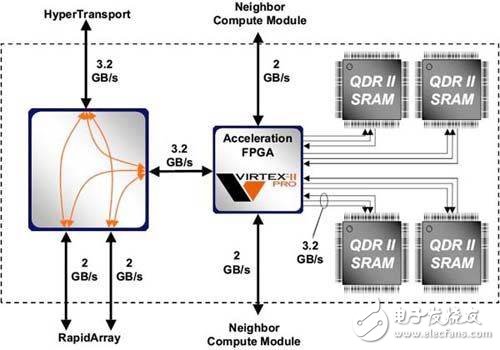

首先是Cray Research,该公司的超级计算机:XD1就有用上FPGA,XD1用的是Xilinx(赛灵思)公司的VIRTEX系列FPGA。XD1机内有所谓的FPGA应用程序加速模块(FPGA Application Acceleration Module),模块等于是机内的一个小型辅助运算系统,VIRTEX是模块内的主控芯片,等于是一个协同处理器(Co-Processor),只不过这个协同处理器与ASIC型式的协同处理器不同,FPGA具有可程序化的功效,因此VIRTEX是一颗可程序化的协同处理器。

运算模块内除了有FPGA的协同处理器外,处理器也必须搭配内存才能行使运算,所以FPGA会再连接4颗QDR II SRAM(极高速性的内存),然后模块一方面用HyperTransport与XD1的主处理器相连,另一方面也连往XD1的特有高速I/O界面:RapidArray。

接着,由于高效运算多是执行大量重复性的运算,例如气象预测、风洞测试等,所以可以将执行的应用程序转化成FPGA内的组态(Configuration,中国内地方面称为:配置)程序,以硬件线路方式来执行运算,如此将比过往用纯软件方式执行快上数倍至数十倍的效能,甚至在特定的应用运算上能达一百倍以上的效能。

更仔细而言,其实是将整个应用程序中重复性最高、且最经常呼用(Call,呼叫使用,中国内地方面称为:调用)的函式库(Library,中国内地方面称为:库)进行转化,改以FPGA的硬件线路执行,如此就能够以最小的转化心力获得最大的加速效果。

Cray如此,与Cray同为高效运算市场的另一家业者:SGI(视算科技)也实行相同的作法,SGI提出所谓的RASC(Reconfigurable Application Specific Computing;RASC),中文可称为:可组态化应用程序性运算,RASC也是以模块方式让原有的超级计算机能获得加速效果。

SGI的作法与Cray有部分相同也有部分不同,Cray是将模块设置在原有超级计算机的机内,而SGI则是运用既有超级计算机机箱的上部来加搭加速模块,不过就功效机制而言两者异曲同工,此外两者都使用Xilinx的VIRTEX系列FPGA,但是内存与I/O部分两家也实行不同的设计,Cray是使用QDR II SRAM,SGI则是可实行QDR SRAM,或者也可用DDR2 SDRAM,前者容量少(80MB)但速度快,后者容量大(20GB)而速度慢,提供两种选择的原因是可依据不同的应用程序特性来选用。

另外,高效运算业者通常有独门的机内通讯传输技术,RapidArray即是Cray的独家技术,而SGI自身也有独家的传输技术,即NUMAlink 4(已是第四代技术),所以SGI的RASC不是使用RapidArray,而是使用NUMAlink 4。

其实Cray系统内所用的FPGA模块是与DRC Computer公司技术合作而成,因此DRC Computer自身也有提供相近方案,DRC的RPU(Reconfigurable Processor Units)同样也是用FPGA来加速,一样是用Xilinx VIRTEX FPGA,但与主系统间的连接接口改成AMD Opteron处理器的接座接口,如此一般使用AMD Opteron处理器的x86服务器也可以加装RPU来提升高效运算的效能。

芯片开发时的逻辑功效验证

FPGA的另一个新应用是芯片开发时的逻辑功效验证。过去数字芯片在设计开发时,每开发至一个阶段就必须对已经完成的电路进行逻辑上、机制上的功效验证,以了解设计是否有误,关于此多是用计算机软件程序来进行逻辑推演(Simulation),不过用计算机程序来进行验证,其推演速度相当慢,所以每一项验证都要经过漫长等待才能知道结果。

对此或许有人会说:可以使用更快速的计算机来加快验证,但这其实是鸡与蛋的问题,计算机效能提升其实是因为芯片效能愈来愈高,芯片效能愈来愈高原因可用摩尔定律来解释,在摩尔定律下,芯片开发速度变快、同时也让芯片更复杂,所以「计算机的更快速」与「芯片的更复杂」是连动的,使用了更快速的计算机,也意味着要推演、验证更复杂设计的芯片,最根本的问题并还没有真正解决。

不过,由于FPGA的电路密度、运作效能在近年来大幅提升,所以开始有人提议用FPGA来取代纯计算机执行的验证软件,如此推演速度就可以获得大幅提升。举例来说,IBM、Sony、Toshiba三家业者所共同合作开发的Cell芯片,当芯片还在开发阶段时就已经使用FPGA来推演验证,以加速了解设计上的正确性。更具体来说,就是将新芯片的逻辑电路加载到FPGA,让FPGA充当新芯片来执行。

改采FPGA方式来验证,其优点不仅是加速验证程序,也可以节省验证成本,过去为了加速验证,必须动用大量的计算机,让众多的计算机同时都执行验证程序,才能让验证速度提升,有时其计算机的用量甚至要用及整个运算机房内的计算机,而今改成FPGA方式验证后,计算机用量就可大幅减少。

要注意的是,由于芯片的电路愈来愈复杂,即便使用高阶、大容量(逻辑闸)的FPGA,都很难单独用一颗FPGA就仿真出整个新芯片,所以通常是同时用上多颗FPGA芯片,每颗FPGA芯片仿真部份的新芯片电路,然后再将多个FPGA芯片进行串连,用多个芯片来同时仿真一颗新芯片。

另外,FPGA虽可以进行芯片设计的功效验证,但并不代表整个芯片的设计开发流程都可以加速,芯片电路设计的部份依旧需要工程师人工设计,只有功效验证上可以获得加速。再者,功效验证完全正确后并不代表芯片就此设计完成(除非该芯片确定直接以FPGA方式出货),后续在正式投产之前,还要经过频率收敛、电路化简等其它实体电路特性的调修,这方面FPGA也无从给予帮助。

数字信号处理器(DSP)

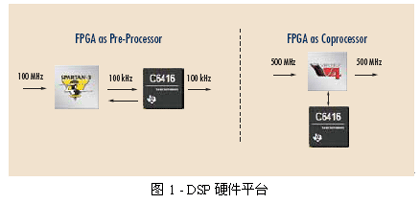

FPGA另一个新应用是取代DSP,由于FPGA适合规划成可同时大量平行运算组态,如此可加速数字信号运算。

所谓的「取代」,其实牵涉到价格效能比(Price Performance Rate,中国内地方面称为:性价比,性能价格比)问题,相同的数字信号运算工作可以用FPGA运算,也可以用DSP运算,重点在于芯片成本,一般而言FPGA的芯片价格贵过DSP,但FPGA同时间可平行执行的数字信号运算量比DSP大,当数字信号运算的需求量够大时,FPGA在价格效能比上就会超越DSP。

若更具体说明,一颗高效能的DSP约要30至200美元,而一颗高阶的FPGA则约200美元,高效能的DSP同时间可以处理4个信道的数字信号,而高阶的FPGA则可因应20至40个信道以上的信号运算,如此简单将信道数与价格相除,可明显看出在同时多组运算时FPGA的成本低于DSP。

当然,先决条件是应用需求上需要同时间的多组运算,并非所有的应用都需要大量的数字信号运算,不过无线基地台方面确实有此种需求,但无线基地台前端的用户装置则没有这类的需求,事实上现在确实有诸多的无线基地台,已从过去完全只用DSP方式来进行信号收发解析处理,改成部份使用DSP、部份使用FPGA。

但是这也并非绝对,原因有二,一是FPGA仍在积极降价中,未来的价格性能比会持续提升,目前只有大量的数字信号运算是属于FPGA较合算,但日后也会逐渐往中阶、初阶发展,接下来可能小规模性的基地台(如Pico Cell、Femto Cell等)也会使用。

另一是前端用户的数字信号运算量也在增加,特别是MIMO技术已经进入到末端用户产品上(如IEEE 802.11n标准),同时2个、3个天线的收发将使数字信号的运算量增加,加上愈来愈多无线技术是使用OFDM调变,而OFDM的调变为高度平行化的运算,使用FPGA将可获得不错的效益。

虽然许多人看好FPGA取代DSP的后续发展,但是FPGA也并非全然无威胁,目前许多芯片业者正积极发展多核心处理器,例如Tilera公司的Tile64处理器拥有64个执行核心,一样可以提供大量平行的运算,而不需要使用FPGA或DSP。

如冰山般「厚实、缓慢」的推进

上述三种FPGA的新应用,笔者个人认为往后只会更扩展、更深入地运用,而不可能回退,高效运算系统未来只会愈来愈常使用FPGA,芯片设计上的逻辑功效验证也会愈来愈常用使用FPGA,并减少使用推演软件(或称:仿真软件),基地台等应用也是如此。

所以FPGA是厚实地拥有了这三项新应用,未来用量与运用程度只会增加,但会慢慢地增加,因为FPGA的电路密度(或称:晶体管数量)只会愈来愈密、运作效能只会愈来愈快,同时价格也将愈来愈低。如同冰山一样:缓慢扩展,但每一英寸扩展却都相当地坚厚而难以回退。

△图说:Cray XD1超级计算机内的应用程序加速模块是用FPGA做协处理器,接着透过RapidArray接口连接至RapidArray的接口处理器(简称:RAP),RAP另一端再以HyperTransport(简称:HT)接口与超级计算机的主处理器连接。(www.Cray.com)

△图说:Cray XD1超级计算机应用程序加速模块部分的更仔细线路图,其中Xilinx VIRTEX FPGA与4颗QDR II SRAM相连,同时自身也能与其它相邻运算模块沟通传输,另外也与RAP相连。(www.Cray.com)

△图说:SGI的RASC应用程序加速模块,可直接加装在SGI超级计算机机箱的上端,并透过NUMAlink 4接口与超级计算机相连,以加速原有超级计算机的应用程序运算。

△图说:SGI RASC加速模块的内部图,中间部位的铜质散热片下方即是FPGA芯片,设置于周旁的则是内存模块,后端的黑色连接器即是NUMAlink 4接口,2组连接器表示RASC具有2组NUMAlink 4接口。

△图说:另一款SGI RASC:RASC RC100 Blade,图中可见大量的DDR2 SDRAM内存模块,容量最高可至20GB,适合在大数据量的高效运算。

△图说:Cell宽带引擎芯片还在电路的开发设计阶段时,是先运用数颗FPGA芯片组兜出Cell的仿真电路,然后推演、验证其功效逻辑及机制是否正确无误,图为Cell芯片的裸晶与一般文具图钉的体积比较。

△图说:无线收发基地台端有着同时多组数字信号的运算需求,此时就价格效能比而言使用FPGA将比使用多颗DSP合算,图中为WiMAX基地台端的模块化运算机箱(东讯TECOM公司的WM5070),机箱内负责无线传输的收发信号解析与演算,若WiMAX基地台使用方位性天线,则同时间内所需要运算的信号组数也会增加。

电子发烧友App

电子发烧友App

评论