1. CvP 简介 CvP(Configuration via Protocol)是一种通过协议实现 FPGA 配置的方案,Arria V,Cyclone V,Stratix V,Arria 10

2020-11-27 14:06:41 5111

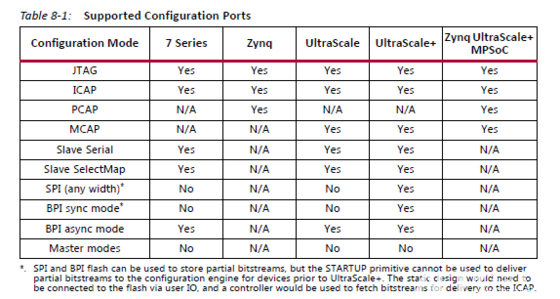

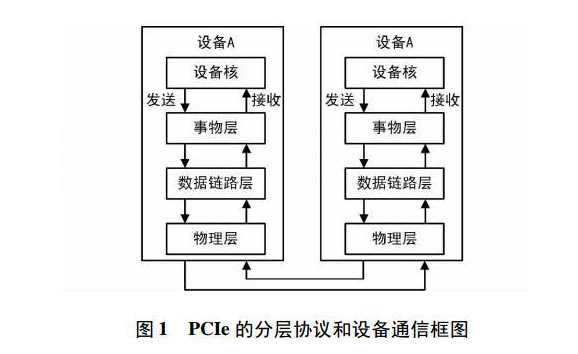

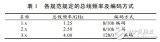

5111 芯片才能实现,具体哪些系列能实现哪种配置方式如下图所示: 图1 本质上来说,无论是JTAG还是ICAP或者MCAP以及其它FPGA的配置方式,目的都是配置FPGA的逻辑。MCAP是通过PCIE来实现

2021-01-03 09:20:00 3617

3617

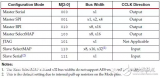

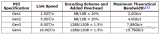

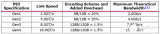

本文我们将向大家介绍PCIe引脚定义以及PCIe协议层。

2023-09-26 11:39:14 5665

5665

嗨,我正在尝试使用KC705板进行PCIE RC和端点测试。1)我将把PCIE RC控制器IP设计和FPGA PCIE PHY放在FPGA中。2)我将在FPGA中放置另一个PCIE端点控制器IP

2020-07-26 13:06:25

6678的pcie和fpga的pcie TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

2018-06-21 15:49:12

写在前面SPI协议系列文章:FPGA实现的SPI协议(一)----SPI驱动 在上篇文章,简要介绍了SPI协议,编写了SPI协议的FPGA驱动,但是在验证环节,仅仅验证了发送时序,而没有与从机进行

2022-02-17 06:03:44

1.单单用FPGA来实现路由、MAC层协议是有可能的吗?实现的主要困难在哪里?2.之前问过别人协议涉及大量变量,FPGA无法单独完成,需要ARM的配合,那么如果用FPGA+ARM框架来联合实现的复杂度大吗?3.可不可以直接用Power PC来实现?

2018-07-25 17:49:53

TCP/IP协议:TCP/IP协议是Internet上使用的主要协议之一,它定义了数据在网络中的传输方式和处理方式。FPGA可以通过实现TCP/IP协议栈来支持TCP/IP通信。PCIe协议:PCI

2023-03-27 09:01:46

我毕设需要做一个赛灵思的FPGA输入高速信号到PCIE口,但是速率过高不能直接接入,所以买了贵公司的CH368,但是不知道FPGA和CH368之间应该怎么实现通信,有没有verilog的例程可以参考,CH368是UART口还是普通串口呢?谢谢了!

2022-10-10 07:10:28

开发环境:windows开发平台:QT5.11.31.PCIE上位机测试过程FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:1.实现上位机的速度测试,经测试pcie的传输速度

2019-12-26 10:27:19

开发环境:windows开发平台:QT5.11.31、PCIE上位机测试过程FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:1.实现上位机的速度测试,经测试pcie的传输速度

2022-01-13 16:44:54

`PCIE总线的FPGA设计方法`

2015-10-30 14:30:52

本文档旨在提供关于将PCIe接口集成到基于AMBA的片上系统(SoC)的指导。

假设PCIe接口通过基于AXI或ACE协议的互连连接到SoC的其余部分。

读者应熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

基于PCI Express的数据采集卡PCIe数据采集卡PCI Express数据采集卡在北京工作6年以上,从事FPGA外围接口设计,非常熟悉PCI Express协议,设计调试了多个基于PCI

2015-01-10 20:36:09

大家好,我我想请问一下,在FPGA中怎样用verilog来编写通信协议的程序?它的步骤是怎样的?刚接触FPGA,好多不懂的,希望大神指点一二。。。

2014-12-06 21:19:02

功能,1、FPGA是不是可以直接通过PCIE操作DDR完成DMA操作?2、在操作过程中CPU是一个旁观者的角色吗?3、地址转换,DDR接口操作等都是由CPU内部的硬件完成?CPU在FPGA操作DDR的过程中,完全不受影响的工作吗?多谢!

2016-04-06 16:24:36

\drv\exampleProjects\PCIE_exampleProject 里面的例子

这个工程可以成功跑起来,并且在PC端通过用WinDriver可以看到设备,但是目前有一个关于例程中BAR配置

2018-06-19 00:50:13

前段时间发了个关于fpga的PID实现的帖子,有个人说“整个算法过程说直白点就是公式的硬件实现,用到了altera提供的IP核,整个的设计要注意的时钟的选取,流水线的应用”,本人水平有限,想请教一下其中时钟的选取和流水线的设计应该怎么去做,需要注意些什么,请大家指导一下。

2015-01-11 10:56:59

本人想问下,FPGA的介绍中有些事说带有PCIe硬核的,那么这个FPGA直接购买后就可以使用这个硬核完成PCIE功能了吗?不再需要购买其他什么许可文件之类的东西了吗? 这点不是很清楚,顺便问一下带有这中硬核的FPGA大概要多少钱呢?

2012-12-12 17:52:08

FPGA pcie dma测试

流程:金手指和电脑连接之后,先加载程序,pc重启;

现象:pc无法开机。

FPGA pcie x8,pc x16,直接连接上去的

请问这是什么情况呀,为什么电脑开不了机呢?

2023-09-13 18:21:28

编码后传到FPGA中,接着利用FPGA进行信道编码,再通过模拟调制,再发送。那么,我想问下通信协议在这里的作用是什么?或者说,如果我们想使用wifi协议,我们该如何应用wifi协议指导我们的设计?硬件

2015-01-27 18:15:35

关于这几个协议的实现,可以看下下面的文章,其中UART中详细介绍了RS232和UART区别。一天一个设计实例-3万字讲解UART和实例一天一个设计实例-IIC协议及FPGA实现一天一个设计实例-SPI

2022-08-19 16:32:22

查过mini pcie的信号引脚定义,有52个信号(大多引脚无用),X1 LANE 的情况,查看飞思卡尔或INTEL处理器的设计资料,关于这个应用除了主要 的差分收、发和差分时钟信号之外还需要额外

2017-11-29 11:50:51

FPGA(资源够用)都可以以soft IP形式实现FPGA吗?4.个人觉得使用Megwizard和Qsys中的IP就可以实现PCIE功能了,那么什么样的设计还需要加专用的协议芯片呢?谢谢!

2015-07-27 11:05:46

/en-us/design/trainingandevents/Documents/X-FEST%202012%20PRESENTATIONS/xfest12_pdf_pcie_v1_1_april29.pdf)如果FPGA中的ASIC退出,为什么我们需要Tandem方法?

2020-05-29 12:52:09

FPGA实现 PCIE 端点设备,我该如何实现这样一个功能,PC发送一条消息(比如一个存储器写事务),然后FPGA用户逻辑获得这个事务包里的内容进行相关操作,比如把一个LED点亮。已知在设计例程中

2016-03-12 10:48:22

pc端有一个文件,需要将文件中的数据通过pcie发送给fpga,有没有可供pc端调用的sdk

2017-02-09 11:10:14

项目名称:FPGA PCIe信号拆分应用领域:计算机参赛计划:利用FPGA的并行资源,实现在不使用plx硬核芯片的情况下对PCIe信号的拆分。具体有效带宽视开发板资源而定。使用FPGA相较于使用硬核

2021-05-12 18:05:46

技术,主要支持一致性缓存,内存和IO扩展。CXL是基于PCIe 5.0实现的连接技术,复用了很多PCIe协议的东西,这一点上与CCIX比较像,但又不完全一样。说起CCIX和CXL,难免要相互对比。其实

2022-09-09 15:03:06

串行总线协议PCIe、ASI和sRIO之间有什么不同?

2021-05-25 07:05:09

开发板测试:1、 安装windrive 2、LED状态显示 3、测试读写 PCIE开发板介绍:1、原理图介绍 PCIE TLP协议介绍:1、分析存储器写报文结构 2、分析存储器读报文结构 PCIE

2022-02-14 09:50:22

,那就很容易把pcie协议理解彻透彻,当然这里狭义指的是上层交互的TLP协议,数据链路层和物理层更复杂的事情是硬核做的,用起来PCIE并不需要深入了解。

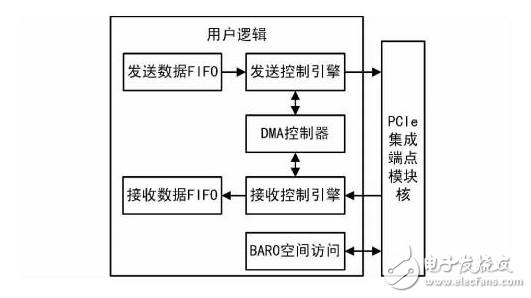

如何使用紫光PCIE,首先FPGA端需要一个

2023-11-17 14:35:30

你好,先生或女士我是中国学生。我已经研究FPGA一段时间了,我正在尝试使用FPGA来实现FC协议。经过一番研究,我发现GTH可以达到FC1。但是我发现使用7系列FPGA收发器向导IP存在一些问题。我

2020-08-17 10:28:07

嗨!我正在研究的沟通链如下:PC-PCIe- 光纤与sfp +-FPGA高数据吞吐量(10Gbps)是从FPGA到PC的。我应该使用什么协议?谢谢!以上来自于谷歌翻译以下为原文Hi

2019-02-26 09:50:19

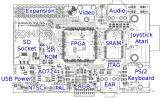

Atlas200I A2+PCIE X4接口测试FPGA 实物图片

全爱科技QA200A2 Altas200I A2开发套件做了验证。

图 1-2 QA200A2 Atlas200I A2 开发套件实物图

2023-09-05 14:39:57

1、在FPGA中实现串口协议的设计在FPGA中实现串口协议,通过Anlogic_FPGA开发板上的“UART2USB”口接收从计算机发来的数据。实验设计思路UART串口是一种类似于USB、VGA

2022-07-19 11:09:48

作者:王毅 管会生 刘斌彬 梅顺良引言本文采用FPGA实现了IDE硬盘接口协议。系统提供两套符合ATA-6规范的IDE接口,一个与普通IDE硬盘连接,另一个与计算机主板上的IDE接口相连。系统采用

2019-04-18 07:00:10

,基于ARINC664规范第7部分,提出符合该规范的基于FPGA的AFDX端系统协议芯片和相应AFDX端系统板卡的设计方案,并给出关键模块的具体实现;通过对端系统协议芯片进行测试验证,证明该端系统协议芯片

2010-05-13 09:09:08

基于MIPI协议的FPGA实现视频传输技术

2019-08-13 10:01:23

本项目标识码 : 04X1V5000082请记下 项目标识码 与客服人员,我们将尽快安排工程师与您沟通基于Xilinx Virtex-5LXT FPGA的四路光纤PCIE卡(4路光纤卡)1、板卡

2012-06-18 11:40:51

PCIe是什么?有什么核心优势?Xilinx的PCIe端点模块的显著优势包括哪些?基于Virtex-5 LXT FPGA的PCIe端点该怎样去设计?

2021-05-26 06:39:11

PCIe总线通信过程是怎样的?是什么原理?如何利用PCIe DMA总线实现一个基于FPGA的PCIe 8位数据采集卡?

2021-09-17 07:16:03

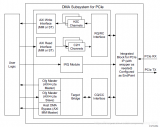

嗨,我正在使用超大规模的FPGA板。我可以通过DMA子系统IP和DDR控制器IP将数据从PC传输到DDR。我打算在FPGA中进行一些处理,然后更新数据,以便PC可以读取。如何通过PCIe指示PC处理

2020-05-08 09:40:04

IDE接口协议简介用FPGA实现接口协议的方法介绍

2021-04-08 06:39:49

需求:两块fpga互联,两块fpga分别模拟成特定的pcie设备,两个设备通过serdes总线互联通信,fpga仅仅只要模拟特定的设备就可以,不需要负载的逻辑,提供简单的读写,dma,中断等功能。高价寻高手,请各位多帮忙啊。

2019-02-11 15:31:02

只有一个)。在我的设计中,我已经将FMC HPC连接器用于其他目的,我想知道我是否可以将PCIe中的MGT用于RapidIO协议,或者这个接口仅用于PCIe?提前致谢。

2019-08-29 10:33:02

一块带有PCIE接口的FPGA,一块PCIE转USB3.0板卡,想通过FPGA控制PCIE转USB3.0板卡,实现USB3.0读入数据,经过FPGA高速处理,不需要经过电脑CPU。请问各位专家:1.

2014-12-25 22:54:58

本人现在在做一个PCIE接口的数据采集系统,下位机是FPGA,上位机是PC,调用的Xilinx的PCIE核,DMA传输。现在需要在数据缓存到一定程度时(这个时候是知道的)由FPGA产生一个中断信号通知上位机接收数据。但是不知该如何产生使用这个中断信号,求大神帮忙解答一下,谢谢!

2016-07-19 20:04:36

/pcie-ti81xx中的代码,使用了函数platform_get_resource_byname(),这个函数是否和我想实现的功能有关?我在PCIe.c中加

2018-05-28 01:52:49

嗨,我将从一个新项目开始。它涉及使用FPGA和GP / GPU加速PCIe板,这些板将被添加到常规计算机或服务器中。 GPU将是NVIDIA特斯拉。 FPGA板......还有待选择。我确实看到了

2019-01-24 10:55:48

bit)是关于PCIe的5个问题,这些只要按要求去做就行了。但我们在网上看到有人讲:多片C6678通过PCIe互联通信时,发现C6678在多个方面与PCIe协议不一致!是真的吗?如果是这样,不但C6678

2018-08-03 08:16:10

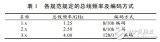

传输速率是根据PCIE的协议制定的吗?2.如果我设置的速率超过5.0Gbps可以吗?是否会出现数据的传输错误等现象?3.不太理解PCIE中关于x1和x2的含义,文档说PCIE是one single interface link,那么对于单个端口而言,x2的含义仅仅是代表速率是x1速率的一倍吗?

2018-06-19 04:36:26

亲关于如何使用GTX生成PIPE接口PCIE PHY的以下主题,有没有人有答案?https://forums.xilinx.com/t5/7-Series-FPGA

2020-05-04 09:05:44

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 编辑

你好!我目前正在实现6657DSP 评估板与xilinx kintex7 FPGA之间的PCIE连接,其中DSP作为Root

2018-06-25 05:14:40

请问,那里能找到关于在FPGA中实现DDC中分数倍重采样的资料?不是指用CIC实现,而是基于多相的结构实现。

2020-07-30 16:50:07

系列FPGA实现PCIe接口所涉及的硬件板卡参数、应用层系统方案、DMA仲裁、PCIe硬核配置与读写时序等内容。

2019-05-21 09:12:26

PCI总线协议的FPGA实现及驱动设计

摘要! 采用FPGA技术! 在公司的flex6000系列芯片上实现了从设备模式pci总线的简化协议!并给出了WIndowsx 系统下的虚拟设备驱动程序

2010-03-12 14:30:27 36

36 将PCIE与PCI、K1.X等总线技术进行比较,分析它的技术特性和优势,剖析数据包在各层中的流动过程。/并且详细阐述基于FPGA的两种盯行性实现方案,即采用第三方PHY接口器件和低成本

2011-08-31 17:42:49 154

154 Altera公司(Nasdaq: ALTR)宣布,成功实现28-nm Stratix® V GX FPGA与PLX®技术公司(Nasdaq: PLXT) ExpressLane™ PCI Express® (PCIe®) Gen3的互操作

2011-12-14 09:28:09 677

677 介绍了HDLC协议RS485总线控制器的FPGA实现

2012-02-14 14:59:36 100

100 白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 基于PCIe2_0协议的PCS层弹性缓冲器设计_武桂林

2017-01-07 20:49:27 5

5 PCI Express(PCIe)是一种高性能互连协议,可应用于网络适配、图形加速、服务器、大数据传输、嵌入式系统等领域。PCIe协议在软件层上可兼容于PCI和PCIX,但同时也有明显的不同。在两个

2017-10-13 10:41:03 24

24 目前,PCI Express总线的实现方式主要有两种:基于专用接口芯片ASIC和基于IP核的可编程逻辑器件FPGA方案。前者通常采用ASIC+FPGA/DSP的组合方式,专用PCIE接口芯片

2018-07-25 11:01:00 1376

1376 根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspci可能无法检测到基于FPGA

2018-06-19 10:24:00 7625

7625

目前通过 FPGA 实现 PCIe 接口是一种比较常用的方式,具有硬件成本低、可靠性高、灵活性大、易于升级等优势。两大 FPGA 厂商 Xilinx 和 Altera均具有完善的接口 IP 和测试方法。

2019-03-24 09:21:15 2833

2833

PCIe协议分析仪作为PCIe总线分析的基本工具,不仅仅用于主机,网络,存储系统等各种IT和通讯设备针对PCIe插卡的问题分析,同时也是PCIe/NVMe SSD分析的必备工具。 作为PCIe协议

2020-09-21 14:26:48 9855

9855 为了实现军航管制系统中雷达数据的可靠传输,根据HDLC协议的帧结构和循环冗余校验(CRC)原理,提出了一种新型的基于并行机制的HDLC协议控制器,讨论采用FPGA新技术实现HDLC协议帧的构成

2020-11-04 18:04:10 15

15 基于FPGA的TCP/IP协议的实现说明。

2021-04-28 11:19:47 49

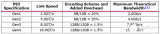

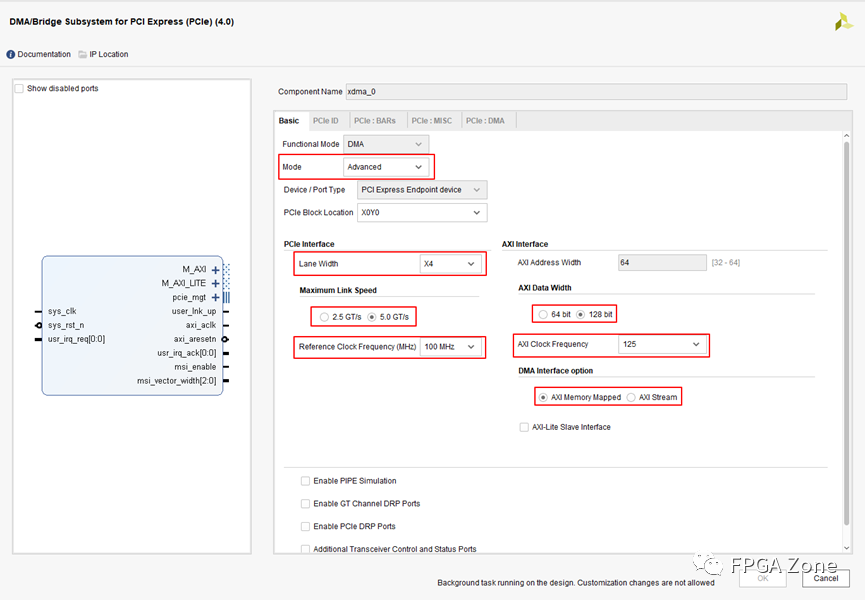

49 基于VIVADO的PCIE IP的使用 项目简述 上一篇内容我们已经对PCIE协议进行了粗略的讲解。那么不明白具体的PCIE协议,我们就不能在FPGA中使用PCIE来进行高速数据传输了吗?答案是否

2021-08-09 16:22:10 10199

10199

基于FPGA的SPI协议及设计实现博主微信:flm13724054952,不懂的有疑惑的也可以加微信咨询,欢迎大家前来投稿,谢谢!引言介绍在电子通信领域里采用的通信协议有IIC,SPI,UART

2021-11-05 19:05:59 22

22 CXL是基于PCIe 5.0实现的连接技术,复用了很多PCIe协议的东西,这一点上与CCIX比较像,但又不完全一样。说起CCIX和CXL,难免要相互对比。

2022-09-06 10:05:57 5257

5257 PCIE协议5.0完整版

2022-09-13 14:32:47 0

0 FPGA实现SPI协议

2023-03-20 10:35:02 0

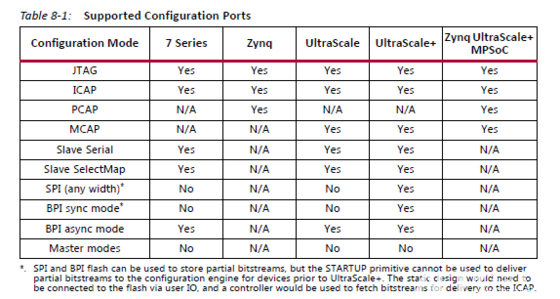

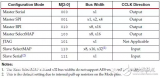

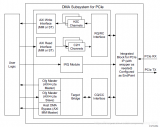

0 AMD FPGA自带PCIE硬核,实现了PCIE协议,把串行数据转换为并行的用户数据,以UltraScale系列FPGA为例,其支持Gen1.02.03.04.0,1~16 Lanes,如下图所示。

2023-06-09 09:34:26 852

852

AMD FPGA自带PCIE硬核,实现了PCIE协议,把串行数据转换为并行的用户数据

2023-07-14 15:53:40 878

878

本文介绍一个FPGA 开源项目:PCIE I/O控制卡。上一篇文章《FPGA优质开源项目– PCIE通信》开源了基于FPGA的PCIE通信Vivado工程,用于实现上位机通过PCIE接口访问FPGA的DDR3以及RAM内存数据。PCIE I/O控制卡工程是在上一个工程的基础上进行了部分模块和参数的修改。

2023-09-01 16:18:36 1296

1296

本文介绍一个FPGA开源项目:PCIE通信。该工程围绕Vivado软件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的开源驱动程序,可在Windows系统或者Linux系统下使用,因此采用XDMA IP进行PCIE通信是比较简单直接的。

2023-09-04 16:45:54 1142

1142

Hello,大家好,之前给大家分享了大约一百多个关于FPGA的开源项目,涉及PCIe、网络、RISC-V、视频编码等等,这次给大家带来的是不枯燥的娱乐项目,主要偏向老的游戏内核使用FPGA进行硬解,涉及的内核数不胜数,主要目标是高的可实现性及复现性。

2024-01-10 10:54:24 363

363

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,实现PCIe PHY Layer,Data Link Layer以及

2024-02-21 15:15:03 144

144

电子发烧友App

电子发烧友App

评论