用循环语句设计一个7人投票表决器,速求

2013-04-23 18:01:49

仅供参考,有哪里不对的话还望各位网友多多指教,大家共同探讨。

2019-06-21 15:24:02

8人表决器电路,,源文件

2015-04-12 09:43:57

的,它们需要用编程器烧写。目前的PLD都可以用ISP在线编程,也可用编程器编程。这种PLD可以加密,并且很难解密,所以常常用于单板加密。1.将PLD焊在PCB板上2.接好编程电缆3.现场烧写PLD芯片

2012-02-27 10:42:53

; 3.还有一种反熔丝(Anti-fuse)技术的FPGA,如Actel,Quicklogic的部分产品就采用这种工艺。但这种的PLD是不能重复擦写,需要使用专用编程器,所以开发过程比较麻烦,费用也比较

2009-06-20 10:38:05

PLD现在已经从采用最先进的标准单元技术制造的固定逻辑器件手中夺得部分市场份额。而消费电子则是PLD正在快速增长的应用领域。 PLD行业最近出现了很多新变化。以往,PLD更多是用在一些特殊产品中,例如低成本原型,或者像路由器这样的小批量产品。而今天,PLD则更多涉足消费电子领域。

2019-07-29 08:07:20

采用最先进的标准单元技术制造的固定逻辑器件手中夺得部分市场份额。而消费电子则是PLD正在快速增长的应用领域。 PLD行业最近出现了很多新变化。以往,PLD更多是用在一些特殊产品中,例如低成本原型,或者像路由器这样的小批量产品。而今天,PLD则更多涉足消费电子领域。

2019-07-17 07:19:16

采用最先进的标准单元技术制造的固定逻辑器件手中夺得部分市场份额。而消费电子则是PLD正在快速增长的应用领域。 PLD行业最近出现了很多新变化。以往,PLD更多是用在一些特殊产品中,例如低成本原型,或者像路由器这样的小批量产品。而今天,PLD则更多涉足消费电子领域。

2019-07-22 06:51:56

,通过三态门控制数据直接输出或反馈到输入端。PLD有多种结构形式和制造工艺,不同厂商生产的可编程逻辑器件又有不同的型号和名称,下面简单介绍低密度和高密度可编程逻辑器件的基本结构和特点。(1)PROM。即可编程只读存储器

2019-03-06 10:19:07

的延时;3、具有信号寄存和按时序产生和处理信号的能力。特别是在单片机系统中,由于单片机的输出信号线很有限,在需要同时控制显示器、键盘、扩展存储器、I2C闪存、多路传感器等众多外部设备时,就更显

2012-11-19 20:41:23

警报;(2) 系统复位后进入抢答状态,当有一路抢答按键按下,该路抢答信号将其余各路抢答信号封锁,同时铃声想起,直至该路按键松开,显示牌显示该路抢答台号;(3) 用VHDL语言设计符合上述功能要求的四人

2012-07-17 10:19:21

三人表决器的VHDL设计实现求代码

2018-11-10 13:50:50

设计一个七人表决电路:表决结果用不同颜色的LED表示;表决输入采用自恢复按键,即点动后能够自动复位的那种,尽量采用与或非门完成设计,结果必须最简;

2009-05-17 10:10:23

求labview速成方法《《《《急急急

2012-09-11 21:54:12

)、USB 2.0、DVI、HDMI和各种各样的无线标准。本文将介绍如何应用可编程逻辑器件(PLD)将不同的高速视频内容连接到视频播放器。 视频输入 USB 2.0是目前连接电脑和娱乐信息设备的主流

2019-05-14 07:00:12

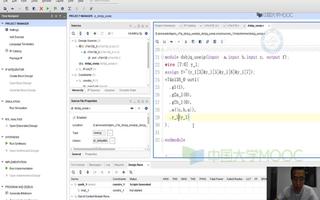

:数字电路是FPGA的敲门砖、因为数字电路主要的内容就是组合和时序,而组合和时序就是FPGA设计的核心。HELLO FPGA项目实战篇:该篇列举三人表决器、数字时钟、多功能点歌系统、数字示波器这四个实际的工程项目,手把手带领大家分析工程、分解工程、到最终实现工程。

2020-05-11 14:31:53

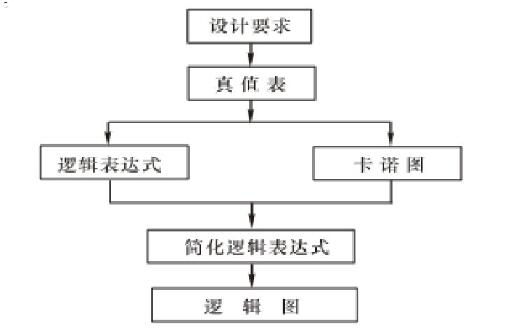

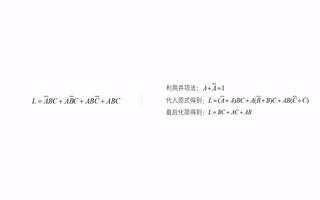

时序电路)。 在组合逻辑电路中,任何时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。在上一节中,设计的三人表决器就是组合逻辑电路,输出与输入一一对应,和其他

2023-02-21 15:35:38

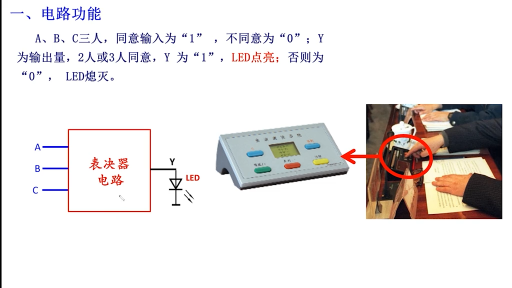

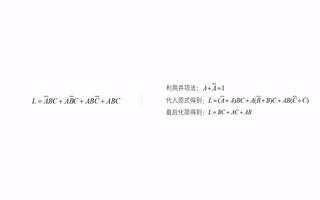

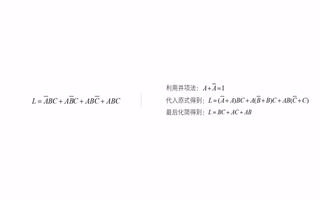

的取值确定之后,输出的取值便随之而定。因此,输出与输入之间是一种函数关系。这种函数关系称为逻辑函数。 下面利用一个三人表决器的电路设计来说明一些问题。此电路有三个输入(A、B、C),一个输出(Y),只有

2023-02-20 17:24:56

现在用51单片机和nrf905做一个表决器。关于nrf905有一些问题,想让大家帮帮忙!!!nrf905上的spi接口只需要设置RF配置寄存器,是吗?如果是如何确定那个是主哪个是从, 难道主从是看程序中所写的发送和接收程序吗?

2012-09-15 17:16:47

`项目实战篇以例举三人表决器、数字时钟、多终端点歌系统、数字示波器这四个实际的工程项目,手把手带领大家从分析工程、分解工程到最终实现工程。`

2021-04-06 14:20:59

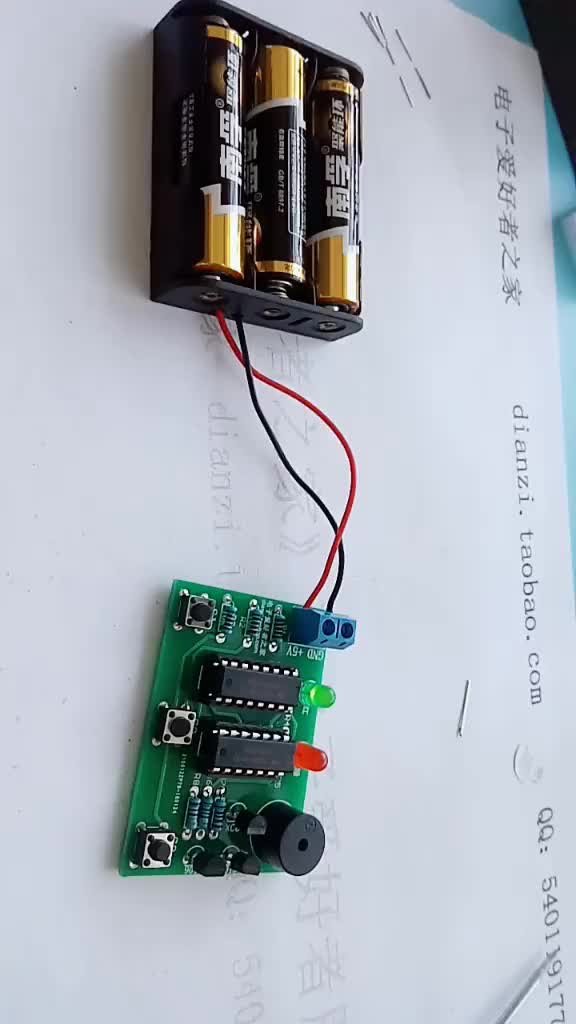

有了对LED、KEY、数码管的了解后,接下来就是对这三者一个综合应用了,那就是经典的三人表决器。结合开发板,三个按键按下,则其对应的LED将会点亮,数码管同时显示总的投票数 无需废话。看程序

2016-09-21 22:02:31

)两类功能,瞬时逻辑主要是指与、或、非及其混合运算,输出结果对输入条件能即时响应;延时逻辑一般由时钟信号驱动,主要实现寄存器、计数器以及与十序有关的逻辑功能。 最简单的PLD器件一般有8个专用输入端和8

2012-10-30 23:39:54

(二) 由逻辑命题编程如果用拨动开关左1、左2、左3代表逻辑输入A、B、C,发光管左1、左2、左3位指示其状态,用数码管1和0指示输出状态试编程序实现下述逻辑关系:M10.模拟少数服从多数表决器(三

2013-07-14 16:01:39

的消费类视频接口包括ieee 1394(火线)、u*** 2.0、dvi、hdmi和各种各样的无线标准。本文将介绍如何应用可编程逻辑器件(pld)将不同的高速视频内容连接到视频播放器。

视频输入

u

2018-12-28 07:00:06

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。

2019-10-18 08:20:51

请问如何使用PLD去设计三相正弦波电压发生器?

2021-04-29 07:01:08

采用最先进的标准单元技术制造的固定逻辑器件手中夺得部分市场份额。而消费电子则是PLD正在快速增长的应用领域。

2019-09-24 06:58:39

如何在ALTERA公司的Quartus II环境下用VHDL、Verilog HDL实现设计输入,采用同步时钟,成功编译、综合、适配和仿真,并下载到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

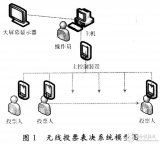

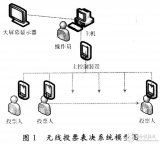

以微型处理器为核心,外围配以存储器,键盘及led显示器,设计出一种实用的无线电子表决器

2019-03-13 15:02:16

怎么在PLD开发中提高VHDL的综合质量?利用Quartus II软件的开发流程有哪些步骤?

2021-05-08 09:23:07

现在我在做一个无线表决器,其他都成功了,但是就是在报到时无法排除没有按下报到键和没有上电的表决器,我个人认为是表决器返回值时出错了,但我有找不到问题,希望各位帮帮忙,谢了!!! 下面是我集中器发送

2013-03-14 16:53:57

怎么画线路图和原理图

2018-06-19 12:07:25

我的VHDL测试文件中要求有三相输入,分别是Uab(t)=128sin(327t+120°),Ubc(t)=128sin327t,Uca(t)=128sin(327t+240°)。求教如何转成把这三个式子编写成VHDL语言输入

2016-05-17 14:14:32

本帖最后由 eehome 于 2013-1-5 09:58 编辑

用AT89C51实现三人表决器

2012-08-14 19:39:24

用BD—Ⅳ型,拼一个三人表决器电路接通开关,A、B、C三点:双向灯绿灯红灯三点都悬空(不表决)蓝灭灭无论哪二点接正,另一点接正、接负、悬空灭亮灭无论哪二点接负,另一点接正、接负、悬空灭灭亮不使

2019-09-29 20:57:34

这两个警告怎么解决,一下是源程序,我做的是三人表决,程序通过,但是仿真的波形不对啊Warning: No exact pin location assignment(s) for 4 pins

2016-09-28 18:07:55

PLD设计技巧—采用同步电路设计AsynchronousvsSynchronous Circuit Design

Mainly useCombinationalLogic to do

2008-09-11 09:12:46 24

24 PC机与单片机通信实例:表决器单片机要同时处理很多部分的功能,如:按键处理、LED处理、通信处理等。而单片机程序是串行执行的。如何让众多任务同时进行或者看起来同时

2009-06-28 00:02:05 70

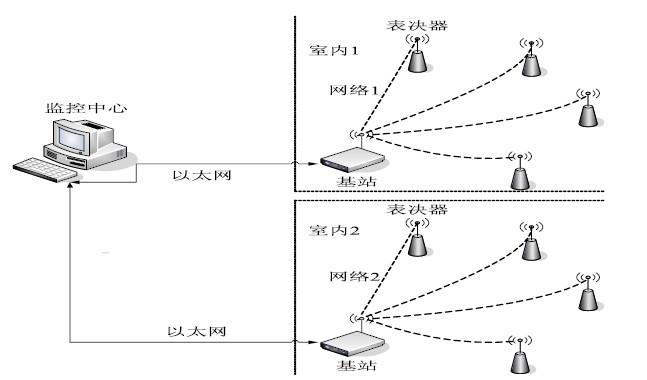

70 介绍了一种基于MSP430F123 和nRF905 的无线表决系统的软硬件设计与实现。系统通过主控器、表决器和PC 机实现对表决信息的采集、处理和显示。本系统具有低功耗、功能强、可靠性

2009-08-11 08:22:51 51

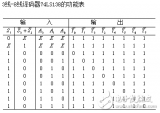

51 采用Lattice公司的PLD器件ISPLSI1032,基于VHDL描述语言设计了一种MCS一5I单片机与PLD可编程逻辑器件的接口电路,该接口电路具有体积小、性能可靠、开发便捷、所需外围元件少等优

2009-11-17 16:13:01 30

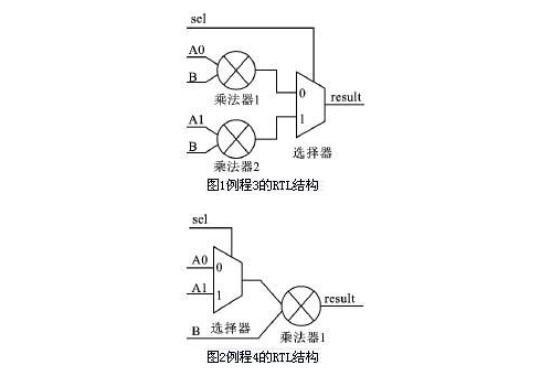

30 采用CPLD/FPGA的VHDL语言电路优化原理设计

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起

2010-03-19 11:38:02 2318

2318

文章在MAX+PLUS II 开发环境下采用VHDL 语言设计并实现了电表抄表器讨论了系统的四个组成模块的设计和VHDL 的实现每个模块采用RTL 级描述整体的生成采用图形输入法通过波形仿真下载芯

2011-09-23 17:56:11 40

40 本文详细讨论了VHDL语句对PLD设计的影响和设计经验,经典文章,值得仔细阅读消化。, PLD Programming Using VHDL

2012-01-17 11:20:54 0

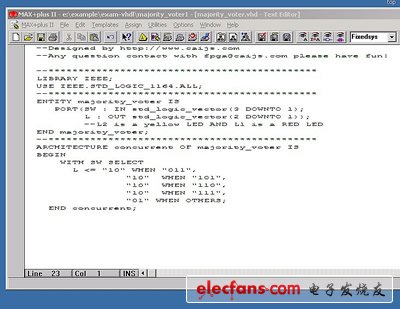

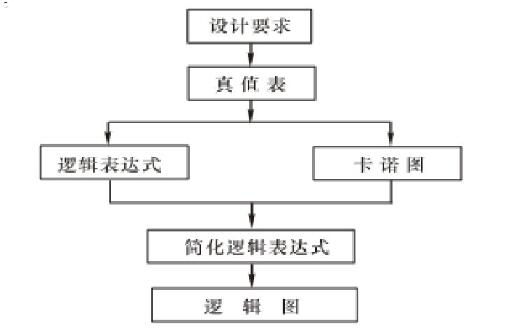

0 我们根据三人表决器的直值表,可以通过 卡诺图 化简可以得到: L2=SW1SW2 SW1SW3 SW2SW3 L1=_L2 那么我们可以在MAX plusII中用原理图实现上面的三人表决器 下面仅把和 VHDL 不同的详细写下,相

2012-05-18 15:46:43 8330

8330

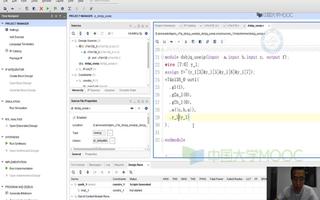

--三人表决器(三种不同的描述方式) vhdl -- Three-input Majority Voter -- The entity declaration is followed

2012-05-18 16:04:22 20986

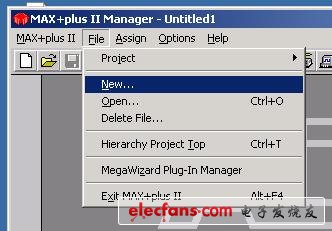

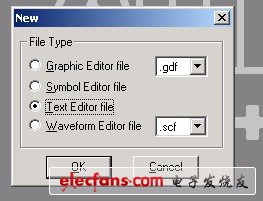

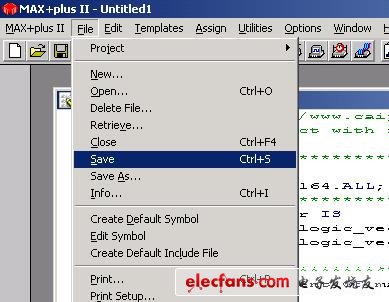

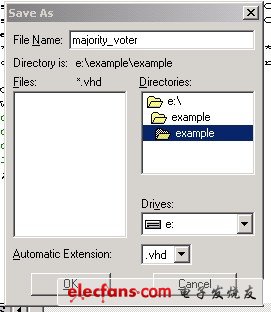

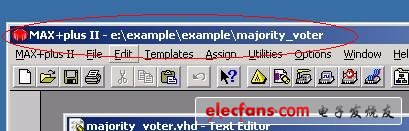

20986 今天我们将带领大家完成你的第一个PLD设计,即使你从没有接触过PLD,也可以让你可以在十分种之内初步学会PLD设计! 不信? 呵呵 我们慢慢往下看。 实验目的 我们分别采用VHDL、Verilog

2012-05-18 16:29:52 1124

1124 下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过: (1)打开MAX plusII (2)新建 新建一个verilog-HDL文件(Text Editor File类型) (3)输入设计文件 其中SW12,SW13,SW23为中间变量 module m

2012-05-18 16:37:14 13434

13434

用 VHDL /VerilogHD语言开发PLD/ FPGA 的完整流程为: 1.文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。通常VHDL文件保存为.vhd文件,Verilog文件保存为.v文件 2.功能仿真

2012-05-21 12:58:06 1083

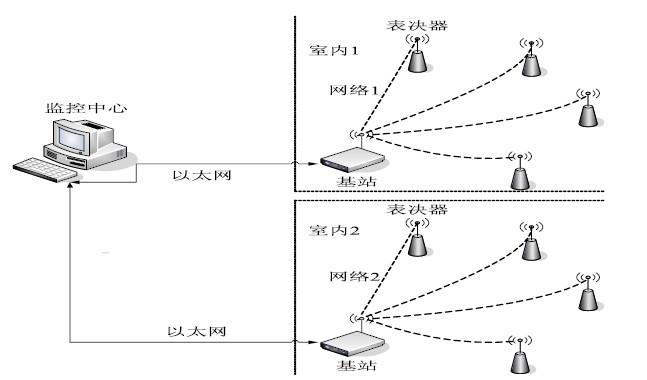

1083 1 引言 投票表决器在选举,会议,教学,娱乐节目中得到大量的使用。现行的无线表决系统采用单一的无线网络,使无线终端设备与上位机进行通信。由于无线网络存在传输距离有限,

2012-07-24 16:45:27 1671

1671

基于PLD和AHDL的交通灯控制器设计. 基于VHDL设计交通灯控制器,外围电路少、功耗低、可靠性高,便于系统功能的修改,设计效率高。

2016-01-08 16:21:00 27

27 掌握在 Quartus Ⅱ开发环境下,运用硬件描述语言输入法对“三人表决器”进行设计输入、编译、调试和仿真的方法。

2016-01-15 15:27:33 0

0 本文通过举例 利用VHDL 语言描述了不同模式的有限状态机 分析了有限状态机在 PLD 中综合的特点 。

2016-03-22 15:41:36 3

3 HL配套C实验例程100例之表决器,配合开发板学习效果更好。

2016-04-11 16:09:41 14

14 以前寫論文收集的一些資料,學習單片機、C語言的好資料!!!!

2016-07-08 13:58:47 4

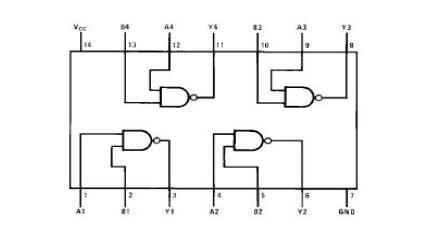

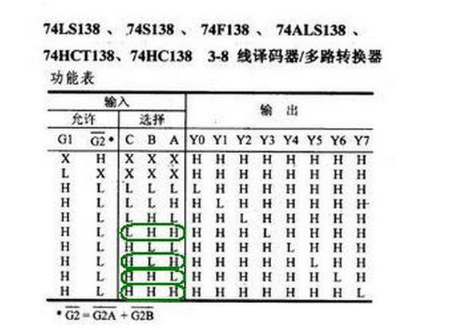

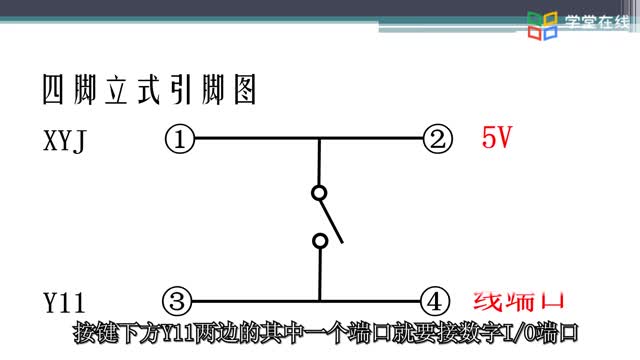

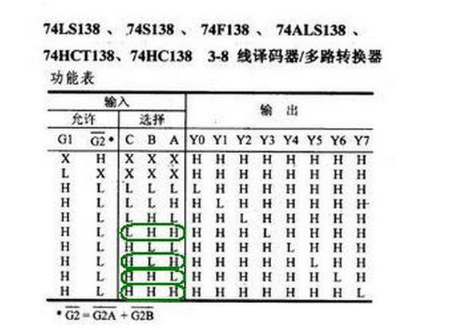

4 三人表决器主要由一个3-8位译码器(74LS138)和2个4输入与非门(74LS20)组成。通过三个按钮接受用户输入。按钮按下表示同意,不按下表是否决,当没有人按下按钮时,或只有一个人按下按钮

2017-10-31 15:13:25 92965

92965

本文为大家带来五种三人表决器电路设计方案,包括两款仿真电路及程序分析,三款逻辑电路设计的原理详解。

2018-01-17 18:49:21 298033

298033

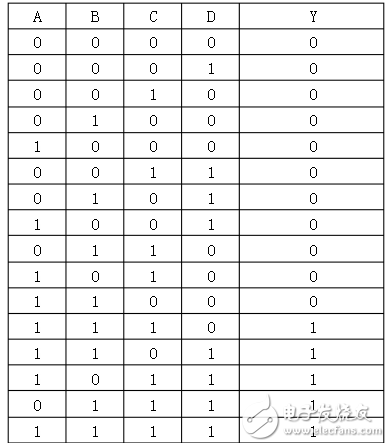

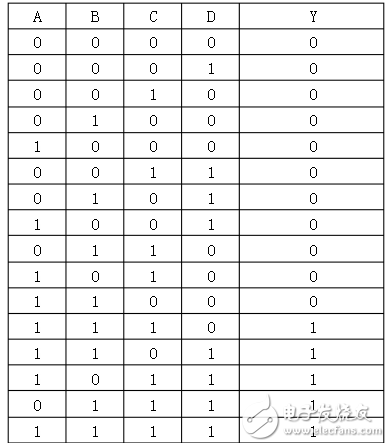

本文为大家分享四款四人表决器电路设计的原理及方案详细。

2018-01-17 19:13:09 142800

142800

本文为大家带来五款五人表决器电路设计方案。

2018-01-18 09:18:07 98683

98683

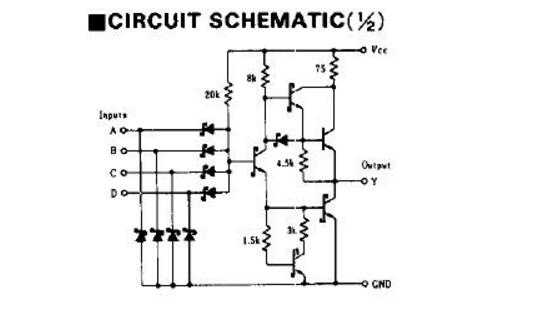

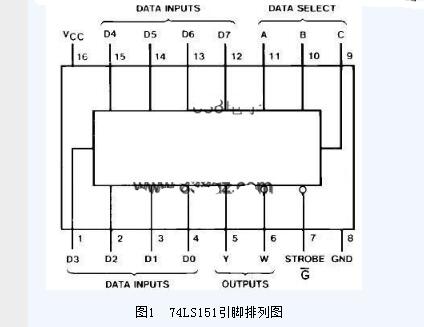

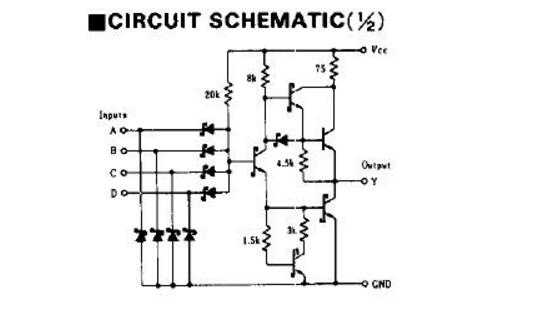

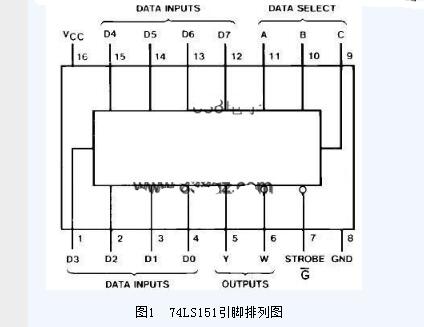

本文介绍了4种方式实现三人表决电路。其中包括用74LS00,74LS20实现三人表决电路、用译码器138和与非门74LS20设计实现三人表决电路、用8选1数据选择器74LS151实现三人表决电路以及用4选1数据选择器74LS153实现三人表决电路方法。

2018-01-26 17:26:20 335165

335165

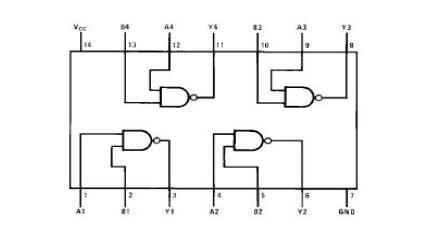

本文开始介绍了74LS00管脚排列图与74ls00的功能表,其次介绍了74ls00应用电路与74ls00的极限值,最后介绍了74ls00制作三人表决器逻辑电路的设计步骤与调试。

2018-02-08 15:42:56 243528

243528

本文开始介绍了74LS20功能表与74LS20引脚图,其次介绍了74LS20真值表,最后详细介绍了74ls20实现的四人表决器电路并对工作原理、电路仿真及调试进行了相应的介绍。

2018-02-08 16:18:08 90713

90713

74ls151是常用的8选1数据选择器。本文主要介绍了74ls151引脚图、74ls151逻辑图及74ls151真值表,详细的阐述了74ls151实现三人表决器电路。

2018-02-08 16:59:36 177218

177218

本文主要介绍了五款74ls138的应用电路图。其中包括了74ls138全加器电路、74ls138抢答器电路、74ls138实现逻辑函数、74ls138全减器电路以及与74LS20组合的三人表决器电路。

2018-05-04 10:31:55 95858

95858

”,绿灯不亮;当表决器的五个输入变量中有3个以上(含3个)为“1”时,则表决器输出为“1”,此时绿灯就亮了。

2018-05-07 11:38:47 108521

108521

在三人表决器的设计中,如果数字系统简单,可以采用门电路;如果数字系统复杂,则可以采用译码器、数据选择器和加法器比较好。

2018-08-07 09:31:14 161411

161411

投票表决器在选举,会议,教学,娱乐节目中得到大量的使用。现行的无线表决系统采用单一的无线网络,使无线终端设备与上位机进行通信。由于无线网络存在传输距离有限,对障碍物穿透性较差等问题,无法实现远程监控

2018-12-26 09:10:00 4425

4425

该设计实现了基于MSP430F135和CCllOO的无线表决系统的主控制装置和表决器的软硬件,并利用Microsoft Visual Studio 2005实现了系统PC机软件的设计,同时用非接触式射频卡储存个人信息,省时省力,在平时民主测评中以及其他相应场合的应用前景非常广泛。

2018-09-13 09:32:00 5404

5404

多数表决器常见于信号处理。例如,在自动控制中,对三个针对同一事物的信号使用多数表决器进行运算,并按照其中两个一致的结果执行。这样既可以提高信号的可靠性(信号不止一个),又避免信号源错误(出错的信号在表决中被排除)造成不必要的损失。

2019-12-04 07:02:00 2675

2675

表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。表决时,与会的有关人员只要按动各自表决器上“赞成”、“反对”、“弃权”的某一按钮,荧光屏上即显示出表决结果。目前,表决器可分为有线

2019-09-23 07:09:00 2043

2043

表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。表决时,与会的有关人员只要按动各自表决器上“赞成”、“反对”、“弃权”的某一按钮,荧光屏上即显示出表决结果。

2019-09-23 07:05:00 2725

2725

我们例举三人表决器、数字时钟、多终端点歌系统、数字示波器这四个实际的工程项目,手把手带领大家从分析工程、分解工程、到最终实现工程。通过逐个解决工程中的实际问题,来学习原汁原味的FPGA设计。本篇一改

2019-12-06 07:05:00 6384

6384

本文档的主要内容详细介绍的是组合逻辑电路三人表决器的设计资料详细说明。

2019-12-03 08:00:00 12

12 本文档的主要内容详细介绍的是使用单片机实现七人表决器的程序和仿真资料免费下载。

2020-06-22 08:00:00 30

30 本文档的主要内容详细介绍的是8人表决器的电路图免费下载。

2020-06-28 16:46:00 49

49 VHDL电路设计的优化与VHDL描述语句、EDA工具以及可编程器件(PLD)的选用都有着直接的关系。

2020-07-16 08:46:03 2333

2333

protel dxp 三人表决器

2022-06-14 15:00:26 0

0 基于51单片机的表决器例程源代码例程源代码

2023-05-12 15:55:13 1

1 基于51单片机的表决器例程源代码例程源代码

2023-05-18 09:54:43 0

0

电子发烧友App

电子发烧友App

评论