软件开发者应该明白许多参数都会影响接口的性能。即使对IP规范以及SOC设计团队开发的特定配置进行了最为谨慎的研究,也无法保证软件开发者能够按照支持实际IP模块的方式,对IP进行编程。在最优情况下,这些故障可以在软件开发阶段检测出来。在最坏情况下,这些故障可能在SOC实际使用过程中出现。

软件开发者还需要一份关于PHY的陈述,以便与其他设备验证互操作性和性能。关于高级工艺节点日益严重的问题,是半导体公司用于构建控制器与PHY完整原型的独立PHY芯片越来越少。设计人员必须依赖他们的IP供应商为软件团队提供充足的PHY卡。在很多情况下,IP提供商只根据特定客户的要求通过特定方式,提供用于新PHY IP验证实现与特性的PHY卡。获得PHY(作为IP原型套件中标准部件)是一个获得完整原型解决方案的可靠方法。

为了简化流程,虽然硬件团队改进了配置设定,软件团队可以使用DesignWare IP原型套件或者DesignWare IP虚拟开发工具包(VDK)查看软件栈(图6)。软件开发者可以使用这两种工具通过使用相关参考软件开发、调试、优化IP驱动软件。

DesignWare IP原型套件不仅可以处理驱动软件的功能行为,还可以与连接到PHY子卡的外部设备共同验证软件性能。由于硬件团队可以为HAPS-DX系统(IP原型FPGA系统)提供烧录文件,尽早确定目标有很多益处,如果新的硬件就绪,软件团队可以再次尝试新的硬件配置。即使团队位于远程,这种互动方法仍然可行。由于DesignWare IP原型套件价格可以接受,并且可以做到开箱即可使用,可以轻松适用于SOC与软件开发团队。DesignWare IP原型套件首次组装后,软件开发者可以在他们的主机上使用最优开发环境,或者在ARC软件开发平台上编辑软件。将新烧录文件下载到HAPS-DX板上后,这个过程十分迅速,并且每天可以进行数百个软件的调试。

DesignWare IP虚拟开发工具包(VDK)提供了一种模拟模型(虚拟原型),可以使用ARMv8 Cortex big.LITTLE处理系统(四核Cortex-A57及四核Cortex-A53处理器)呈现ARMv8基本参考模板。DesignWare 控制器 IP模型将与参考模板进行整合。每个模型都可以根据软件开发者相关的设置进行配置。经过配置步骤后,软件开发者可以使用他们喜欢的软件调试器。除了标准调试器功能,VDK还可以详细查看软件或硬件的活动。软件团队还可以将完成的软件栈发送给硬件团队,以便其进行下一次性能迭代。这种并行的硬件设计和软件开发过程通常还被称为"左移"。以IP为中心的SDK可以使设计人员,将软件开发任务分解为一系列独立、相互隔离的任务,这就不需要进行大规模的组织变动或大规模投资。唯一的投资就是添加Synopsys IP SDK,软件团队无需进行其他投资或者学习。

第4步:将IP整合到SOC中

从宏观角度来看SOC设计问题,半导体企业硬件方面的问题主要包括:设计自有的差异化IP模块、获得高质量第三方IP、按照SOC优化法进行配置、将所有模块整合到时钟、电压供应商的SOC基础模块中、芯片缓冲存储器或寄存器、测试电路。SOC设计团队将确定半导体特定实施细节并制定关于如何整合IP的要求。IP具有泛型接口,如果不是在SOC基础设施中加入额外粘合逻辑无法匹配。对于许多IP供应商而言,这项工作是由SOC设计团队负责的繁琐任务。

对IP供应商期待更多(帮助)有利于设计人员解决这些问题。首先,DesignWare IP原型套件提供了完整的参考设计。根据该设计,半导体可以执行相应的粘合逻辑。他们甚至可以复制(相关方)提供的RTL源代码并以此为起点作出更多工作。

对于小型SOC设计组织而言,这是一种使用IP提供者的知识、通过支持工程师或IP开发者获得相 关见解的高效方法。

对于项目复杂且截止时间较紧的大型组织而言,IP原型套件还不够。他们需要更多的支持,并且需要大幅度降低内部费用:他们需要定制化的接口IP子系统。接口IP子系统使得设计人员可以充分利用IP提供者关于协议与标准的知识和见解,将这些知识和见解与他们自己的半导体知识和执行问题相结合,并提供综合性解决方案。IP可交付成果与半导体需求的整合应该通过节省成本、半定制方法完成。由于这个过程可以用于多个客户,每个客户可以享用来自其他项目的IP提供商经验,将IP重复利用范式用于子系统。IP提供者在上述整合中需要提供的要求包括:控制器与PHY的整合、多协议与常见PHY的整合、子系统(包括软件栈)的完成。(例子:感应器子系统)

第5步:将驱动和固件整合到SOC软件栈中

最后,还需要进行软件开发工作。即使对于驱动而言,多数工作可以通过DesignWare IP原型套件或者IP虚拟开发工 具包进行分解和辅助,软件开发团队的终极目标是完成整个软件栈。软件团队一般都从在上一个硅片上运行的可用软件栈开始,并且尝试使用先前的基板进行一些开发。但是由于半导体的重大变化,他们无法走的很远,因此,如果他们希望撼动整个设计圈,他们需要一个涉及SOC所有相关部件的硅实现前目标。

这项工作所需的投资和努力远远大于简单的IP SDK,但是对于软件开发团队是一个好消息的是:新思科技的IP SDKs实际上是一个可以获得整个SOC目标的缩小版。小型团队将会欣喜的发现DesignWare IP原型套件可以作为垫脚石,帮助他们获得更多的SOC部件。4M的门容量对于低于500K的控制器尺寸可以充分满足需要,为相同的原型系统添加更多部件所需的空间也预留充足。

随着规模不断扩大,原型团队可以首先使用HAPS-70原型系统并与像卫星系统一样扩展连接DesignWare IP原型套件,这样可以保留已经完成且已验证的部分、可以快速切换到SOC其他未验证部分进行工作(图7)。

对于使用虚拟原型方法的团队而言,DesignWare IP VDK内的模型是Virtualizer™虚拟原型工具中可用模型的完整打包版。这类团队可以使用Virtualizer™中相同的参考模型和配置,与事务级模型(TLM)库(涵盖最常用的商业IP)中的其他特定SOC模型一起进行扩展,并使用Virtualizer事务级模型(TLM)创建工具为独特的内部IP创建模型。

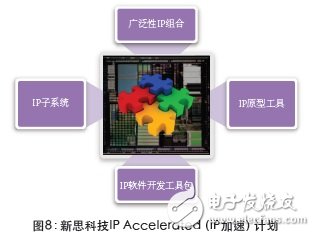

IP Accelerated(IP加速)

IP Accelerated(IP加速)是新思科技(作为接口IP的头号提供商)为了推进IP供应商范例启动的多年计划。新思科技IP Accelerated(IP加速)计划(图8)促进了新思科技已经建立的广泛的,经过硅验证DesignWare IP组合,该组合包括新型DesignWare IP原型套件、DesignWare IP虚拟开发工具包、IP子系统,这可以加快确定原型、软件开发,并加快将IP整合到SOC体中。

对于硬件工程师而言,IP原型套件可以提供经过验证的IP配置,并且该配置可以轻松修改以便为目标性应用进行优化设计。软件开发者可以使用IP虚拟开发工具包或者IP原型套件用于软件的前期开发、调试、测试。

概述与展望

半导体行业正在根据市场需求的变化进行一次自然进化。虽然客户向半导体行业提出了很多新的要求,IP提供者不得不满足这些不断增加的要求。IP Accelerated(IP加速)计划有利于应对这些挑战。我们需要尽量在满足IP用户最大程度上的自我发展与向关注核心竞争力的组织提供专门定制化服务的行为之间寻求平衡。

参考

[1]系统IC业务成功的要素以及对商业模式产生的影响,IBS2012年第4季度报告

[2]2013年新思科技全球用户调查

[3]全球系统IC行业服务报告 - 将半导体行业内的软件货币化的方法,IBS第23卷第4号,2014年4月

电子发烧友App

电子发烧友App

评论